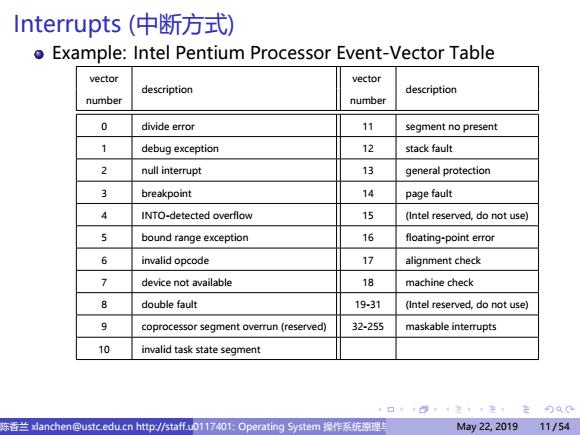

Interrupts(中断方式) o Example:Intel Pentium Processor Event-Vector Table vector vector description description number number 0 divide error 11 segment no present 1 debug exception 12 stack fault 2 null interrupt 13 general protection 3 breakpoint 14 page fault 4 INTO-detected overflow 15 (Intel reserved,do not use) 5 bound range exception 16 floating-point error 6 invalid opcode 17 alignment check 7 device not available 18 machine check 8 double fault 19-31 (Intel reserved,do not use) 9 coprocessor segment overrun (reserved) 32-255 maskable interrupts 10 invalid task state segment 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 May22,201911/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Interrupts (中断方式) Example: Intel Pentium Processor Event-Vector Table vector description vector description number number 0 divide error 11 segment no present 1 debug exception 12 stack fault 2 null interrupt 13 general protection 3 breakpoint 14 page fault 4 INTO-detected overflow 15 (Intel reserved, do not use) 5 bound range exception 16 floating-point error 6 invalid opcode 17 alignment check 7 device not available 18 machine check 8 double fault 19-31 (Intel reserved, do not use) 9 coprocessor segment overrun (reserved) 32-255 maskable interrupts 10 invalid task state segment 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 11 / 54

Outline I/O Hardware and I/O control methods Polling(轮询方式 o Interrupts(中断方式 ●Direct Memory Access(DMA方式) o 1/O hardware summary 口18,走卡11月00 陈话兰xlanchen@ustc.edu:cn http:/staff.uO11740i.Operating System操作系统原理斐 May22,201912/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Outline 1 I/O Hardware and I/O control methods Polling (轮询方式) Interrupts (中断方式) Direct Memory Access (DMA方式) I/O hardware summary 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 12 / 54

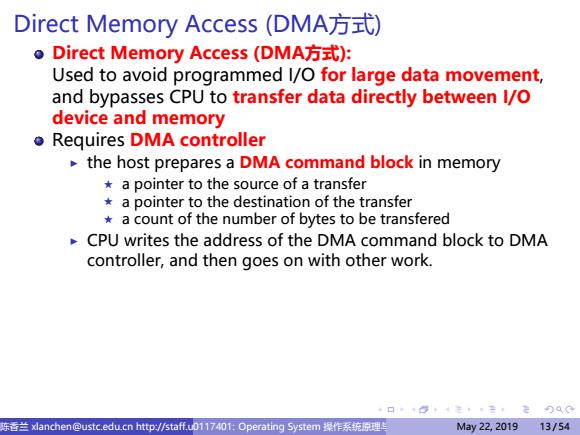

Direct Memory Access(DMA方式) o Direct Memory Acces:5(DMA方式): Used to avoid programmed I/O for large data movement, and bypasses CPU to transfer data directly between I/O device and memory Requires DMA controller the host prepares a DMA command block in memory a pointer to the source of a transfer a pointer to the destination of the transfer a count of the number of bytes to be transfered CPU writes the address of the DMA command block to DMA controller,and then goes on with other work. 口⊙生年12月00 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 May22,201913/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Direct Memory Access (DMA方式) Direct Memory Access (DMA方式): Used to avoid programmed I/O for large data movement, and bypasses CPU to transfer data directly between I/O device and memory Requires DMA controller ▶ the host prepares a DMA command block in memory ⋆ a pointer to the source of a transfer ⋆ a pointer to the destination of the transfer ⋆ a count of the number of bytes to be transfered ▶ CPU writes the address of the DMA command block to DMA controller, and then goes on with other work. 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 13 / 54

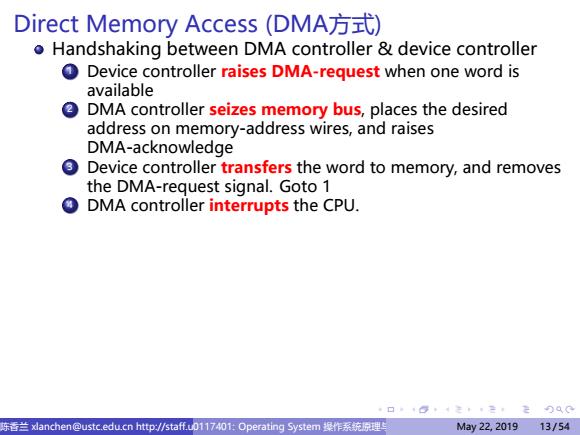

Direct Memory Access(DMA方式) Handshaking between DMA controller device controller Device controller raises DMA-request when one word is available DMA controller seizes memory bus,places the desired address on memory-address wires,and raises DMA-acknowledge Device controller transfers the word to memory,and removes the DMA-request signal.Goto 1 DMA controller interrupts the CPU 东香兰xlanchen@ustc,edu.cn http:/staff..u011740i:Operating System操作系统原理 May22,201913/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Direct Memory Access (DMA方式) Handshaking between DMA controller & device controller 1 Device controller raises DMA-request when one word is available 2 DMA controller seizes memory bus, places the desired address on memory-address wires, and raises DMA-acknowledge 3 Device controller transfers the word to memory, and removes the DMA-request signal. Goto 1 4 DMA controller interrupts the CPU. 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 13 / 54

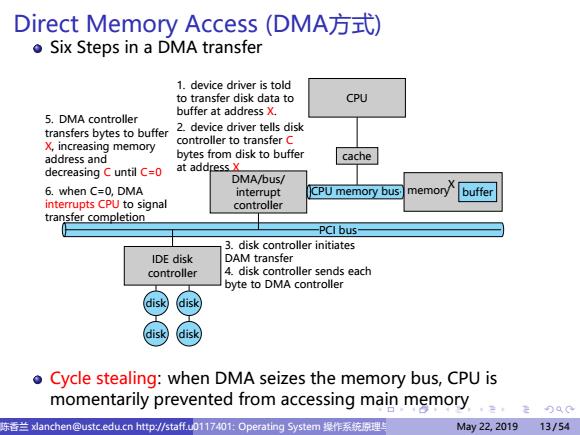

Direct Memory Access(DMA方式) o Six Steps in a DMA transfer 1.device driver is told to transfer disk data to CPU 5.DMA controller buffer at address X. transfers bytes to buffer 2.device driver tells disk X,increasing memory controller to transfer C address and bytes from disk to buffer cache decreasing C until C=0 at address x DMA/bus/ 6.when C=0,DMA interrupt CPU memory bus] memory buffer interrupts CPU to signal controller transfer completion PCI bus 3.disk controller initiates IDE disk DAM transfer controller 4.disk controller sends each byte to DMA controller isk Cycle stealing:when DMA seizes the memory bus,CPU is momentarily prevented from accessing main memory 东香兰xlanchen@ustc.edu.cn http:/作taf仟.u011740i:Operating System操作系统原理 May22,201913/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Direct Memory Access (DMA方式) Six Steps in a DMA transfer PCI bus DMA/bus/ interrupt controller CPU memory bus memory cache CPU buffer X IDE disk controller disk disk disk disk 1. device driver is told to transfer disk data to buffer at address X. 2. device driver tells disk controller to transfer C bytes from disk to buffer at address X 5. DMA controller transfers bytes to buffer X, increasing memory address and decreasing C until C=0 6. when C=0, DMA interrupts CPU to signal transfer completion 3. disk controller initiates DAM transfer 4. disk controller sends each byte to DMA controller Cycle stealing: when DMA seizes the memory bus, CPU is momentarily prevented from accessing main memory 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 13 / 54