光电信息技术实验一一光电数字电路 四、实验注意事项: 1、正确选择集成电路的型号,在集成电路的管脚图中,只有在管脚标“VCC”接电源+5V 管脚标“GD”接电源“地”后,集成电路才能正常工作(千万不可接反,否则将毁坏集 成电路)。门电路的输入端接入高电平(逻辑1态)或低电平(逻辑0态),可由实验箱中 逻辑电平开关K(16个)提供,门电路的输出端可接逻辑电平指示灯L(即16个发光 极管),由L灯的亮或灭来判断输出是高、低电平。(集成电路的输出端管脚不能与逻辑开 关(K)相接,更不能直接接在电源上,否则集成电路会损坏。) 2、用数字表逻辑挡检测TTL门电路的好坏:先将集成电路电源管脚“VCC”和“GND” 接通电源,其他管脚悬空,数字表的黑表笔接电源“地”上,红表笔测门电路的输入端, 数字表逻辑显示应为1态,如显示为0态则说明TTL门电路输入端内部击穿,门电路坏了, 此门电路不能再使用:红表笔测门电路的输出端,输出应符合逻辑门的逻辑关系。例:与 非门(74LS00),两输入端悬空都为逻辑1,输出应符合逻辑与非的关系,测量应为逻辑0 态,如果逻辑关系不对,可判断门电路坏了。 3、用数字表测试时应注意表笔必须与被测门电路的引脚直接相接触,以免面包板接触不 良而造成错误判断。 4、TTL门电路输入负载特性:当门电路需要在输入端与地之间接入电阻R时,因为有输 入电流流过,会使输入低电平Ui提高,从而削弱了电路的抗干扰能力,当R增大到某 值时U会变为高电平,从而使逻辑状态发生改变。 五、实验内容和实验步骤: TTL与非门的参数的测试(74LS00) (1)空载导通功耗Pon 空载导通功耗Po的测试电路如图2-2所示。按图接线,合上K1和K2,再合上电源 开关,读出电流值CCL和电压值VCC,记入表2-2。 (2)空载截止功耗Pof 空载截止功耗Pof的测试电路如图2-2所示。按图接线,K1或K2断开,合上电源开 关,读出电流值ICCH和电压值VCC,记入表2-2。 (3)低电平输入电流L 低电平输入电流L的测试电路如图2-3所示。按图接线,读出电流表上显示的电流 值记入表2-2。 (4)输出高电平VOH 输出高电平VOH的测试电路如图2-4所示。按图接线,合上K1,断开K2,接通电 源,读出电压表上显示的电压值记入表2-2。 (5)输出低电平VOL 输出低电平VOL的测试电路如图2-4所示。按图接线,合上K1和K2,接通电源, 杭州电子科技大学理学院物理实险教学示范中心电信息技术实验室

光电信息技术实验 ――光电数字电路 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 20 四、实验注意事项: 1、正确选择集成电路的型号,在集成电路的管脚图中,只有在管脚标“VCC”接电源+5V, 管脚标“GND”接电源“地”后,集成电路才能正常工作(千万不可接反,否则将毁坏集 成电路)。门电路的输入端接入高电平(逻辑 1 态)或低电平(逻辑 0 态),可由实验箱中 逻辑电平开关 K(16 个)提供,门电路的输出端可接逻辑电平指示灯 L(即 16 个发光二 极管),由 L 灯的亮或灭来判断输出是高、低电平。(集成电路的输出端管脚不能与逻辑开 关(K)相接,更不能直接接在电源上,否则集成电路会损坏。) 2、用数字表逻辑挡检测 TTL 门电路的好坏:先将集成电路电源管脚“VCC”和“GND” 接通电源,其他管脚悬空,数字表的黑表笔接电源“地”上,红表笔测门电路的输入端, 数字表逻辑显示应为 1 态,如显示为 0 态则说明 TTL 门电路输入端内部击穿,门电路坏了, 此门电路不能再使用:红表笔测门电路的输出端,输出应符合逻辑门的逻辑关系。例:与 非门(74LS00),两输入端悬空都为逻辑 1,输出应符合逻辑与非的关系,测量应为逻辑 0 态,如果逻辑关系不对,可判断门电路坏了。 3、用数字表测试时应注意表笔必须与被测门电路的引脚直接相接触,以免面包板接触不 良而造成错误判断。 4、TTL 门电路输入负载特性:当门电路需要在输入端与地之间接入电阻 Ri 时,因为有输 入电流流过 Ri,会使输入低电平 Ui 提高,从而削弱了电路的抗干扰能力,当 Ri 增大到某 一值时 Ui 会变为高电平,从而使逻辑状态发生改变。 五、实验内容和实验步骤: TTL 与非门的参数的测试(74LS00)。 (1)空载导通功耗 Pon 空载导通功耗 Pon 的测试电路如图 2-2 所示。按图接线,合上 K1 和 K2,再合上电源 开关,读出电流值 ICCL 和电压值 VCC,记入表 2-2。 (2)空载截止功耗 Poff 空载截止功耗 Poff 的测试电路如图 2-2 所示。按图接线,K1 或 K2 断开,合上电源开 关,读出电流值 ICCH 和电压值 VCC,记入表 2-2。 (3)低电平输入电流 IIL 低电平输入电流 IIL 的测试电路如图 2-3 所示。按图接线,读出电流表上显示的电流 值记入表 2-2。 (4)输出高电平 VOH 输出高电平 VOH 的测试电路如图 2-4 所示。按图接线,合上 K1,断开 K2,接通电 源,读出电压表上显示的电压值记入表 2-2。 (5)输出低电平 VOL 输出低电平 VOL 的测试电路如图 2-4 所示。按图接线,合上 K1 和 K2,接通电源

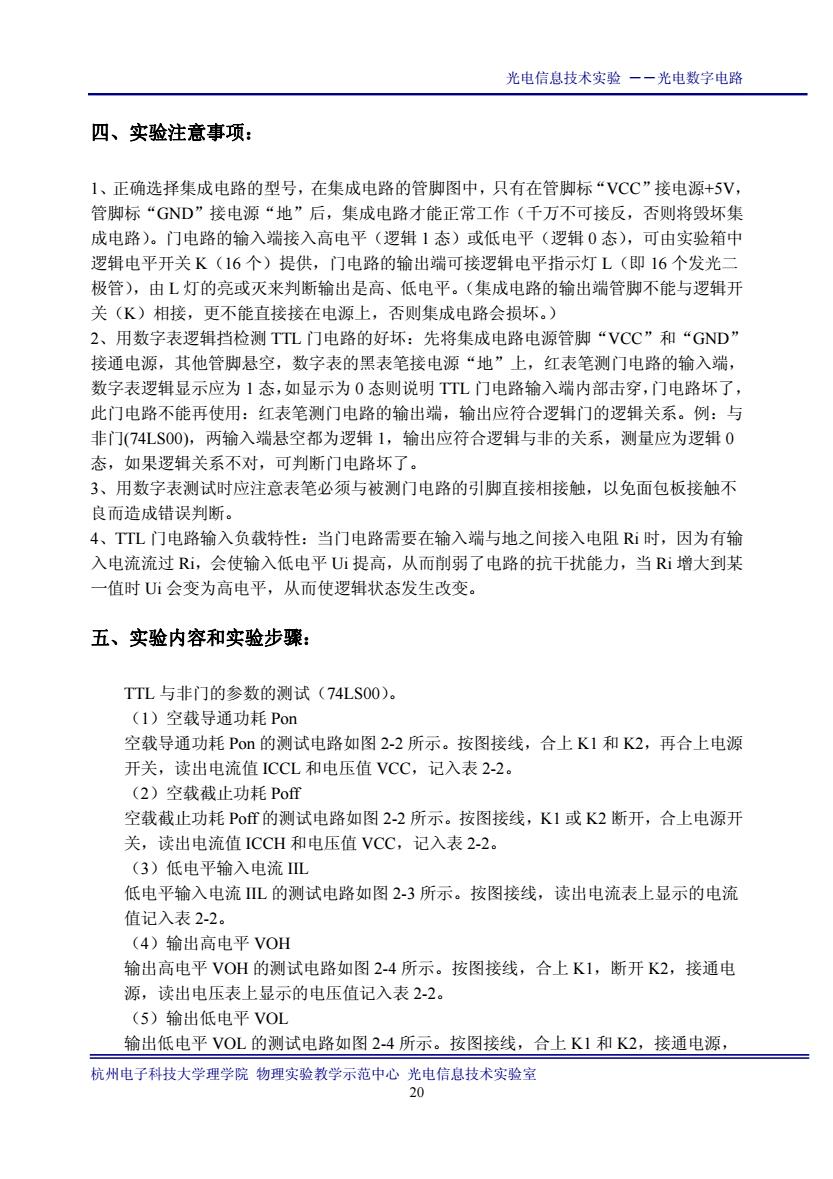

光电信息技术实验一一光电数字电路 读出电压表上显示的电压值记入表2-2。 (6)平均传输延迟时间tpd 平均传输延迟时间pd的测试电路如图2-14所示。按图接线,3个与非门组成环形抹 荡器,从示波器中读出振荡周期T,记入表2-2,则平均传输延迟时间pd=T/6。 97DD=57 CD4001 6≥2 YA 示波 图2-1474LS00平均传输延迟时间pd的测试电路 (7)扇出系数NO 扇出系数NO的测试电路如图2-7所示。按图接线,1脚和2脚悬空,接通电源,调 节电位器Rw,使电压表的值为VOL=0.4V,读出此时的电流表值1OL,记入表2-2, 则扇出系数NO=OL/IL 表2-2TTL器件电参数的测试 测量值 表2-3TTL器件电压传输特性 74LS00 序号V,(V)V(V) 电压传输特性曲线 5 6 7 8 10 (8)电压传输特性曲线 电压传输特性的测试电路如图2-6所示。按图接线,电阻R插入实验箱电阻插孔 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

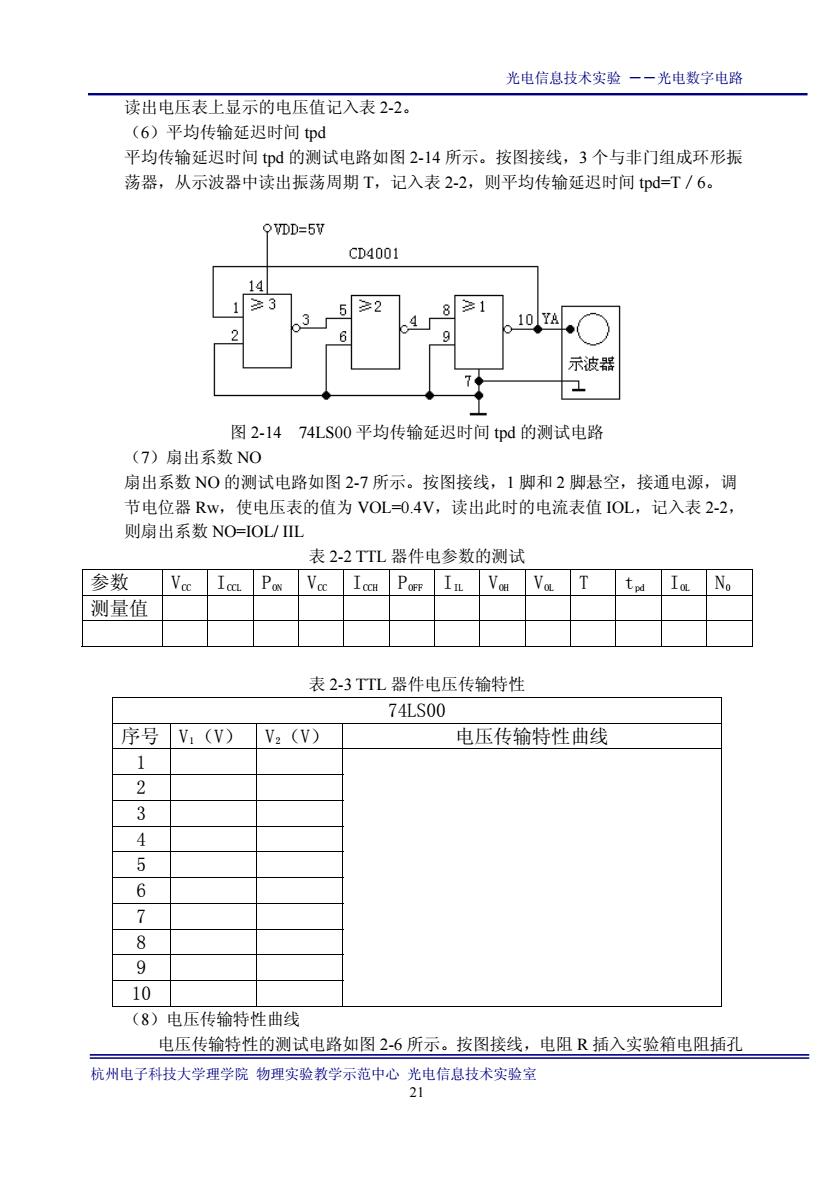

光电信息技术实验 ――光电数字电路 读出电压表上显示的电压值记入表 2-2。 (6)平均传输延迟时间 tpd 平均传输延迟时间 tpd 的测试电路如图 2-14 所示。按图接线,3 个与非门组成环形振 荡器,从示波器中读出振荡周期 T,记入表 2-2,则平均传输延迟时间 tpd=T/6。 图 2-14 74LS00 平均传输延迟时间 tpd 的测试电路 (7)扇出系数 NO 扇出系数 NO 的测试电路如图 2-7 所示。按图接线,1 脚和 2 脚悬空,接通电源,调 节电位器 Rw,使电压表的值为 VOL=0.4V,读出此时的电流表值 IOL,记入表 2-2, 则扇出系数 NO=IOL/ IIL 表 2-2 TTL 器件电参数的测试 参数 VCC ICCL PON VCC ICCH POFF IIL VOH VOL T tpd IOL N0 测量值 表 2-3 TTL 器件电压传输特性 74LS00 序号 V1(V) V2(V) 电压传输特性曲线 1 2 3 4 5 6 7 8 9 10 (8)电压传输特性曲线 电压传输特性的测试电路如图 2-6 所示。按图接线,电阻 R 插入实验箱电阻插孔 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 21

光电信息技术实验一一光电数字电路 中,K2拨到高电平,旋转电位器Rw,使V1,逐渐增大,同时读出V1和V2值,其 中V1值为输入电压,V2为输出电压。将V1和V2记入表2-3中,并绘出V1-V2的 曲线,即由压传输特性曲线。 2、三态门应用 (1)选用与非门(74LS00)和三态门(74LS125),测试接线图如图2-15所示。 (2)A端输入1Hz方波信号,用指示灯观察输出端F1、F2,并将结果填入表2-4中。 表24三态门功能表 B 控制 输入 输出 EN,=0 A F= EN1=1 A F。= EN2=0 A F= EN2=0 A F2= (3)将图2-15中的F1和F2端用导线连接起来实现总线结构,从而实现一根信号线 分时传送多组数据。用实验方法验证。 (输入IH2方波) F1(L1) CC(+57) EN 47K F2(L2) EN2 EN (K1)A -F(L1) (K2)B- B (K1) 图2-15 74LS125测试线路图 图216集电极开路门测试图 表2-50C门线与真值表 输入 输出 0 0 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

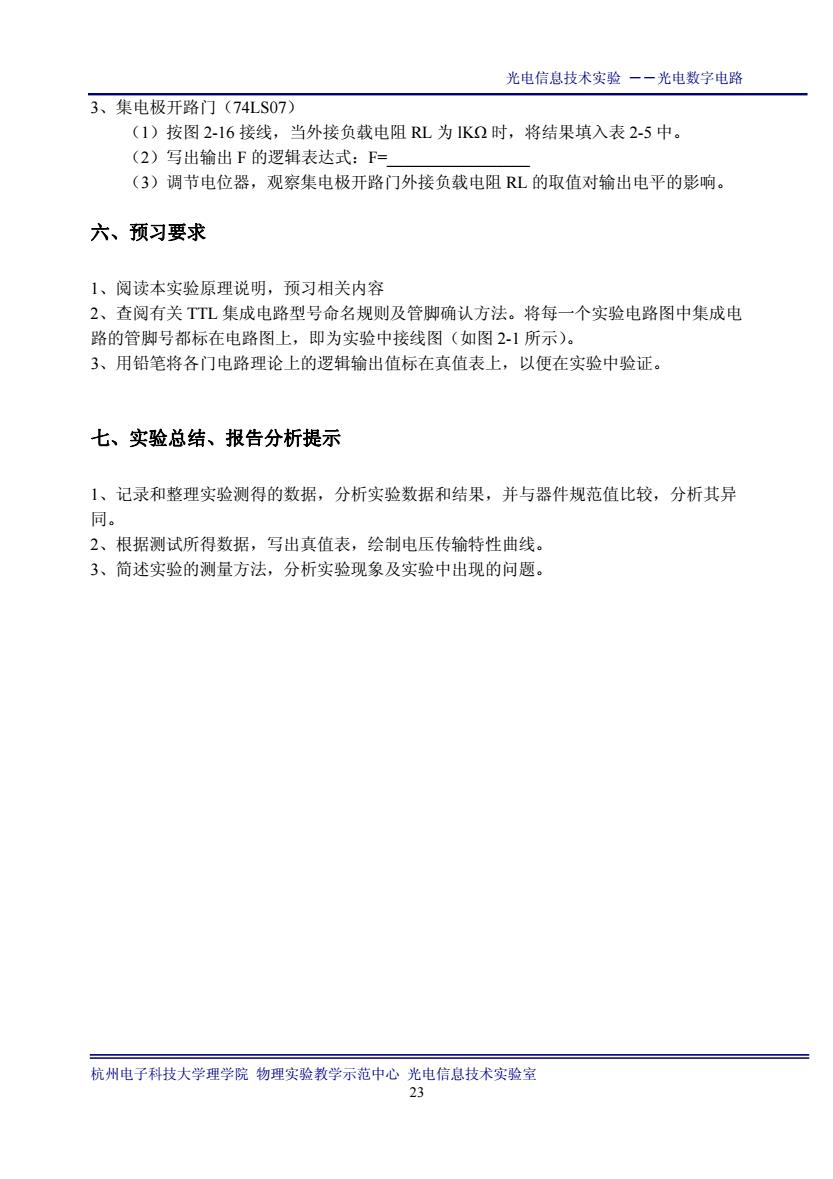

光电信息技术实验 ――光电数字电路 中,K2 拨到高电平,旋转电位器 Rw,使 V1,逐渐增大,同时读出 V1 和 V2 值,其 中 V1 值为输入电压,V2 为输出电压。将 V1 和 V2 记入表 2-3 中,并绘出 V1- V2 的 曲线,即电压传输特性曲线。 2、三态门应用 (1)选用与非门(74LS00)和三态门(74LSl25),测试接线图如图 2-15 所示。 (2)A 端输入 1Hz 方波信号,用指示灯观察输出端 F1、F2,并将结果填入表 2-4 中。 表 2-4 三态门功能表 B 控制 输入 输出 EN1=0 A F1= 1 EN1=1 A F2= EN2=0 A F1= 0 EN2=0 A F2= (3)将图 2-15 中的 F1 和 F2 端用导线连接起来实现总线结构,从而实现一根信号线 分时传送多组数据。用实验方法验证。 图 2-15 74LS125 测试线路图 图 2-16 集电极开路门测试图 表 2-5 OC 门线与真值表 输入 输出 A B F 0 0 0 1 1 0 1 1 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 22

光电信息技术实验一一光电数字电路 3、集电极开路门(74LS07) (1)按图2-16接线,当外接负载电阻L为KΩ时,将结果填入表2-5中。 (2)写出输出F的逻辑表达式:F= (3)调节电位器,观察集电极开路门外接负载电阻L的取值对输出电平的影响。 六、预习要求 1、阅读本实验原理说明,预习相关内容 2、查阅有关TTL集成电路型号命名规则及管脚确认方法。将每一个实验电路图中集成电 路的管脚号都标在电路图上,即为实验中接线图(如图2-1所示)。 3、用铅笔将各门电路理论上的逻辑输出值标在真值表上,以便在实验中验证。 七、实验总结、报告分析提示 1、记录和整理实验测得的数据,分析实验数据和结果,并与器件规范值比较,分析其异 同。 2、根据测试所得数据,写出真值表,绘制电压传输特性曲线。 3、简述实验的测量方法,分析实验现象及实验中出现的问题。 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室 2

光电信息技术实验 ――光电数字电路 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 23 3、集电极开路门(74LS07) (1)按图 2-16 接线,当外接负载电阻 RL 为 lKΩ 时,将结果填入表 2-5 中。 (2)写出输出 F 的逻辑表达式:F=_ (3)调节电位器,观察集电极开路门外接负载电阻 RL 的取值对输出电平的影响。 六、预习要求 1、阅读本实验原理说明,预习相关内容 2、查阅有关 TTL 集成电路型号命名规则及管脚确认方法。将每一个实验电路图中集成电 路的管脚号都标在电路图上,即为实验中接线图(如图 2-1 所示)。 3、用铅笔将各门电路理论上的逻辑输出值标在真值表上,以便在实验中验证。 七、实验总结、报告分析提示 1、记录和整理实验测得的数据,分析实验数据和结果,并与器件规范值比较,分析其异 同。 2、根据测试所得数据,写出真值表,绘制电压传输特性曲线。 3、简述实验的测量方法,分析实验现象及实验中出现的问题

光电信息技术实验一一光电数字电路 实验三CMOS门电路测试 一、实验目的 1、掌握CMOS门电路的功能测试方法。 2、学会CMOS门电路外特性的测试方法。 3、比较CMOS门和TTL门的特点。 二、实验原理 CMOS数字集成电路是互补对称金属氧化物半导体集成电路。其基本电路是由增强型 PMOS管和NMOS管按互补对称形式连接而成。CMOS集成电路的主要优点是: 1、功耗低,其静态工作电流在10-9A数量级,是数字集成电路中最低的,而TTL器件则 高得多。 2、输入阻抗高,通常大于10100,远高于TTL的器件的输入阻抗。 3、接近理想的电压传输特性,输出高电平可达电源电压的99.9%以上,低电平可达电源电 压的0.1%以下,因此输出逻辑电平的摆幅很大,噪声容限很高。 4、电源电压变化范围宽,使用范围为+3~+18V之间 5、由于有很高的输入阻抗,要求的驱动电流很小,约0.1A,输出电流在+5V电源下约为 5004,远小于TTL电路。如以此电流米驱动同类门电路,其扇出系数将非常大。在一般 低频时,无需考虑扇出系数,但在高频时,后级门的输入电容将成为主要负载,使其扇出 能力下降,所以在较高频率工作时,CMOS电路的扇出系数一般取10~20, 因而CMOS集成电路在数字电路中得到广泛的应用,本实验所使用的CMOS集成电路4000 系列芯片(如CD4001)的电源电压。 CMOS门电路的逻辑高、低电平取值和TTL门电路略有不同,通常是高电平为VDD(CMOS 门电路的电源电压值),低电平为0,故CMOS门电路的电源电压取值不同,其输出高电 平也不一样。 CMOS门电路的电压传输特性是指CMOS门电路的输出电压随输入电压的变化而变化的 特性,可在V~V%平面中用曲线来表示,称为传输特性曲线。 CMOS门电路的逻辑功能和平均传输延迟时间p风与TTL门电路相同,可参照实验二的实 验原理部分。 CMOS电路栅极与衬底之间构成了良好的储能电容,极易感应静电电荷,造成栅极和衬底 击穿,使用时应注意以下几点: 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

光电信息技术实验 ――光电数字电路 实验三 CMOS 门电路测试 一、实验目的 1、掌握 CMOS 门电路的功能测试方法。 2、学会 CMOS 门电路外特性的测试方法。 3、比较 CMOS 门和 TTL 门的特点。 二、实验原理 CMOS 数字集成电路是互补对称金属氧化物半导体集成电路。其基本电路是由增强型 PMOS 管和 NMOS 管按互补对称形式连接而成。CMOS 集成电路的主要优点是: 1、功耗低,其静态工作电流在 10-9A 数量级,是数字集成电路中最低的,而 TTL 器件则 高得多。 2、输入阻抗高,通常大于 1010Ω,远高于 TTL 的器件的输入阻抗。 3、接近理想的电压传输特性,输出高电平可达电源电压的 99.9%以上,低电平可达电源电 压的 0.1%以下,因此输出逻辑电平的摆幅很大,噪声容限很高。 4、电源电压变化范围宽,使用范围为+3~+18V 之间。 5、由于有很高的输入阻抗,要求的驱动电流很小,约 0.1μA,输出电流在+5V 电源下约为 500μA,远小于 TTL 电路。如以此电流来驱动同类门电路,其扇出系数将非常大。在一般 低频时,无需考虑扇出系数,但在高频时,后级门的输入电容将成为主要负载,使其扇出 能力下降,所以在较高频率工作时,CMOS 电路的扇出系数一般取 10~20。 因而CMOS集成电路在数字电路中得到广泛的应用,本实验所使用的CMOS集成电路4000 系列芯片(如 CD4001)的电源电压。 CMOS 门电路的逻辑高、低电平取值和 TTL 门电路略有不同,通常是高电平为 VDD(CMOS 门电路的电源电压值),低电平为 0,故 CMOS 门电路的电源电压取值不同,其输出高电 平也不一样。 CMOS 门电路的电压传输特性是指 CMOS 门电路的输出电压随输入电压的变化而变化的 特性,可在 Vi~Vo 平面中用曲线来表示,称为传输特性曲线。 CMOS 门电路的逻辑功能和平均传输延迟时间t pd 与 TTL 门电路相同,可参照实验二的实 验原理部分。 CMOS 电路栅极与衬底之间构成了良好的储能电容,极易感应静电电荷,造成栅极和衬底 击穿,使用时应注意以下几点: 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 24