光电信息技术实验一一光电数字电路 (1)烙铁和测量仪器必须良好接地。不使用时,所有引脚必须用导线短路或用金属 材料包装屏蔽。 (2)闲置的输入端不能悬空。由于CMOS电路有很高的输入阻抗,外来的一些于扰 信号很容易在一些悬空的输入端上感应出很高的电压,以至损坏器件。通常是将闲置 的输入端接到VDD或VSS端,或将它们与使用的输入端并联. (3)输出端不允许直接与VDD或VSS连接,否则将导致器件损坏。 (4)禁止在接通电源的情况下装拆器件或电路板。 (5)工作或测试时必须先接通电源,然后加入输入信号:工作或测试结束,必须先 撤去输入信号,再关闭电源。输入信号的幅度应限制在VSS<VI<VDD的范围内。 三、实验仪器及材料 1、双踪示波器 2、元器件 CMOS芯片: CD4001 四2输入或非门 1片 CD4011 四2输入与非门 1片 TTL芯片:74LS00四2输入与非门 1片 电位器 47K 1只 电阻 5K 2只 四、实验内容与步骤 1、CMOS芯片CD4001参数测试(方法与TTL电路相同,参照实验二) CMOS器件的各项参数的含义和测试方法与TTL器件相似,因此测试CMOS器件 态参数时的电路与测试TTL器件静态参数时的电路大体相同,不过要注意CMOS器件和 TTL器件的使用规则各不相同,对各个端脚的处理要注意符合逻辑关系。另外,CMOS器 件的ICCL和ICCH值极小,仅几微安。为了保证输出开路的条件,其输出端所使用的电 压表内阻要足够大,最好用直流数字电压表。 A1- 14 -VDD YI- -B4 Y2- a A2- -Y3 B2- -B3 VSS- 8-A3 图3-1CD4001B集成电路引脚排列图 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

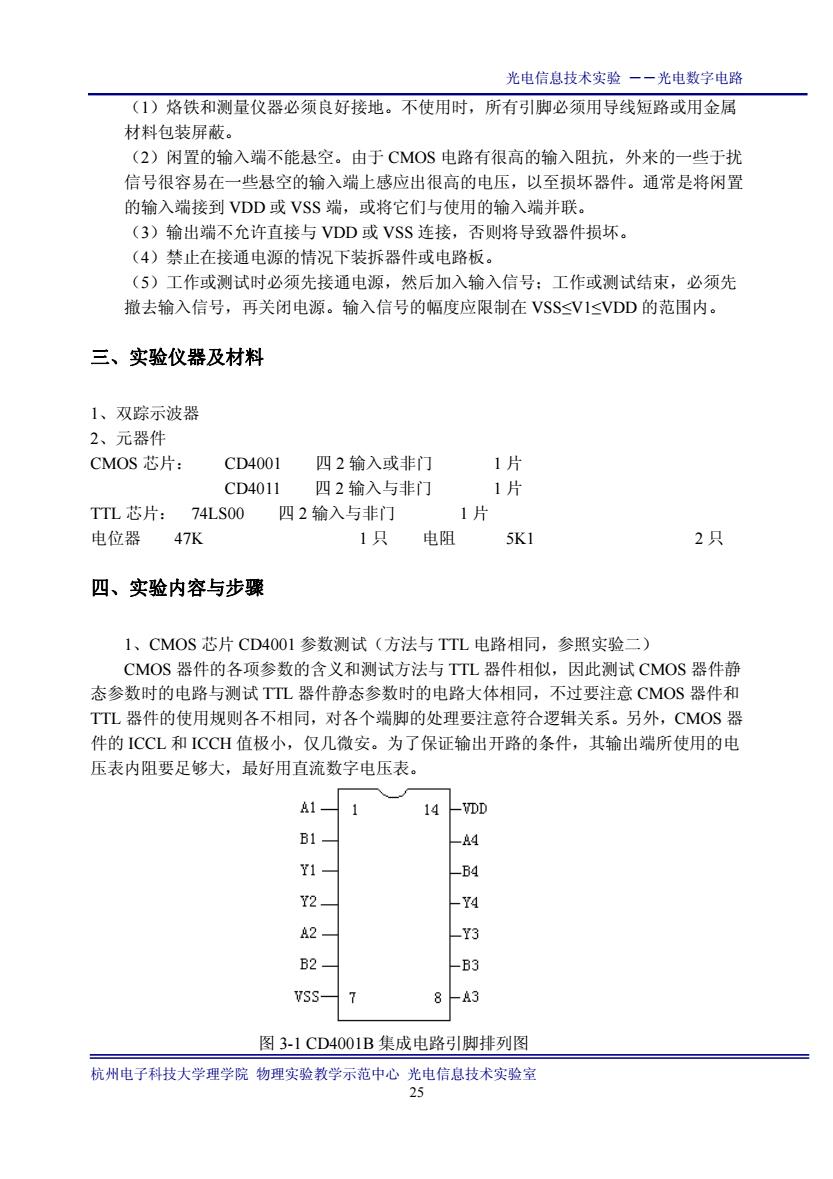

光电信息技术实验 ――光电数字电路 (1)烙铁和测量仪器必须良好接地。不使用时,所有引脚必须用导线短路或用金属 材料包装屏蔽。 (2)闲置的输入端不能悬空。由于 CMOS 电路有很高的输入阻抗,外来的一些于扰 信号很容易在一些悬空的输入端上感应出很高的电压,以至损坏器件。通常是将闲置 的输入端接到 VDD 或 VSS 端,或将它们与使用的输入端并联。 (3)输出端不允许直接与 VDD 或 VSS 连接,否则将导致器件损坏。 (4)禁止在接通电源的情况下装拆器件或电路板。 (5)工作或测试时必须先接通电源,然后加入输入信号;工作或测试结束,必须先 撤去输入信号,再关闭电源。输入信号的幅度应限制在 VSS≤V1≤VDD 的范围内。 三、实验仪器及材料 1、双踪示波器 2、元器件 CMOS 芯片: CD4001 四 2 输入或非门 1 片 CD4011 四 2 输入与非门 1 片 TTL 芯片: 74LS00 四 2 输入与非门 1 片 电位器 47K 1 只 电阻 5K1 2 只 四、实验内容与步骤 1、CMOS 芯片 CD4001 参数测试(方法与 TTL 电路相同,参照实验二) CMOS 器件的各项参数的含义和测试方法与 TTL 器件相似,因此测试 CMOS 器件静 态参数时的电路与测试 TTL 器件静态参数时的电路大体相同,不过要注意 CMOS 器件和 TTL 器件的使用规则各不相同,对各个端脚的处理要注意符合逻辑关系。另外,CMOS 器 件的 ICCL 和 ICCH 值极小,仅几微安。为了保证输出开路的条件,其输出端所使用的电 压表内阻要足够大,最好用直流数字电压表。 图 3-1 CD4001B 集成电路引脚排列图 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 25

光电信息技术实验一一光电数字电路 2、CMOS芯片CD4001功能测试 本实验的电源电压VDD=+5V 在A、B端加不同的逻辑电平,用电压表测出相应的VO值,并将结果列成真值表的 形式。 注意:CMOS门电路的多余输入端不允许悬空。 3、CMOS门电路CD4001电压传输特性测试 按图3-2所示接线。先令VDD=+12V。调节电位器RW的阻值,使V1在+3V~VDD变化, 测出VO随V1变化的特性曲线。 VDD CD4001 21 图3-2CD4001电压传输特性测试的测试电路 表3-1CMOS器件电压传输特性 CD4001 序号V(V)V2(V) 电压传输特性曲线 6 7 9 10 记录有关的实验数据,画成表格形式,如表31。并画出电压传输特性曲线VO-f(V1) 改变VDD值,使其为+5V,重复上述实验内容。 断开电源开关,2脚与7脚断开,1脚和2脚相连。合上电源开关,重复上述调节电 位器Rw的步骤,比较两种情况下电压传输特性曲线的差异。 杭州电子利技大学理学院物理实验教学示范中心光电信息技术实验室

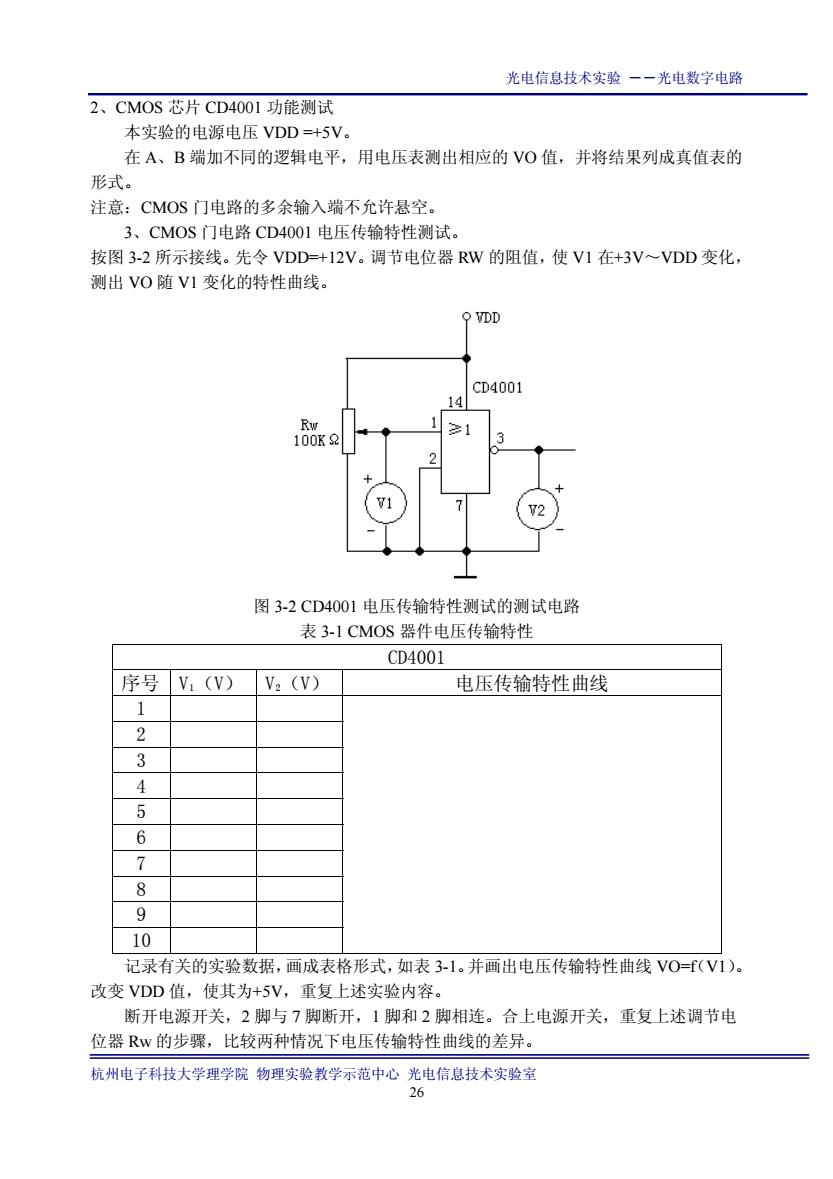

光电信息技术实验 ――光电数字电路 2、CMOS 芯片 CD4001 功能测试 本实验的电源电压 VDD =+5V。 在 A、B 端加不同的逻辑电平,用电压表测出相应的 VO 值,并将结果列成真值表的 形式。 注意:CMOS 门电路的多余输入端不允许悬空。 3、CMOS 门电路 CD4001 电压传输特性测试。 按图 3-2 所示接线。先令 VDD=+12V。调节电位器 RW 的阻值,使 V1 在+3V~VDD 变化, 测出 VO 随 V1 变化的特性曲线。 图 3-2 CD4001 电压传输特性测试的测试电路 表 3-1 CMOS 器件电压传输特性 CD4001 序号 V1(V) V2(V) 电压传输特性曲线 1 2 3 4 5 6 7 8 9 10 记录有关的实验数据,画成表格形式,如表 3-1。并画出电压传输特性曲线 VO=f(V1)。 改变 VDD 值,使其为+5V,重复上述实验内容。 断开电源开关,2 脚与 7 脚断开,1 脚和 2 脚相连。合上电源开关,重复上述调节电 位器 Rw 的步骤,比较两种情况下电压传输特性曲线的差异。 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 26

光电信息技术实验一一光电数字电路 在同一坐标上画出CMOS门取不同的VDD值时所对应的VO=f(V1)曲线。 比较TTL器件与CMOS器件的电压传输出特性曲线。 3、CD4O01平均传输时间TPD的测量。 按图3-3所示电路接线。图中VDD=+5V,CP取自实验仪上的连续脉冲。 CD4001 5.1K 9 □阿四-阿-可 74LS00 图3-3CD4001平均传输时间TPD的测试电路 观察V1和CP的异同,说明芯片74LS00的作用是什么? 用双踪示波器观察并记录VO~V1波形,测出CD4O01芯片的TPD值。 若将图3-3中的CD4001芯片改为CD4011芯片,测出CD4011芯片的pd并和TTL门电 路的pd比较,从中你得到什么结论? 五、思考题 1、CMOS电路多余的输入端在使用时不允许悬空,其理由是什么?试通过实验测定CMOS 门悬空端的电平值,分析所测值是否正确? 2、若将CMOS门CD4O01芯片的A端按下述各种情况连接: A、接+VDD B、接GND C、经1M电阻接地 D、经5002电阻接地 E、经100KQ电阻接+VDD 用电压表测定另一输入端B电压值,你认为各应为多少伏?用实验验证。 3、一般的CMOS门电路能否进行“线与”?为什么?若要将CMOS门的输出进行逻辑与, 你认为采用什么办法? 4、若考虑用一个TTL门直接推动一个CMOS门,或者用一个CMOS门直接推动一个TTL 门,试问能否正常工作?你是怎么考虑的?若有条件,请通过实验验证。 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室 2

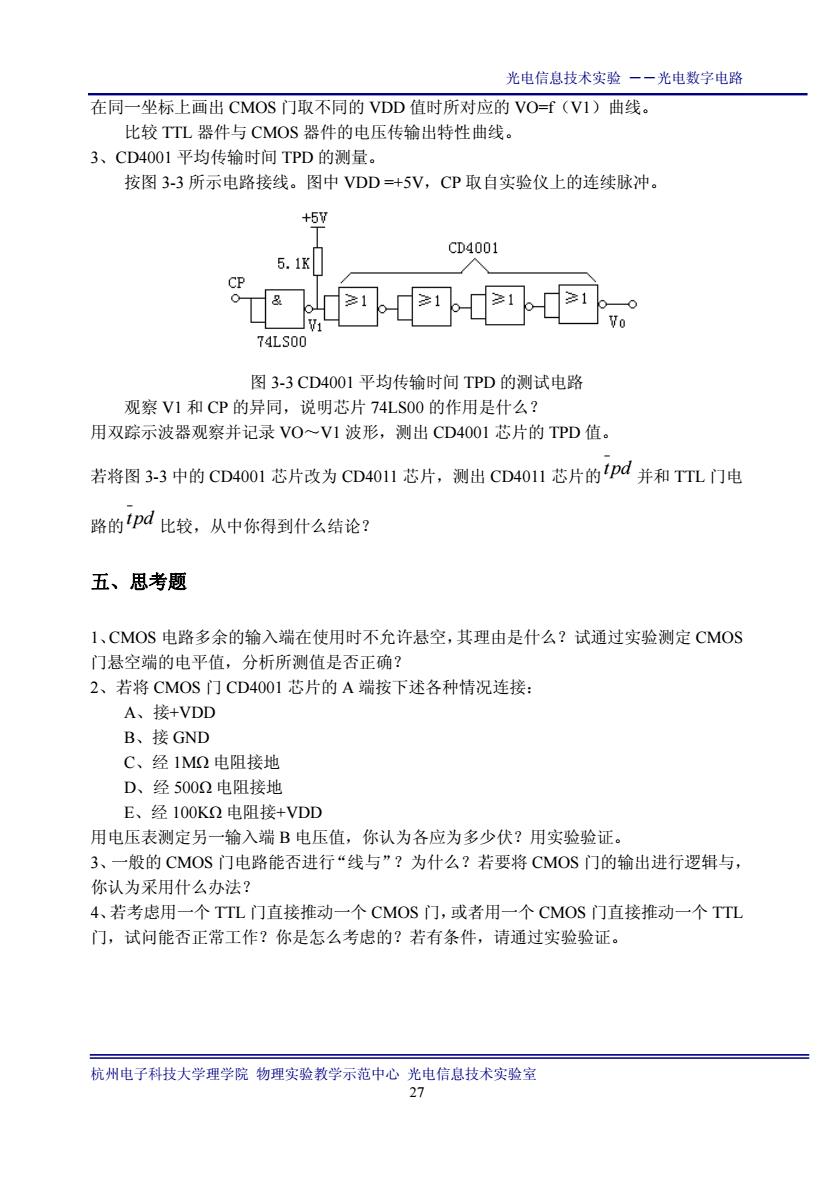

光电信息技术实验 ――光电数字电路 在同一坐标上画出 CMOS 门取不同的 VDD 值时所对应的 VO=f(V1)曲线。 比较 TTL 器件与 CMOS 器件的电压传输出特性曲线。 3、CD4001 平均传输时间 TPD 的测量。 按图 3-3 所示电路接线。图中 VDD =+5V,CP 取自实验仪上的连续脉冲。 图 3-3 CD4001 平均传输时间 TPD 的测试电路 观察 V1 和 CP 的异同,说明芯片 74LS00 的作用是什么? 用双踪示波器观察并记录 VO~V1 波形,测出 CD4001 芯片的 TPD 值。 若将图 3-3 中的 CD4001 芯片改为 CD4011 芯片,测出 CD4011 芯片的 pdt 并和 TTL 门电 路的 pdt 比较,从中你得到什么结论? 五、思考题 1、CMOS 电路多余的输入端在使用时不允许悬空,其理由是什么?试通过实验测定 CMOS 门悬空端的电平值,分析所测值是否正确? 2、若将 CMOS 门 CD4001 芯片的 A 端按下述各种情况连接: A、接+VDD B、接 GND C、经 1MΩ 电阻接地 D、经 500Ω 电阻接地 E、经 100KΩ 电阻接+VDD 用电压表测定另一输入端 B 电压值,你认为各应为多少伏?用实验验证。 3、一般的 CMOS 门电路能否进行“线与”?为什么?若要将 CMOS 门的输出进行逻辑与, 你认为采用什么办法? 4、若考虑用一个 TTL 门直接推动一个 CMOS 门,或者用一个 CMOS 门直接推动一个 TTL 门,试问能否正常工作?你是怎么考虑的?若有条件,请通过实验验证。 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 27

光电信息技术实验一一光电数字电路 实验四门电路逻辑功能及测试 一、实验目的 1、熟悉门电路逻辑功能 2、熟悉数字电路箱及示波器使用方法。 二、实验原理 门电路是开关电路的一种,它具有一个或多个输入端,只有一个输出端,当一个或多 个输入端有信号时其输出才有信号。门电路在满足一定条件时,按一定规律输出信号,起 着开关作用。基本门电路采用与门、或门、非门三种,也可将其组合而构成其它门,如与 非门、或非门等。图41为与非门电路原理图,其基本功能是:在输入信号全为高电平时 输出才为低电平。输出与输入的逻辑关系为:Y=ABCD。平均传输延迟时间pd是衡量门 电路开关速度的参数。它是指输出波形边沿的0.5Vm点相对于输入波形对应边沿的0.5Vm 点的时间延迟。如图4-2所示,门电路的导通延迟时间为pdL,截止延迟时间为pd,则 平均传输延迟时间为: ipd=(tpdL+tpdH) 图43为异或门电路原理图,其基本功能是:当两个输入端相异(即一个为0',另一个 为1')时,输出为1':当两个输入端相同时,输出为‘0'。即:Y=A田B=AB+AB V14 0 t 图41与非门电路原理图 42门电路导通延迟时间与截止延迟时间 杭州电子科技大学理学院物理实验教学示范中心 光电信息技术实验室

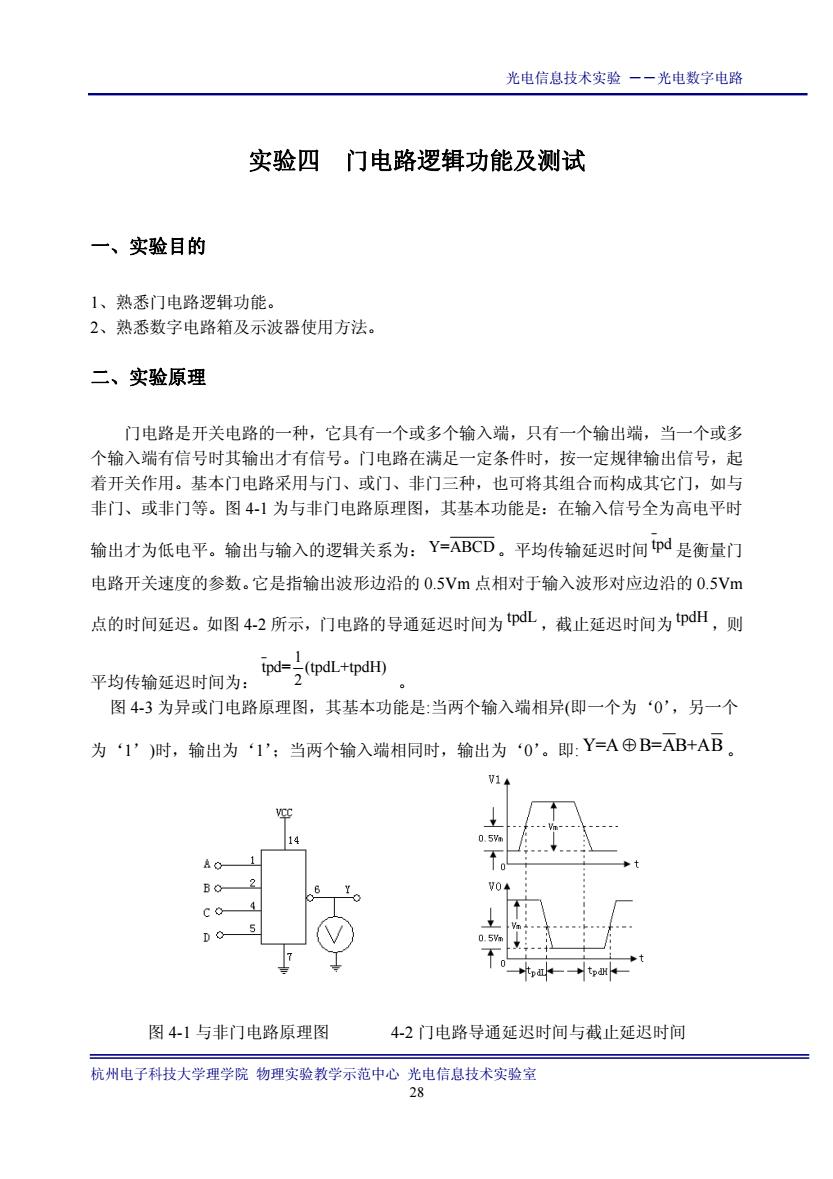

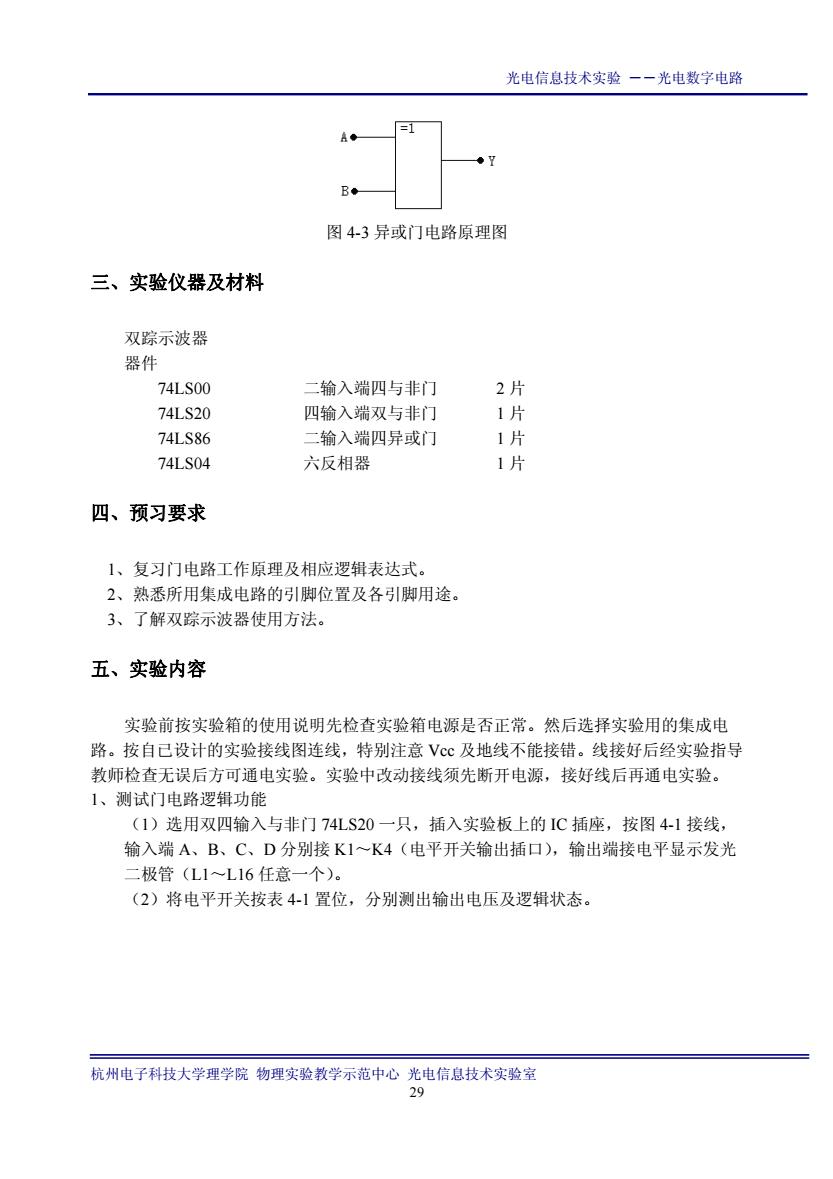

光电信息技术实验 ――光电数字电路 实验四 门电路逻辑功能及测试 一、实验目的 1、熟悉门电路逻辑功能。 2、熟悉数字电路箱及示波器使用方法。 二、实验原理 门电路是开关电路的一种,它具有一个或多个输入端,只有一个输出端,当一个或多 个输入端有信号时其输出才有信号。门电路在满足一定条件时,按一定规律输出信号,起 着开关作用。基本门电路采用与门、或门、非门三种,也可将其组合而构成其它门,如与 非门、或非门等。图 4-1 为与非门电路原理图,其基本功能是:在输入信号全为高电平时 输出才为低电平。输出与输入的逻辑关系为:Y=ABCD 。平均传输延迟时间 tpd 是衡量门 电路开关速度的参数。它是指输出波形边沿的 0.5Vm 点相对于输入波形对应边沿的 0.5Vm 点的时间延迟。如图 4-2 所示,门电路的导通延迟时间为 ,截止延迟时间为 ,则 平均传输延迟时间为: tpdL tpdH 1 tpd= (tpdL+tpdH) 2 。 图 4-3 为异或门电路原理图,其基本功能是:当两个输入端相异(即一个为‘0’,另一个 为‘1’)时,输出为‘1’;当两个输入端相同时,输出为‘0’。即: Y=A B=AB+AB 。 图 4-1 与非门电路原理图 4-2 门电路导通延迟时间与截止延迟时间 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 28

光电信息技术实验一一光电数字电路 1 B◆ 图4-3异或门电路原理图 三、实验仪器及材料 双踪示波器 器件 74LS00 二输入端四与非门 2片 74LS20 四输入端双与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六反相器 1片 四、预习要求 1、复习门电路工作原理及相应逻辑表达式。 2、熟悉所用集成电路的引脚位置及各引脚用途。 3、了解双踪示波器使用方法。 五、实验内容 实验前按实验箱的使用说明先检查实验箱电源是否正常。然后选择实验用的集成电 路。按自已设计的实验接线图连线,特别注意V©c及地线不能接错。线接好后经实验指导 教师检查无误后方可通电实验。实验中改动接线须先断开电源,接好线后再通电实验。 1、测试门电路逻辑功能 (1)选用双四输入与非门74LS20一只,插入实验板上的1C插座,按图41接线, 输入端A、B、C、D分别接K1~K4(电平开关输出插口),输出端接电平显示发光 二极管(L1~L16任意一个)。 (2)将电平开关按表4-1置位,分别测出输出电压及逻辑状态 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

光电信息技术实验 ――光电数字电路 图 4-3 异或门电路原理图 三、实验仪器及材料 双踪示波器 器件 74LS00 二输入端四与非门 2 片 74LS20 四输入端双与非门 1 片 74LS86 二输入端四异或门 1 片 74LS04 六反相器 1 片 四、预习要求 1、复习门电路工作原理及相应逻辑表达式。 2、熟悉所用集成电路的引脚位置及各引脚用途。 3、了解双踪示波器使用方法。 五、实验内容 实验前按实验箱的使用说明先检查实验箱电源是否正常。然后选择实验用的集成电 路。按自已设计的实验接线图连线,特别注意 Vcc 及地线不能接错。线接好后经实验指导 教师检查无误后方可通电实验。实验中改动接线须先断开电源,接好线后再通电实验。 1、测试门电路逻辑功能 (1)选用双四输入与非门 74LS20 一只,插入实验板上的 IC 插座,按图 4-1 接线, 输入端 A、B、C、D 分别接 K1~K4(电平开关输出插口),输出端接电平显示发光 二极管(L1~L16 任意一个)。 (2)将电平开关按表 4-1 置位,分别测出输出电压及逻辑状态。 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 29