光电信息技术实验一一光电数字电路 (3)、输出高电平VOH 输出高电平VOH是指输出不接负载,当有一输入端为低电平时的电路输出电压 值。测试电路如图2-4所示。 (4)、输出低电平VOL: 输出低电平VOL是指所有输入端均接高电平时的输出电压值。测试电路如图2-4 所示。 Vee 图2-4输出高电平VOH和输出低电平VOL的测试电路 (5)、电压传输特性曲线、开门电平on和关门电平6任 电压传输特性曲线如图25所示,是关于输入电压与输出电压(V6)的关系曲 线。使输出电压VO刚刚达到低电平VOL时的最低输入电压称为开门电平Von使输 出电压VO刚刚达到高电平VOH时的最高输入电压Vi称为关门电平VOFF。 电压传输特性侧试电路如图2-6所示。 0()年 00 3.6Y 74LS00 0Von i 3.6Y 图2-5电压传输特性曲线 图2-6电压传输特性测试电路 (6)、扇出系数NO: 电路正常工作时,能带动的同型号门的数目称为扇出系数NO。扇出系数NO的 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

光电信息技术实验 ――光电数字电路 (3)、输出高电平 VOH: 输出高电平 VOH 是指输出不接负载,当有—输入端为低电平时的电路输出电压 值。测试电路如图 2-4 所示。 (4)、输出低电平 VOL: 输出低电平 VOL 是指所有输入端均接高电平时的输出电压值。测试电路如图 2-4 所示。 图 2-4 输出高电平 VOH 和输出低电平 VOL 的测试电路 (5)、电压传输特性曲线、开门电平 Von 和关门电平 Voff: 电压传输特性曲线如图 2-5 所示,是关于输入电压与输出电压(Vi-Vo)的关系曲 线。使输出电压 VO 刚刚达到低电平 VOL 时的最低输入电压称为开门电平 Von 使输 出电压 VO 刚刚达到高电平 VOH 时的最高输入电压 Vi 称为关门电平 VOFF。 电压传输特性测试电路如图 2-6 所示。 图 2-5 电压传输特性曲线 图 2-6 电压传输特性测试电路 (6)、扇出系数 NO: 电路正常工作时,能带动的同型号门的数目称为扇出系数 NO。扇出系数 NO 的 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 15

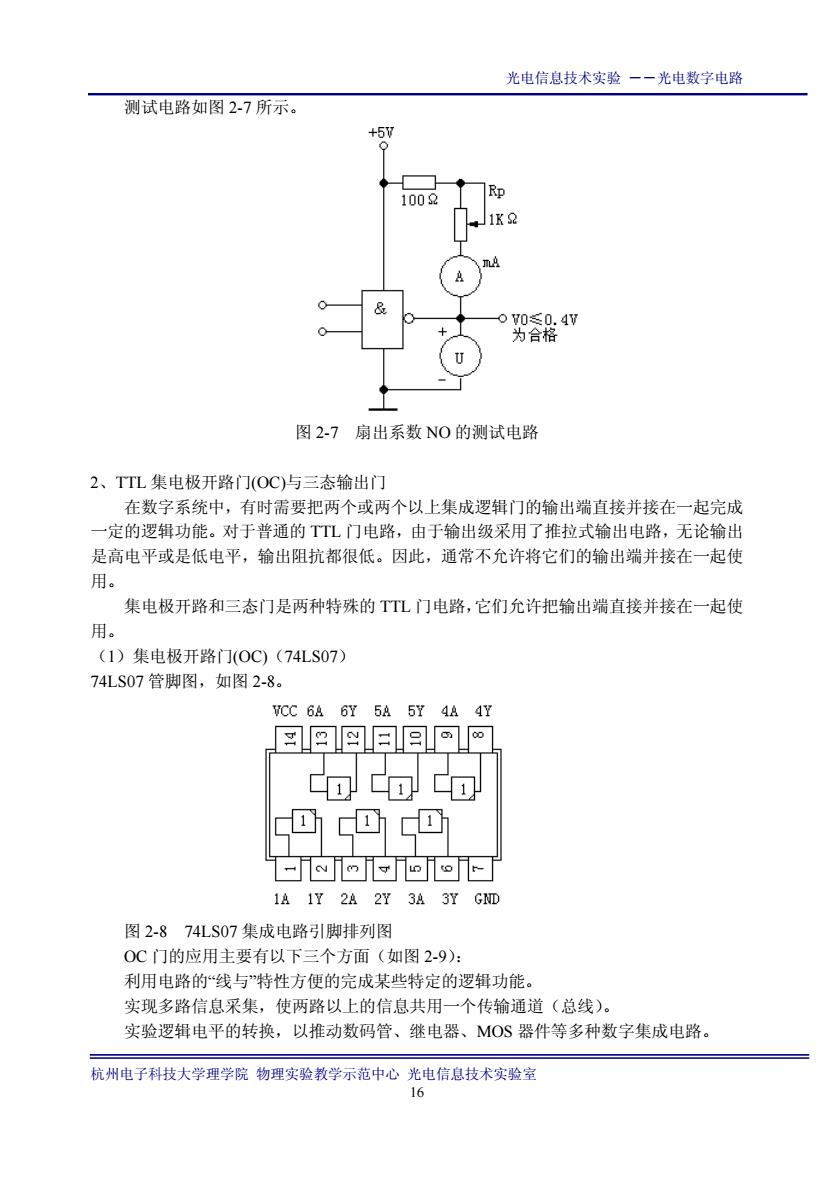

光电信息技术实验一一光电数字电路 测试电路如图2-7所示。 +5w 1002 R 为最 图2-7扇出系数NO的测试电路 2、TTL集电极开路门(OC)与三态输出门 在数字系统中,有时需要把两个或两个以上集成逻辑门的输出端直接并接在一起完成 一定的逻辑功能。对于普通的TTL门电路,由于输出级采用了推拉式输出电路,无论输出 是高电平或是低电平,输出阻抗都很低。因此,通常不允许将它们的输出端并接在一起使 用。 集电极开路和三态门是两种特殊的TTL门电路,它们允许把输出端直接并接在一起使 用。 (1)集电极开路门(OC)(74LS07) 74LS07管脚图,如图2-8。 VCC 6A 6Y 5A 5Y 4A 4Y 阿回曰回回网 cococo co coco -mg回o 1A 1Y 2A 2Y 3A 3Y GND 图2-874LS07集成电路引脚排列图 0C门的应用主要有以下三个方面(如图2-9): 利用电路的“线与”特性方便的完成某些特定的逻辑功能。 实现多路信息采集,使两路以上的信息共用一个传输通道(总线)。 实验逻辑电平的转换,以推动数码管、继电器、MOS器件等多种数字集成电路, 杭州电子利技大学理学院物理实验教学示范中心光电信息技术实验室

光电信息技术实验 ――光电数字电路 测试电路如图 2-7 所示。 图 2-7 扇出系数 NO 的测试电路 2、TTL 集电极开路门(OC)与三态输出门 在数字系统中,有时需要把两个或两个以上集成逻辑门的输出端直接并接在一起完成 一定的逻辑功能。对于普通的 TTL 门电路,由于输出级采用了推拉式输出电路,无论输出 是高电平或是低电平,输出阻抗都很低。因此,通常不允许将它们的输出端并接在一起使 用。 集电极开路和三态门是两种特殊的 TTL 门电路,它们允许把输出端直接并接在一起使 用。 (1)集电极开路门(OC)(74LS07) 74LS07 管脚图,如图 2-8。 图 2-8 74LS07 集成电路引脚排列图 OC 门的应用主要有以下三个方面(如图 2-9): 利用电路的“线与”特性方便的完成某些特定的逻辑功能。 实现多路信息采集,使两路以上的信息共用一个传输通道(总线)。 实验逻辑电平的转换,以推动数码管、继电器、MOS 器件等多种数字集成电路。 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 16

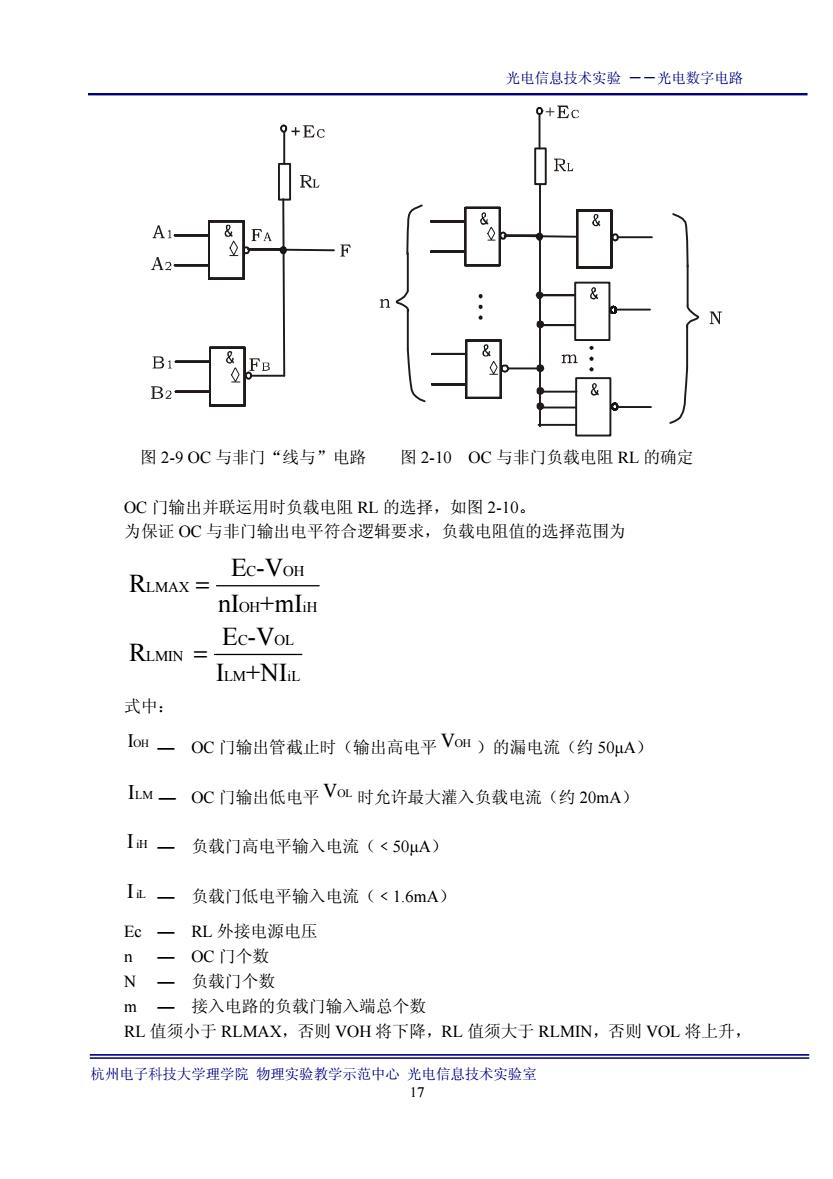

光电信息技术实验一一光电数字电路 9+Ec 9+Ec R 图2-90C与非门“线与”电路 图2-10OC与非门负载电阻RL的确定 OC门输出并联运用时负载电阻RL的选择,如图2-10。 为保证OC与非门输出电平符合逻辑要求,负载电阻值的选择范围为 Ec-VoH RLMAX nloH+mli RLMIN Ec-VoL ILM+NIiL 式中: Io:一OC门输出管截止时(输出高电平Vo)的漏电流(约50uA) IM一OC门输出低电平VoL时允许最大灌入负载电流(约20mA) IH一负载门高电平输入电流(<50μA) IL一负载门低电平输入电流(<1.6mA) Ec- RL外接电源电压 n 一0C门个数 N- 负载门个数 m 一接入电路的负载门输入端总个数 RL值须小于RLMAX,否则VOH将下降,RL值须大于RLMN,否则VOL将上升, 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

光电信息技术实验 ――光电数字电路 图 2-9 OC 与非门“线与”电路 图 2-10 OC 与非门负载电阻 RL 的确定 OC 门输出并联运用时负载电阻 RL 的选择,如图 2-10。 为保证 OC 与非门输出电平符合逻辑要求,负载电阻值的选择范围为 C OH LMAX OH iH C OL LMIN LM iL E -V R nI +mI E -V R I +NI 式中: IOH — OC 门输出管截止时(输出高电平 )的漏电流(约 VOH 50μA) ILM — OC 门输出低电平 时允许最大灌入负载电流(约 VOL 20mA) I iH — 负载门高电平输入电流(﹤50μA) I iL — 负载门低电平输入电流(﹤1.6mA) Ec — RL 外接电源电压 n — OC 门个数 N — 负载门个数 m — 接入电路的负载门输入端总个数 RL 值须小于 RLMAX,否则 VOH 将下降,RL 值须大于 RLMIN,否则 VOL 将上升, 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 17

光电信息技术实验一一光电数字电路 又RL的大小会影响输出波形的边沿时间,在工作速度较高时,RL应尽量选取接近 RLMIN (2)、TTL三态门输出门(3S门) TTL三态输出门是一种特殊的门电路,它与普通的TTL门电路结构不同,它的输出 端除了平常的高电平、低电平两种状态外(这两种状态均为低阻状态),还有第三种 输出状态一高阻状态,处于高阻状态时,电路与负载之间相当于开路。三态输出门按 逻辑功能及控制方式来分有各种不同类型。如图2-11和表2-1。本实验所用三态门的 型号是74LS125三态输出四总线缓冲器。 图2-11三态缓冲器逻辑符号 表21 输 入 输出 A Y 0 0 0 1 0 高阻态 三态门主要用途之一是实现总线传输,即用一个传输通道(称总线),以选通方 式传送多路信息。图2-12中,电路中把若开个三态TTL电路输出端直接连接在一起 构成三态门总线,使用时,要求只有需要传输信息的三态控制端处于使能状态(E=O) 其余各门均处于禁止状态(E=1)。由于三态门输出电路结构与普通TTL电路相同, 显然,若同时有两个或两个以上三态门的控制处于使能状态,将出现与普通TTL门“线 与”运用时同样的问题,因而是绝对不允许的。 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

光电信息技术实验 ――光电数字电路 又 RL 的大小会影响输出波形的边沿时间,在工作速度较高时,RL 应尽量选取接近 RLMIN (2)、TTL 三态门输出门(3S 门) TTL 三态输出门是一种特殊的门电路,它与普通的 TTL 门电路结构不同,它的输出 端除了平常的高电平、低电平两种状态外(这两种状态均为低阻状态),还有第三种 输出状态—高阻状态,处于高阻状态时,电路与负载之间相当于开路。三态输出门按 逻辑功能及控制方式来分有各种不同类型。如图 2-11 和表 2-1。本实验所用三态门的 型号是 74LS125 三态输出四总线缓冲器。 图 2-11 三态缓冲器逻辑符号 表 2-1 输 入 输 出 E A Y 0 0 0 1 0 高阻态 三态门主要用途之一是实现总线传输,即用一个传输通道(称总线),以选通方 式传送多路信息。图 2-12 中,电路中把若开个三态 TTL 电路输出端直接连接在一起 构成三态门总线,使用时,要求只有需要传输信息的三态控制端处于使能状态(E=0), 其余各门均处于禁止状态(E=1)。由于三态门输出电路结构与普通 TTL 电路相同, 显然,若同时有两个或两个以上三态门的控制处于使能状态,将出现与普通 TTL 门“线 与”运用时同样的问题,因而是绝对不允许的。 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 18

光电信息技术实验一一光电数字电路 数据总线 -117 图2-12三态输出门实现总线传输 74LS125管脚图:如图2-13 其特点:三态门的输出除了0态、1态以外,还可以呈现高阻态,或称开路状态 利用三态门可以实现总线结构,还可以实现数据的双向传输。 Cc匝4A4Y3鉅3A3Y g回母日月可网 -o-西oa 1E 1A 1Y 2E 2A 2Y GND 图2-1374LS125(四路三态缓冲门) 三、实验仪器及材料 1、双踪示波器 2、元器件 TTL芯片: 74LS00 四2输入与非门 1片 74LS125三态门 1片 74LS07 集电极开路门 1片 喜安表 0~50mA 1只 电压表 0~5V 2只 杭州电子科技大学理学院物理实验教学示范中心光电信息技术实验室

光电信息技术实验 ――光电数字电路 图 2-12 三态输出门实现总线传输 74LS125 管脚图:如图 2-13 其特点:三态门的输出除了 0 态、1 态以外,还可以呈现高阻态,或称开路状态。 利用三态门可以实现总线结构,还可以实现数据的双向传输。 图 2-13 74LS125(四路三态缓冲门) 三、实验仪器及材料 1、双踪示波器 2、元器件 TTL 芯片: 74LS00 四 2 输入与非门 1 片 74LS125 三态门 1 片 74LS07 集电极开路门 1 片 毫安表 0~50mA 1 只 电压表 0~5V 2 只 杭州电子科技大学理学院 物理实验教学示范中心 光电信息技术实验室 19