历些毛子种枝大 5.38086CPU的脚功能及时序 XIDIAN UNIVERSITY GND Vcc AD14 2 39 AD15 AD13 3 A16/S3 AD12 38 37 A17/S4 AD11 5 36 A18/S5 6 35 A19/S6 AD9 7 BHE/S7 最大方式 INTEL 34 8 8 MN/MX (24-31) 33P9 AD7 9 8086 D D6 2 (RQ/GTO CPU 31P HOLD AD5 30P ◆ HLDA RQ/GT1→ AD4 2 (LOCK) 29 AD3 28 ◆ M/IO (S2) AD2 DT/R 26 ◆ DE丽 (S0) hel 5 ALE (Qs0) 1 INTR 24 INTA (QS1) CLK 23 Test 19 READY 0 21 RESET 8086引脚说明 最小方式 徽机原理与系统设计 第五章 总线及其形成 薏明皓 dminghao@xidian.edu.cn 27

8086引脚说明 (RQ/GTO) (RQ/GT1) (LOCK) (S2) (S1) (S0) (QS0) (QS1) 最小方式 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 GND AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND INTEL 8086 CPU Vcc AD15 A16/S3 A17/S4 A18/S5 A19/S6 BHE/S7 MN/MX RD HOLD HLDA WR M /IO DT/R DEN ALE INTA TEST READY RESET 最大方式 (24-31) 27 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn

历些毛子种技大学 5.3 8086CPU的引脚功能及时序 XIDIAN UNIVERSITY ·最小方式: 适合用于由单处理器组成的小系统。 在这种方式中,8088/8086CPU引脚直接产生存贮器或I/O读 写的读写命令等控制信号。 ·最大方式: 适合用于实现多处理器系统。 在这种方式中,8088/8086CPU不直接提供用于存贮器或I/O 读写的读写命令等控制信号,而是将当前要执行的传送操作 类型编码为三个状态位(S2,S1,S0)输出,由外部的总线控 制器8288对状态信号进行译码产生相应信号。 徽机原理与系统设计 第五章总线及其形成 董明皓 dminghao@xidian.edu.cn

• 最小方式: 适合用于由单处理器组成的小系统。 在这种方式中,8088/8086CPU引脚直接产生存贮器或I/O读 写的读写命令等控制信号。 • 最大方式: 适合用于实现多处理器系统。 在这种方式中,8088/8086CPU不直接提供用于存贮器或I/O 读写的读写命令等控制信号,而是将当前要执行的传送操作 类型编码为三个状态位(S2,S1,S0)输出,由外部的总线控 制器8288对状态信号进行译码产生相应信号。 28 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn

历安毛子种枝大学 5.38086CPU的脚功能及时序 XIDIAN UNIVERSITY 两种方式下部分控制引脚的功能不同; ·主要介绍8086的控制引脚; ·对8088进行对比说明。 8086最小方式 系统总线结构 徽机原理与系统设计 第五章总线及其形成 董明皓 dminghao@xidian.edu.cn 29

• 两种方式下部分控制引脚的功能不同; • 主要介绍8086的控制引脚; • 对8088进行对比说明。 8086 最小方式 系统总线结构 29 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn

历些毛子种枝大” 5.3 8086CPU的引脚功能及时序 XIDIAN UNIVERSITY CLK (入)时钟信号 GND Vcc 8086/8088的CLK信号由8284A 2 39 AD15 3 38 ◆A16/S3 时钟发生器产生 37 A17/S4 5 36 A18/S5 时钟信号占空比为33%时是最 6 35 A19/S6 7 ◆ 34 BHE/S7 佳状态 8 INTEL 33 MN/MX 8086 最高频率对8086和8088为 32 RD 10 CPU 31 HOLD 11 ◆HDA 5MHz 30 12 0000 29 丽 13 ◆M/i0 对8086-2为8MHz,对8086-1为 27 DT/原 6 10MHz 26 E丽 16 2 ALE 17 24 INTA 23 TEST CLK 19 22 READY 21 RESET 微机原理与系统设计 第五章总线及其形成 董明皓 dminghao@xidian.edu.cn 30

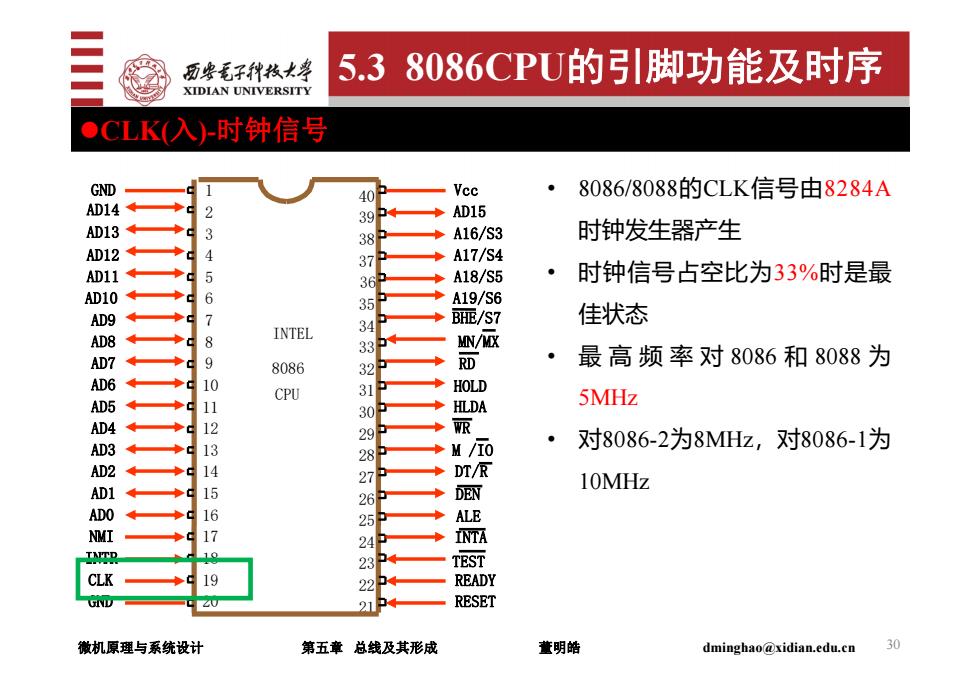

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 GND AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND INTEL 8086 CPU Vcc AD15 A16/S3 A17/S4 A18/S5 A19/S6 BHE/S7 MN/MX RD HOLD HLDA WR M /IO DT/R DEN ALE INTA TEST READY RESET • 8086/8088的CLK信号由8284A 时钟发生器产生 • 时钟信号占空比为33%时是最 佳状态 • 最高频率对 8086 和 8088 为 5MHz • 对8086-2为8MHz,对8086-1为 10MHz CLK(入)-时钟信号 30 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn

历粤毛子代枝大势 5.38086CPU的脚功能及时序 XIDIAN UNIVERSITY CLK(入)时钟信号 ·时序:三种总线上出现的信息不但有严格的顺序,而且有准 确的时间,称为时序 ·时钟:时钟脉冲发生器产生具有一定频率和占空比的脉冲信 号,称之为机器的主脉冲或时钟 ·主频:时钟的频率,是衡量CPU性能的一个重要指标 徽机原理与系统设计 第五章总线及其形成 董明皓 dminghao@xidian.edu.cn 31

• 时序:三种总线上出现的信息不但有严格的顺序,而且有准 确的时间,称为时序 • 时钟:时钟脉冲发生器产生具有一定频率和占空比的脉冲信 号,称之为机器的主脉冲或时钟 • 主频:时钟的频率,是衡量CPU性能的一个重要指标 CLK(入)-时钟信号 31 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn