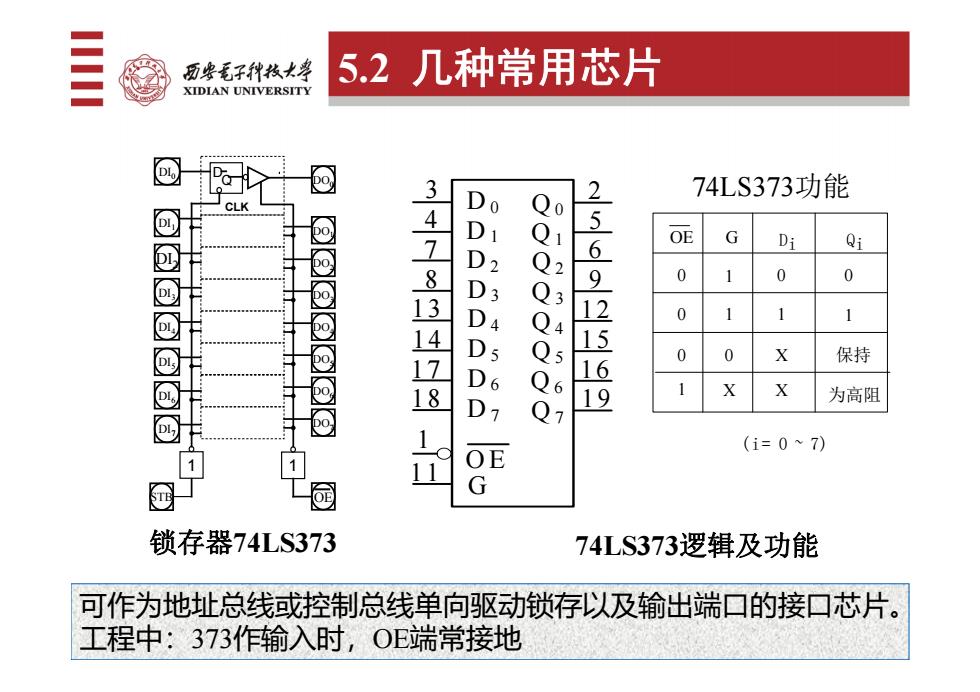

历粤毛子代枝大” 5.2几种常用芯片 XIDIAN UNIVERSITY 可 74LS373功能 34783478 2569 OE G Di Qi 0 1 0 0 0 1 1 0 0 X 保持 Q7 为高阻 (i=0~7) @ 锁存器74LS373 74LS373逻辑及功能 可作为地址总线或控制总线单向驱动锁存以及输出端口的接口芯片。 工程中:373作输入时,OE端常接地

D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 O E G Q 0 Q 1 Q 2 Q 3 Q 4 Q 5 Q 6 Q 7 3 4 7 8 13 14 17 18 1 11 2 5 6 9 15 12 16 19 ~ OE G 0 1 0 1 1 X 为高阻 Di Qi 0 0 1 1 X 00 X 保持 ( i= 0 7) 74LS373逻辑及功能 Q 74LS373功能 DI0 DO0 DI1 DI2 DI3 DI4 DI5 DI6 DI7 1 STB 1 OE DO1 DO2 DO3 DO4 DO5 DO6 DO7 D CLK 锁存器74LS373 可作为地址总线或控制总线单向驱动锁存以及输出端口的接口芯片。 工程中:373作输入时,OE端常接地 5.2 几种常用芯片

历安毛子绑牧大学 XIDIAN UNIVERSITY 8086的引脚功能及时序 徽机原理与系统设计 第五章总线及其形成 董明皓 dminghao@xidian.edu.cn 18

1 总线定义及分类 2 3 4 系统总线的形成 5 8088与8086的差异 几种常用芯片 8086的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 18 dminghao@xidian.edu.cn

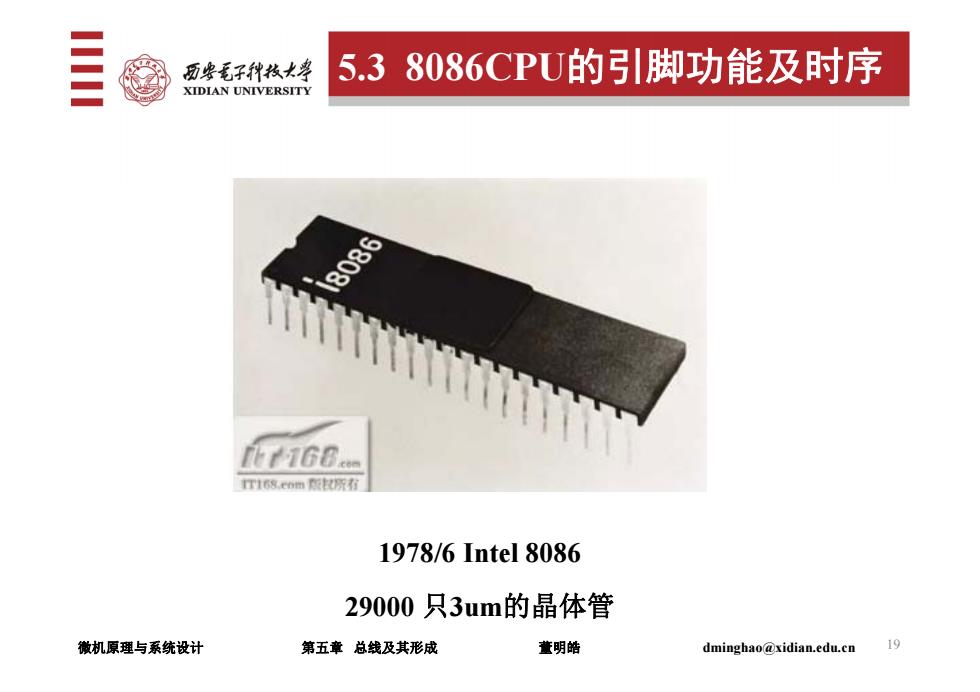

历安毛子种枝大学 5.38086CPU的脚功能及时序 XIDIAN UNIVERSITY 8086 tt160 T168.nm度忆所有 1978/6 Intel8086 29000只3um的晶体管 徽机原理与系统设计 第五章总线及其形成 董明皓 dminghao@xidian.edu.cn

1978/6 Intel 8086 29000 只3um的晶体管 19 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn

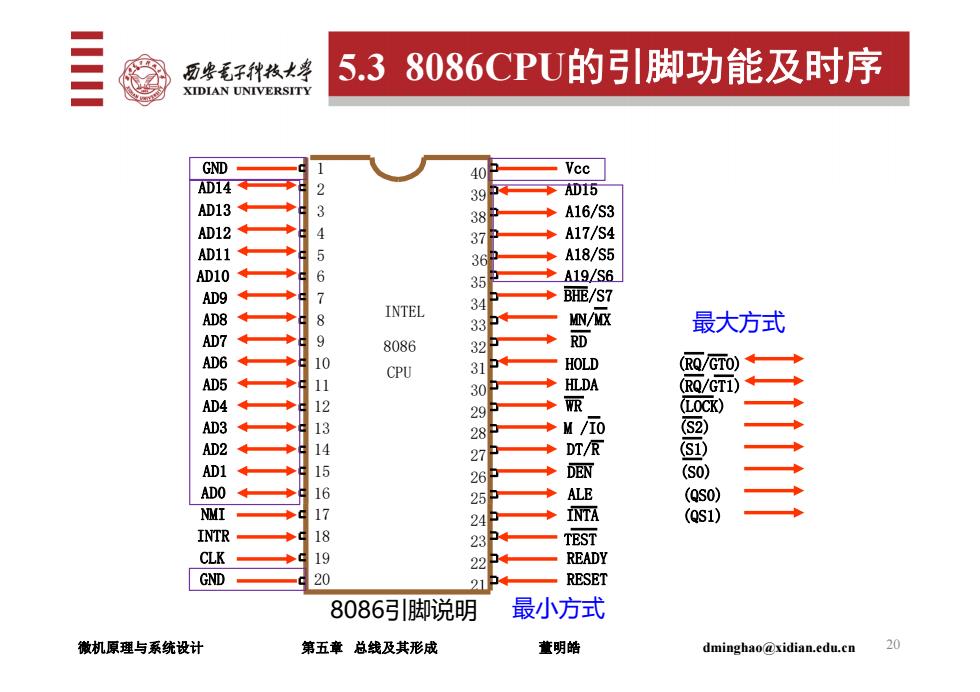

历安毛子种牧大” 5.3 8086CPU的引脚功能及时序 XIDIAN UNIVERSITY GND Vcc AD14 2 AD13 39 ◆AD15 3 38 A16/S3 37 A17/S4 36 A18/S5 6 AD9 35 A19/S6 34 BH亚/S7 AD8 8 INTEL 33 /MX 最大方式 AD7 9 8086 32 D AD6 CPU 31 HOLD GTO) AD5 30 HLDA AD4 1 29 AD3 28 M/IO AD2 3 DT/原 15 26 DE邵 ADO 25 ALE NMI 1 24 INTA (Qs1) INTR 23 test CLK 9 22 READY GND 20 21 RESET 8086引脚说明 最小方式 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn 20

8086引脚说明 (RQ/GTO) (RQ/GT1) (LOCK) (S2) (S1) (S0) (QS0) (QS1) 最大方式 最小方式 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 GND AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND INTEL 8086 CPU Vcc AD15 A16/S3 A17/S4 A18/S5 A19/S6 BHE/S7 MN/MX RD HOLD HLDA WR M /IO DT/R DEN ALE INTA TEST READY RESET 20 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn

历粤毛子代枝大 5.38086CPU的脚功能及时序 XIDIAN UNIVERSITY ●引脚的功能 ·微处理器通过这些引脚与外部的逻辑部件连接,完成信 息(指令及数据)的交换。 1. 与存储器之间交换信息; 2. 与/O设备之间交换信息; 3. 能输入和输出必要的信号。 CPU引脚 微处理级总线 徽机原理与系统设计 第五章总线及其形成 董明皓 dminghao@xidian.edu.cn 21

• 微处理器通过这些引脚与外部的逻辑部件连接,完成信 息(指令及数据)的交换。 1. 与存储器之间交换信息; 2. 与I/O设备之间交换信息; 3. 能输入和输出必要的信号。 CPU引脚 微处理级总线 引脚的功能 21 5.3 8086CPU的引脚功能及时序 微机原理与系统设计 第五章 总线及其形成 董明皓 dminghao@xidian.edu.cn