实验二:组合逻辑电路与集成器件一、实验目的:1、了解集成数据选择器74LS151、加法器74LS283、数值比较器74LS85的管脚排列和管脚功能;2、了解集成编码器74LS148、译码器74LS47和数码管(共阳极)的管脚排列和管脚功能:3、掌握集成数据选择器、加法器、数值比较器的性能及使用方法;4、掌握集成编码器、译码器和数码管的性能及使用方法;5、掌握用MSI中规模集成器件设计组合逻辑电路的方法,用实验验证所设计电路的功能二、实验内容1、某工厂有三个车间A、B,C,有一个自备电站,站内有二台发电机M和N,N的发电能力是M的两倍,如果一个车间开工,启动M就可以满足要求;如果两个车间开工,启动N就可以满足要求;如果三个车间同时开工,同时启动M、N才能满足要求。试用异或门(74LS86)和与非门(74LS00)设计一个控制电路,因车间的开工情况来控制M和N的启动。2、用译码器 74LS138和多路数据选择器74LS151设计一个信息的“并行一串行一并行”传送电路。3、利用4位集成全加器74LS283设计一个BCD码加法器。结构示意图见下图所示。注加6补偿电路甲修正信号产生电路图 BCD码加法器原理框图4、译码、显示电路的设计(74LS47、共阳极数码显示管)译码、显示原理电路框图如下图所示。A、A2、Ar、A。接逻辑开关,作为十进制数据输入,用数码管显示其数字

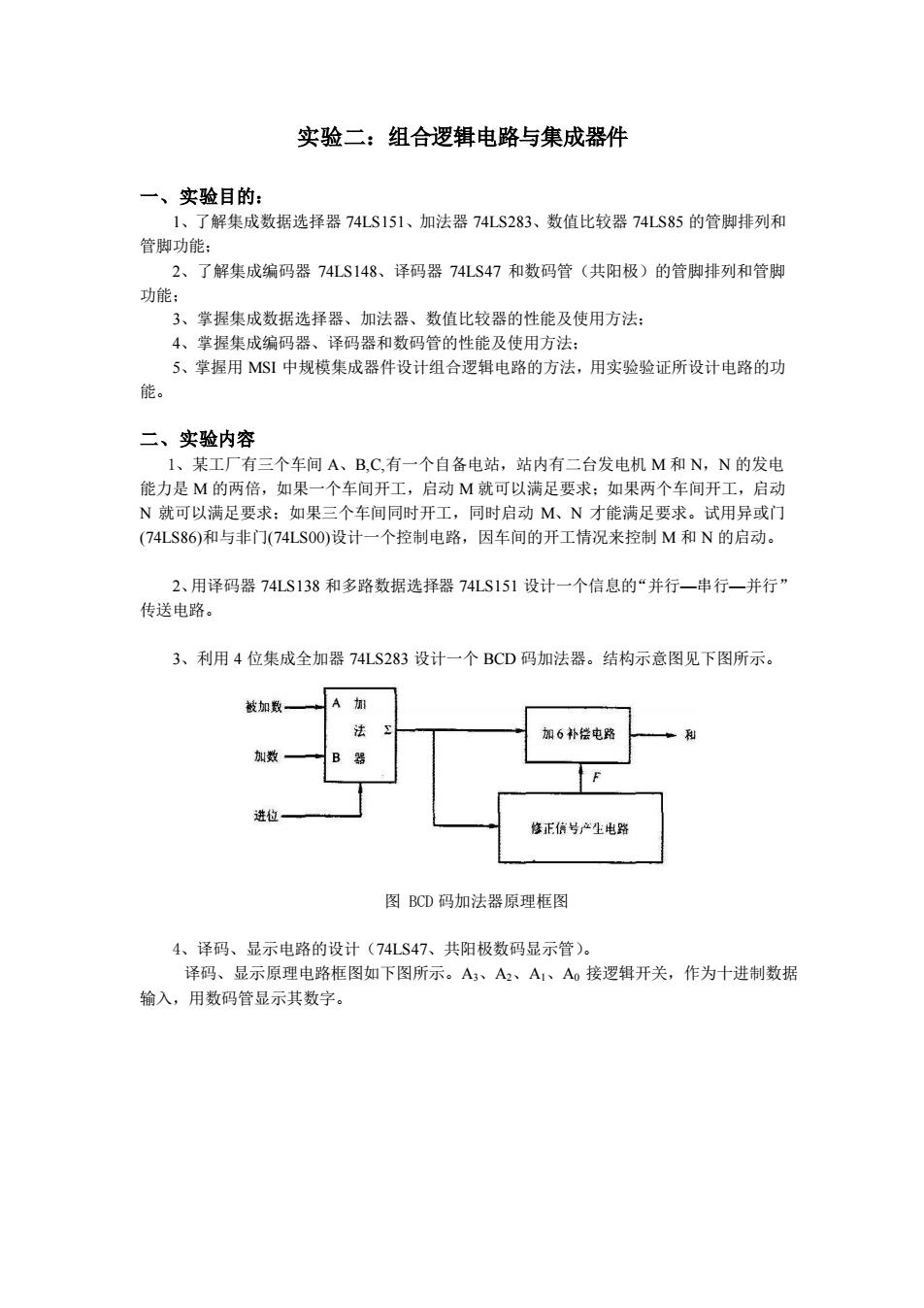

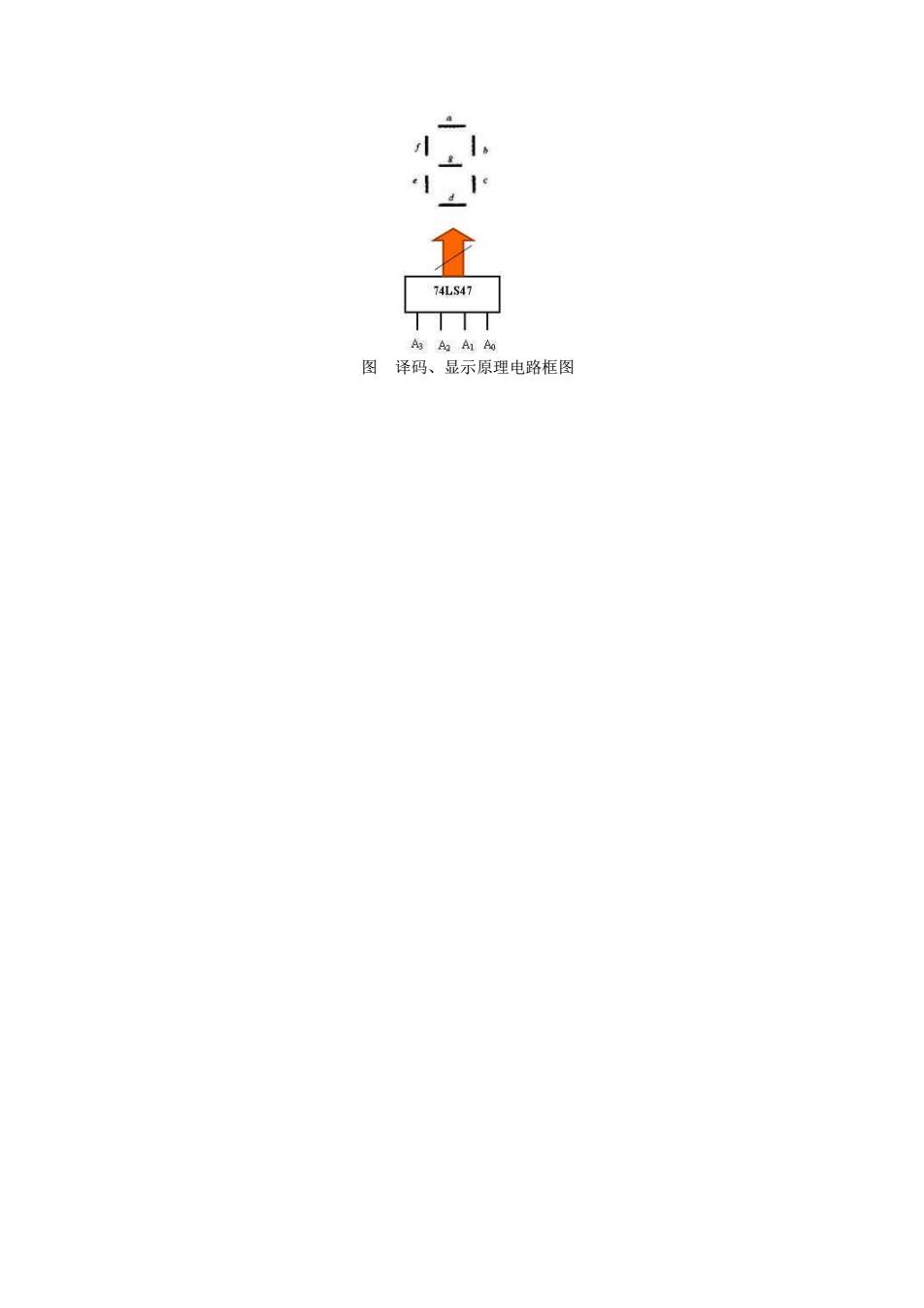

实验二:组合逻辑电路与集成器件 一、实验目的: 1、了解集成数据选择器 74LS151、加法器 74LS283、数值比较器 74LS85 的管脚排列和 管脚功能; 2、了解集成编码器 74LS148、译码器 74LS47 和数码管(共阳极)的管脚排列和管脚 功能; 3、掌握集成数据选择器、加法器、数值比较器的性能及使用方法; 4、掌握集成编码器、译码器和数码管的性能及使用方法; 5、掌握用 MSI 中规模集成器件设计组合逻辑电路的方法,用实验验证所设计电路的功 能。 二、实验内容 1、某工厂有三个车间 A、B,C,有一个自备电站,站内有二台发电机 M 和 N,N 的发电 能力是 M 的两倍,如果一个车间开工,启动 M 就可以满足要求;如果两个车间开工,启动 N 就可以满足要求;如果三个车间同时开工,同时启动 M、N 才能满足要求。试用异或门 (74LS86)和与非门(74LS00)设计一个控制电路,因车间的开工情况来控制 M 和 N 的启动。 2、用译码器 74LS138 和多路数据选择器 74LS151 设计一个信息的“并行—串行—并行” 传送电路。 3、利用 4 位集成全加器 74LS283 设计一个 BCD 码加法器。结构示意图见下图所示。 图 BCD 码加法器原理框图 4、译码、显示电路的设计(74LS47、共阳极数码显示管)。 译码、显示原理电路框图如下图所示。A3、A2、A1、A0 接逻辑开关,作为十进制数据 输入,用数码管显示其数字

74LS47TTTTASAIA图译码、显示原理电路框图

图 译码、显示原理电路框图