Note 帧中继仅工作在物理层和数据链路层. 18.6

18.6 帧中继仅工作在物理层和数据链路层. Note

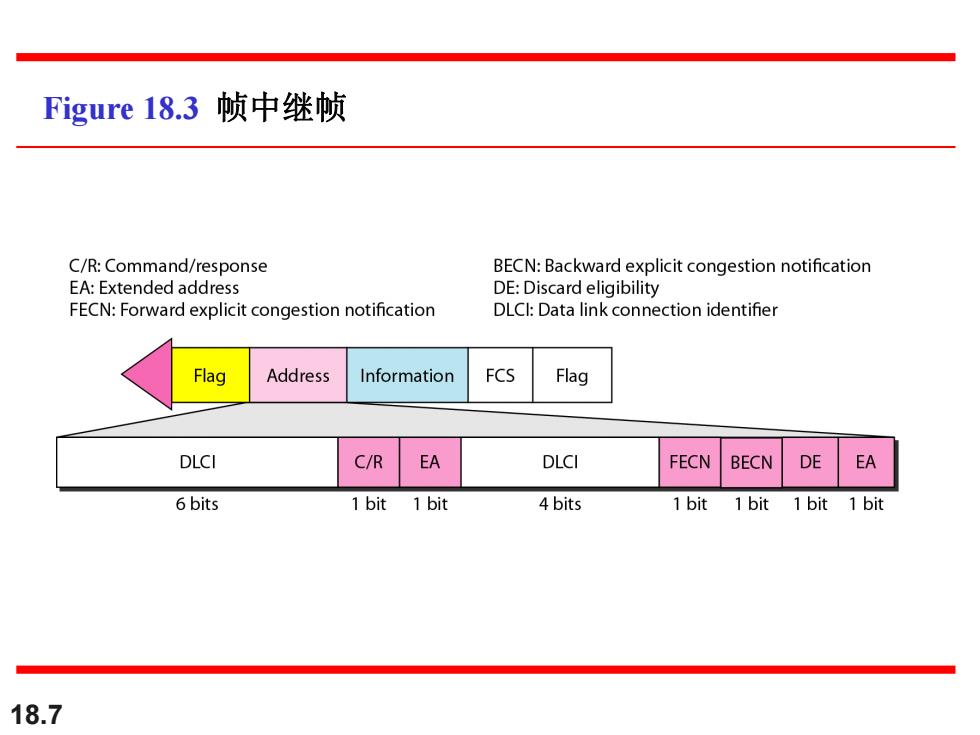

Figure18.3帧中继帧 C/R:Command/response BECN:Backward explicit congestion notification EA:Extended address DE:Discard eligibility FECN:Forward explicit congestion notification DLCl:Data link connection identifier Flag Address Information FCS Flag DLCI C/R EA DLCI FECN BECN DE EA 6 bits 1 bit 1 bit 4bits 1 bit 1 bit 1 bit 1 bit 18.7

18.7 Figure 18.3 帧中继帧

Note 帧中继不提供流量和差错控制, 这些必须由上层协议提供. 18.8

18.8 帧中继不提供流量和差错控制, 这些必须由上层协议提供. Note

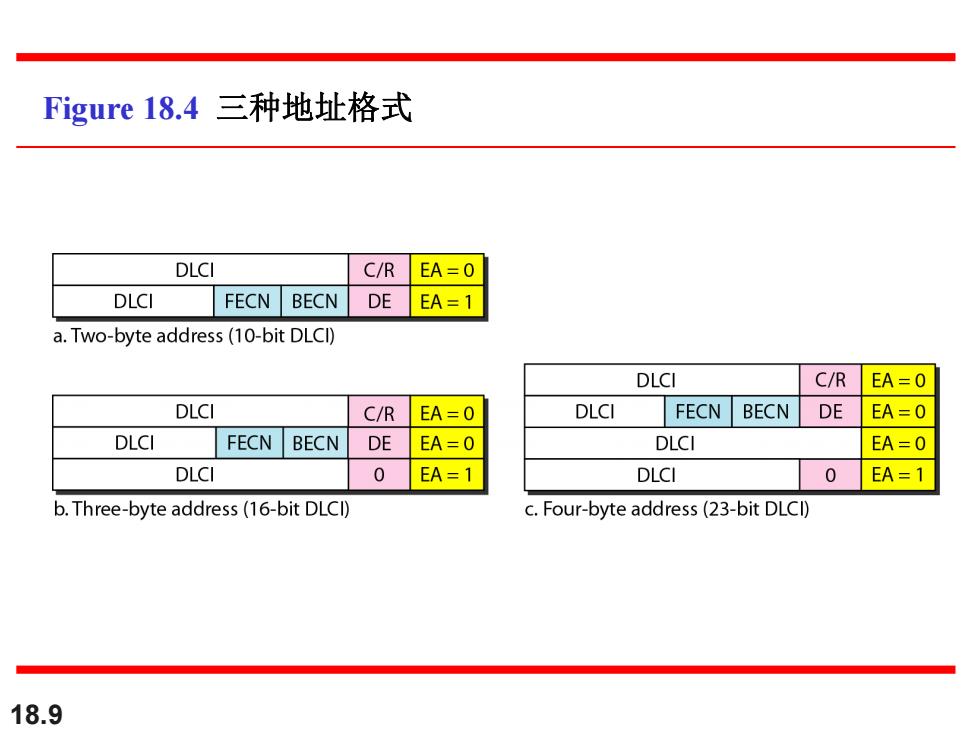

Figure18.4三种地址格式 DLCI C/R EA=0 DLCI FECN BECN DE EA=1 a.Two-byte address(10-bit DLCI) DLCI C/R EA=0 DLCI C/R EA=0 DLCI FECN BECN DE EA=0 DLCI FECN BECN DE EA=0 DLCI EA=0 DLCI 0 EA=1 DLCI 0 EA=1 b.Three-byte address(16-bit DLCI) c.Four-byte address(23-bit DLCI) 18.9

18.9 Figure 18.4 三种地址格式

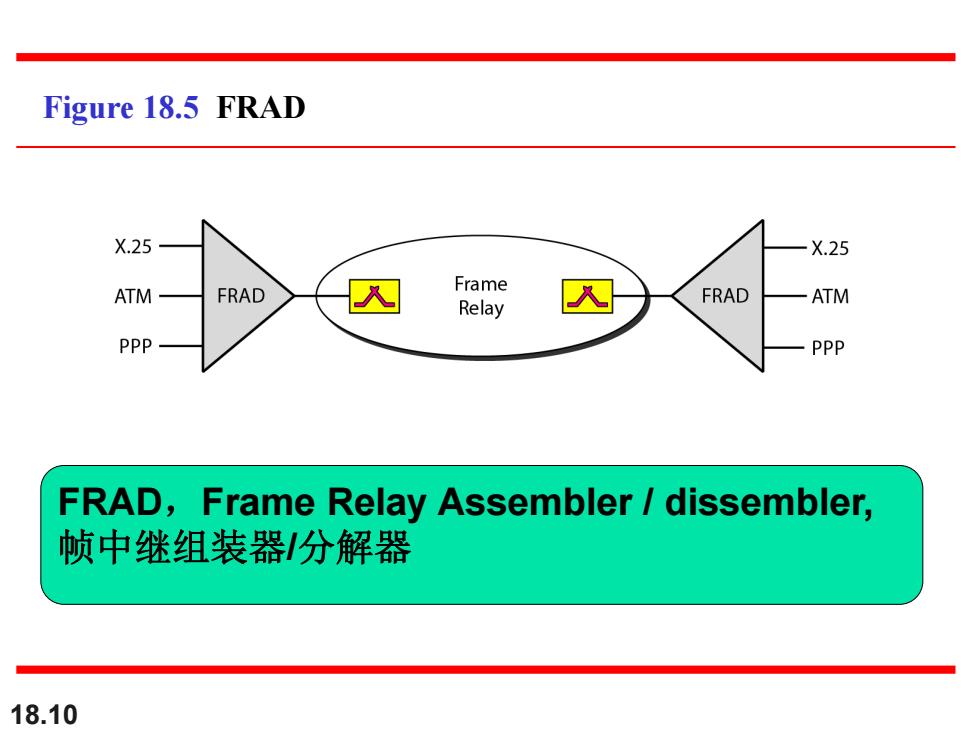

Figure 18.5 FRAD X.25 X.25 ATM FRAD Frame FRAD Relay ATM PPP PPP FRAD,Frame Relay Assembler dissembler, 帧中继组装器/分解器 18.10

18.10 Figure 18.5 FRAD FRAD,Frame Relay Assembler / dissembler, 帧中继组装器/分解器