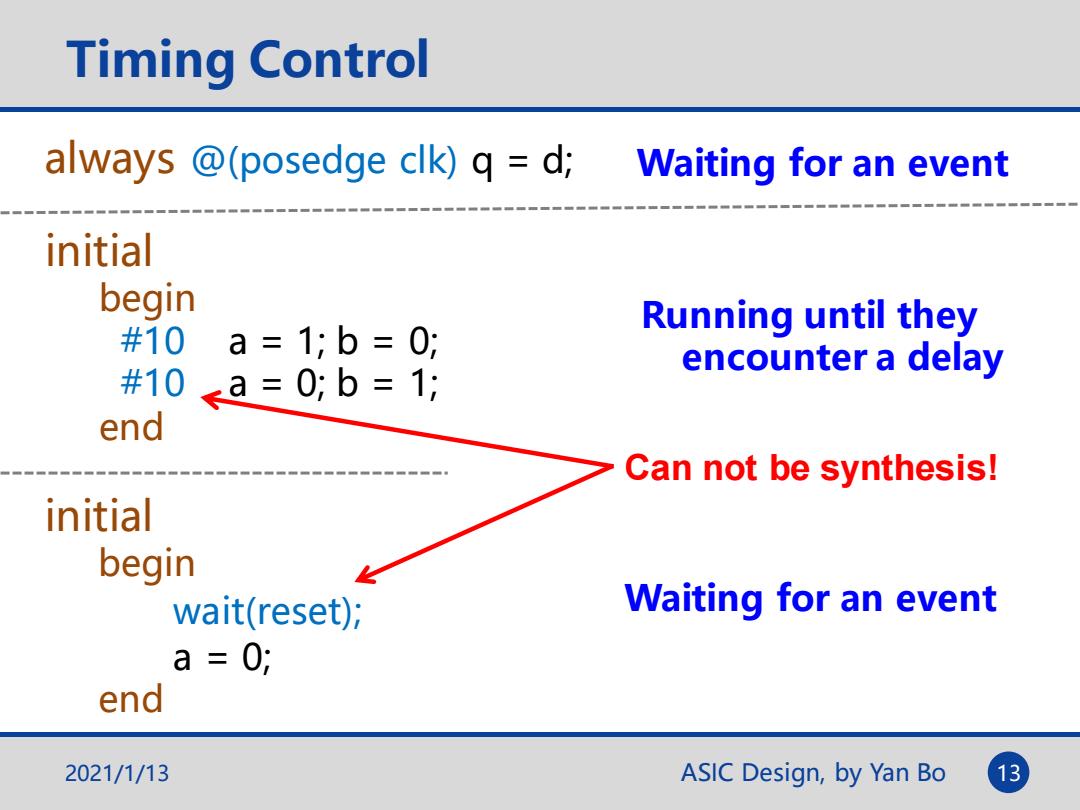

Timing Control always @(posedge clk)q d; Waiting for an event initial begin #10 Running until they a=1;b=0; encounter a delay #10 <a=0;b=1; end Can not be synthesis! initial begin wait(reset); Waiting for an event a=0; end 2021/1/13 ASIC Design,by Yan Bo 13

ASIC Design, by Yan Bo Timing Control initial begin #10 a = 1; b = 0; #10 a = 0; b = 1; end always @(posedge clk) q = d; initial begin wait(reset); a = 0; end Running until they encounter a delay Waiting for an event Waiting for an event 2021/1/13 13 Can not be synthesis!

@ vs.wait denotes event control: That follow the event-control expression do not execute until an activating event occurs. When such an event occurs,the statements execute in sequence,top to bottom. Wait (denotes wait control: The process will be stopped if the wait-control expression is FALSE The process will be continued if the wait-control expression is TURE. 2021/1/13 ASIC Design,by Yan Bo 14

ASIC Design, by Yan Bo @ vs. wait @ denotes event control: That follow the event-control expression do not execute until an activating event occurs. When such an event occurs, the statements execute in sequence, top to bottom. Wait ( ) denotes wait control: The process will be stopped if the wait-control expression is FALSE. The process will be continued if the wait-control expression is TURE. 2021/1/13 14

System tasks:Simulation Control module test_moore_detector; reg x=0,reset=1,clock=0; wire z; initial moore_detector MUT (x,reset,clock,z); begin initial #24 reset=1'b0; #24 reset=1'b0; always #5 clock=~clock; #165 $finish; always #7X=~X; end Initial #189$stop; always #5 clock=~clock; endmodule always #7 x=~x; The first time the flow of a The first time the flow of a procedural block reaches $stop at procedural block reaches Sfinish 189 ns,simulation stops. at 189 ns,simulation terminates. A stopped simulation can be resumed. A finished simulation cannot be resumed. 2021/1/13 ASIC Design,by Yan Bo 15

ASIC Design, by Yan Bo 15 System tasks: Simulation Control module test_moore_detector; reg x=0, reset=1, clock=0; wire z; moore_detector MUT ( x, reset, clock, z ); endmodule initial #24 reset=1'b0; always #5 clock=~clock; always #7 x=~x; Initial #189 $stop; The first time the flow of a procedural block reaches $stop at 189 ns, simulation stops. A stopped simulation can be resumed. initial begin #24 reset=1'b0; #165 $finish; end always #5 clock=~clock; always #7 x=~x; The first time the flow of a procedural block reaches $finish at 189 ns, simulation terminates. A finished simulation cannot be resumed. 2021/1/13

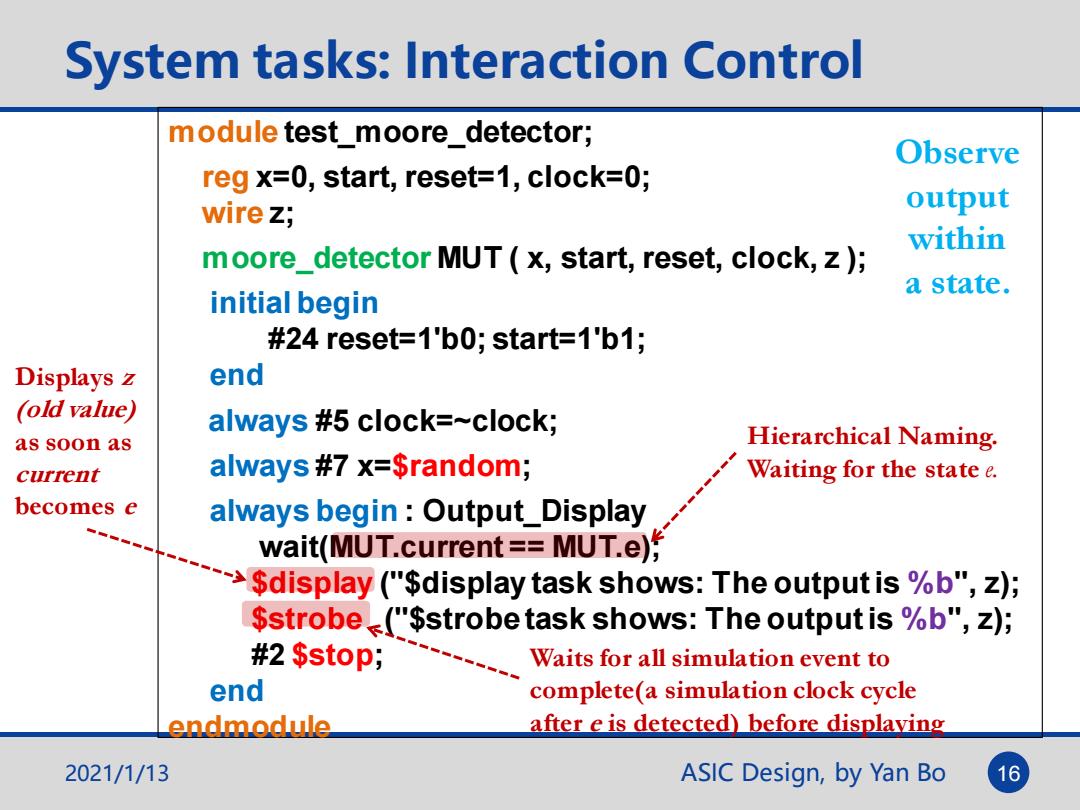

System tasks:Interaction Control module test moore_detector; Observe reg x=0,start,reset=1,clock=0; wire Z; output within moore_detector MUT (x,start,reset,clock,z ) a state. initial begin #24 reset=1'b0;start=1'b1; Displays z end (old value) always #5 clock=~clock; as soon as Hierarchical Naming. current always #7 x=Srandom; Waiting for the state e. becomes e always begin:Output_Display wait(MUT.current =MUT.e) $display ("$display task shows:The output is %b",z); $strobe ("$strobe task shows:The output is %b",z); #2 $stop; Waits for all simulation event to end complete(a simulation clock cycle endmodule after e is detected)before displaving 2021/1/13 ASIC Design,by Yan Bo 16

ASIC Design, by Yan Bo 16 System tasks: Interaction Control module test_moore_detector; reg x=0, start, reset=1, clock=0; wire z; moore_detector MUT ( x, start, reset, clock, z ); initial begin #24 reset=1'b0; start=1'b1; end always #5 clock=~clock; always #7 x=$random; always begin : Output_Display wait(MUT.current == MUT.e); $display ("$display task shows: The output is %b", z); $strobe ("$strobe task shows: The output is %b", z); #2 $stop; end endmodule Hierarchical Naming. Waiting for the state e. Displays z (old value) as soon as current becomes e Waits for all simulation event to complete(a simulation clock cycle after e is detected) before displaying Observe output within a state. 2021/1/13

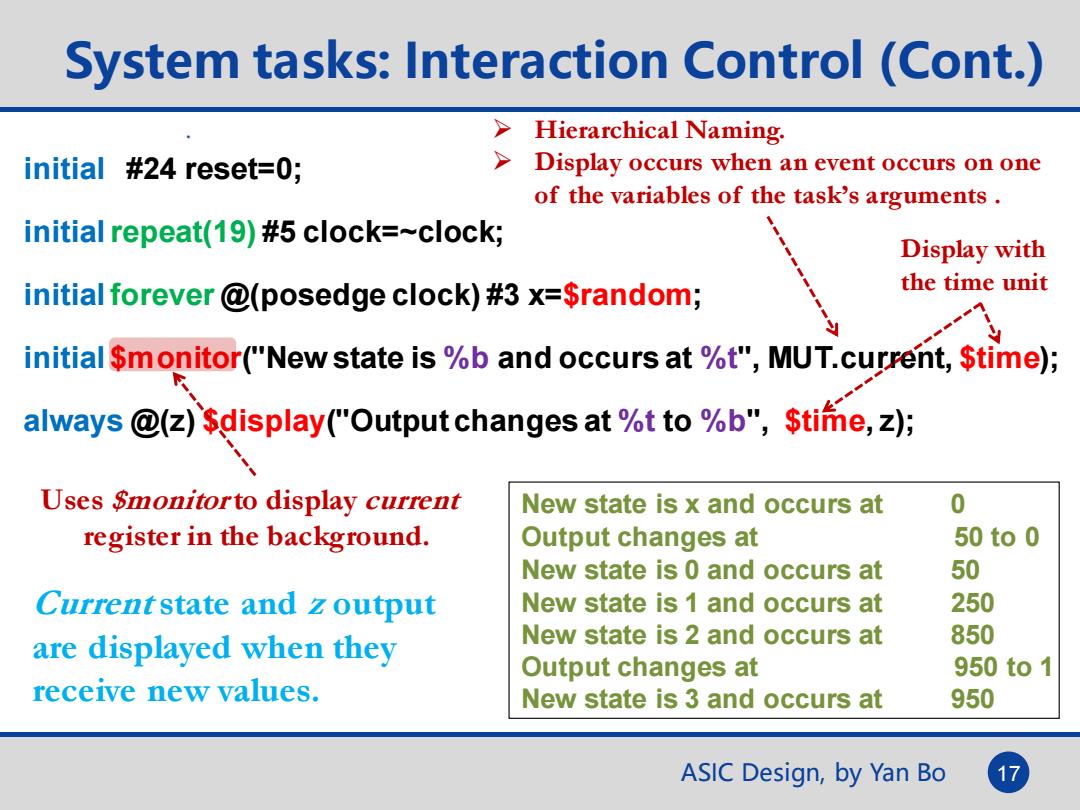

System tasks:Interaction Control (Cont.) Hierarchical Naming. initial #24 reset=0; Display occurs when an event occurs on one of the variables of the task's arguments. initial repeat(19)#5 clock=~clock; Display with initial forever @(posedge clock)#3 x=$random; the time unit initial $monitor("New state is %b and occurs at %t",MUT.current,$time); always @(z)$display("Output changes at %t to %b",Stime,z); Uses Smonitorto display current New state is x and occurs at 0 register in the background. Output changes at 50to0 New state is 0 and occurs at 50 Currentstate and z output New state is 1 and occurs at 250 are displayed when they New state is 2 and occurs at 850 Output changes at 950to1 receive new values. New state is 3 and occurs at 950 ASIC Design,by Yan Bo

ASIC Design, by Yan Bo New state is x and occurs at 0 Output changes at 50 to 0 New state is 0 and occurs at 50 New state is 1 and occurs at 250 New state is 2 and occurs at 850 Output changes at 950 to 1 New state is 3 and occurs at 950 17 initial #24 reset=0; initialrepeat(19) #5 clock=~clock; initial forever @(posedge clock) #3 x=$random; initial $monitor("New state is %b and occurs at %t", MUT.current, $time); always @(z) $display("Output changes at %t to %b", $time, z); System tasks: Interaction Control (Cont.) ➢ Hierarchical Naming. ➢ Display occurs when an event occurs on one of the variables of the task’s arguments . Uses $monitor to display current register in the background. Display with the time unit . Current state and z output are displayed when they receive new values