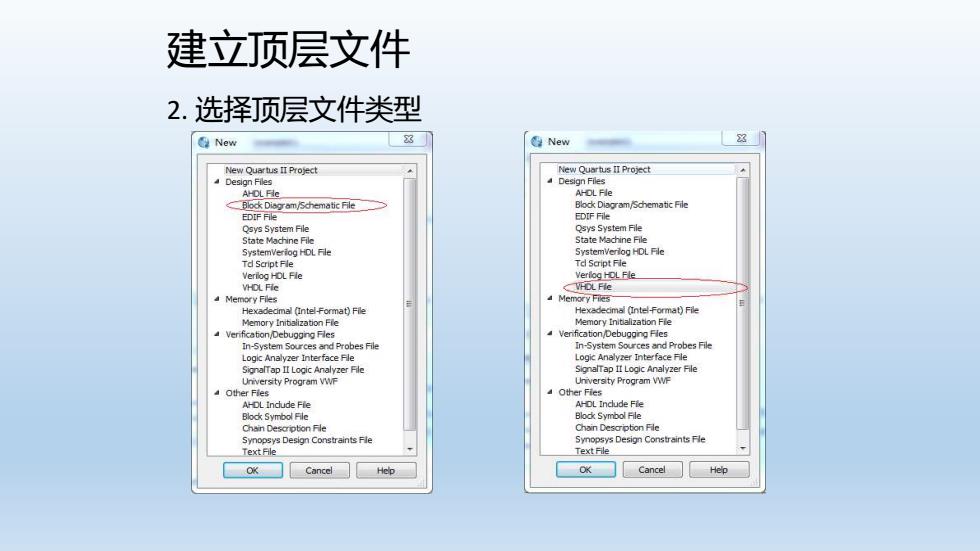

建立顶层文件 2.选择顶层文件类型 New 径NeW New Quartus II Project New Quartus II Project Design Files Design Files AHOLEe AHDL Fle ←Ba&Digram/5小hematic File Block Diagram/Schematic File EDIF File EDIF File Qsys System File Qsys System File State Machine File State Machine File SystemVerlog HDL Fle Td Script Fle Td Script Fle Veriog HOL Fle Verilog HDL Fle VHOL FLe VHDL Fle 4Memory Files 4 Memory Files Hexadedmal (Intel-Format)File Hexadecimal (Intel-Format)File Memory Initalization Fie Memory Initialization Fie Verification/Debugging Fles Verification/Debuggng Fles In-System Sources and Probes File In-System Sources and Probes File Logic Analyzer Interface Fle Logic Analyzer Interface Fle SignalTap II Logic Analyzer File SignalTap If Logic Analyzer File University Program VWF University Program VF 4Other Fies Other Fies AHDL Indude Fle AHDL Indude Fle Block Symbol File Block Symbol File Chain Desaription Fle Chain Desaription Fle Synopsys Design Constraints Fle Synopsys Design Constraints Fle Text File Text File OK Cancel OK Cancel

建立顶层文件 2. 选择顶层文件类型

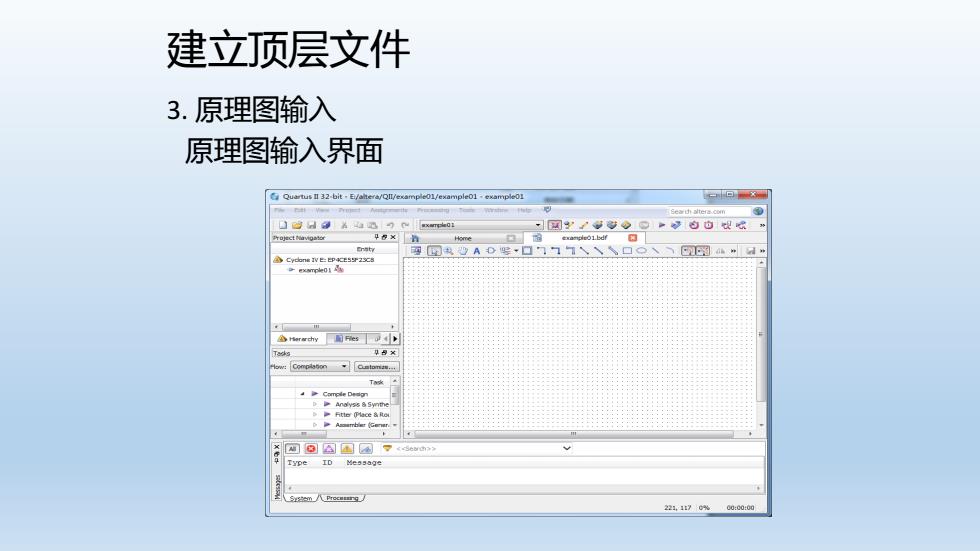

建立顶层文件 3.原理图输入 原理图输入界面 平8× Home rt × 可。@国国, Type ID Message 221,117c%00:00:00

建立顶层文件 3. 原理图输入 原理图输入界面

建立顶层文件 原理图器件调入界面 图Symbol Libraries: c:/aitera/13.1/quartus/braries/ p□megafunctiors prmitives buffer and12 and2 and3 and4 Name: and2 ☐Repeat-nsert mode □Insert symbol as blod Launch Megalizard Plug-In MegaWizard Pug-In Manoger

建立顶层文件 原理图器件调入界面

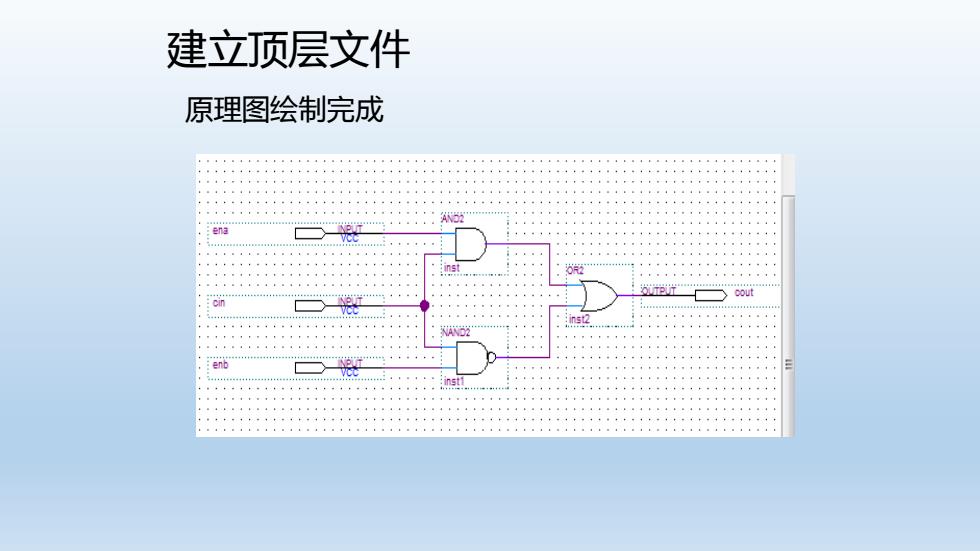

建立顶层文件 原理图绘制完成 ena , 0u cin 2 enb

建立顶层文件 原理图绘制完成

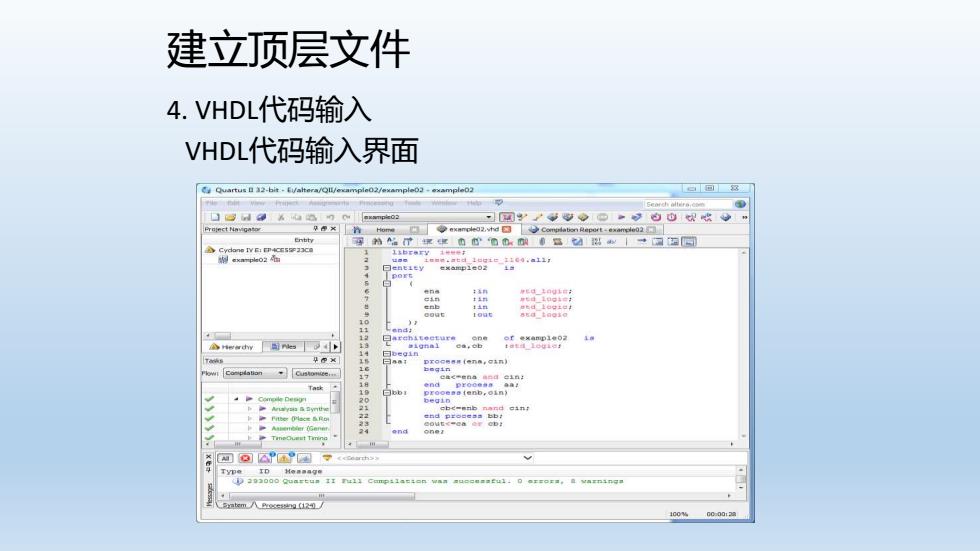

建立顶层文件 4.VHDL代码输入 VHDL代码输入界面 Quartus B32-bir 可国◆◆巴·白⊙以gw 母粉a了家g由心0心0意☑私1同 enb 10 rperdyyi nies Ta end cbe-enb 5atem人a2 00001

建立顶层文件 4. VHDL代码输入 VHDL代码输入界面