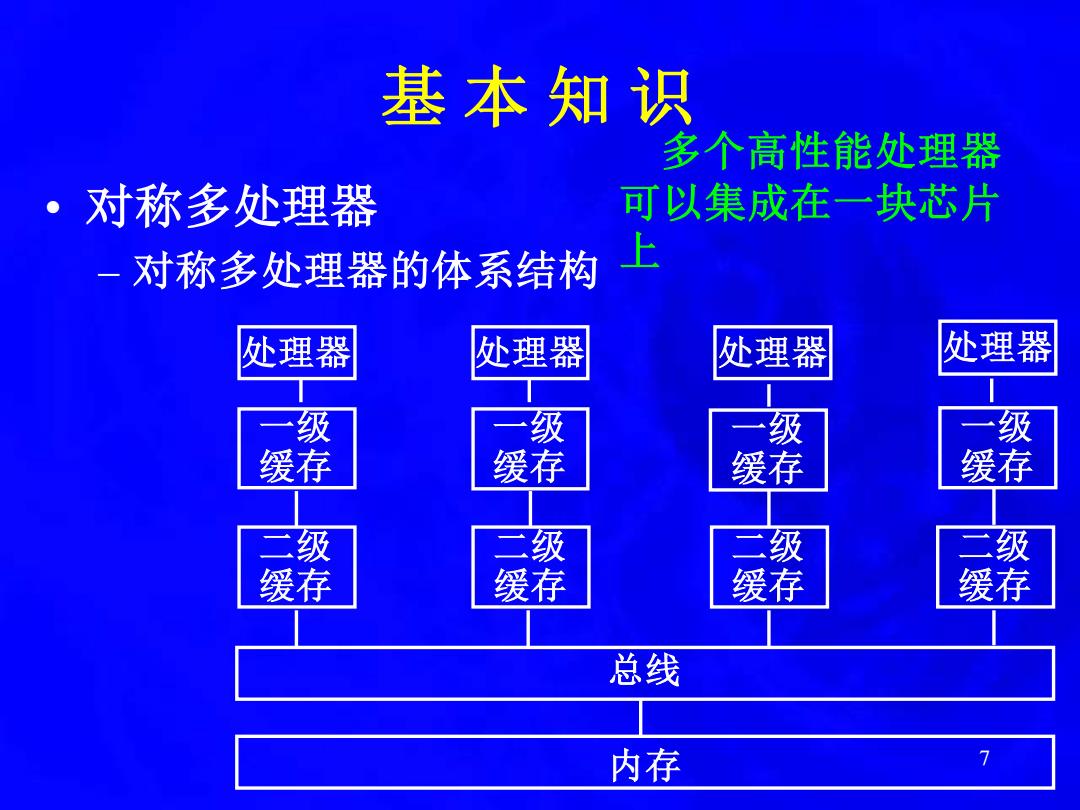

基本知识 个高性能处理器 ·对称多处理器 可以集成在一块芯片 -对称多处理器的体系结构 上 处理器 处理器 处理器 处理器 一级 级 一级 缓存 缓 缓 缓存 二级 二级 缓存 缓存 爱 二级 缓存 总线 内存 7

• 对称多处理器 – 对称多处理器的体系结构 二级 缓存 内存 总线 二级 缓存 二级 缓存 二级 缓存 一级 缓存 一级 缓存 一级 缓存 一级 缓存 处理器 处理器 处理器 处理器 基 本 知 识 多个高性能处理器 可以集成在一块芯片 上 7

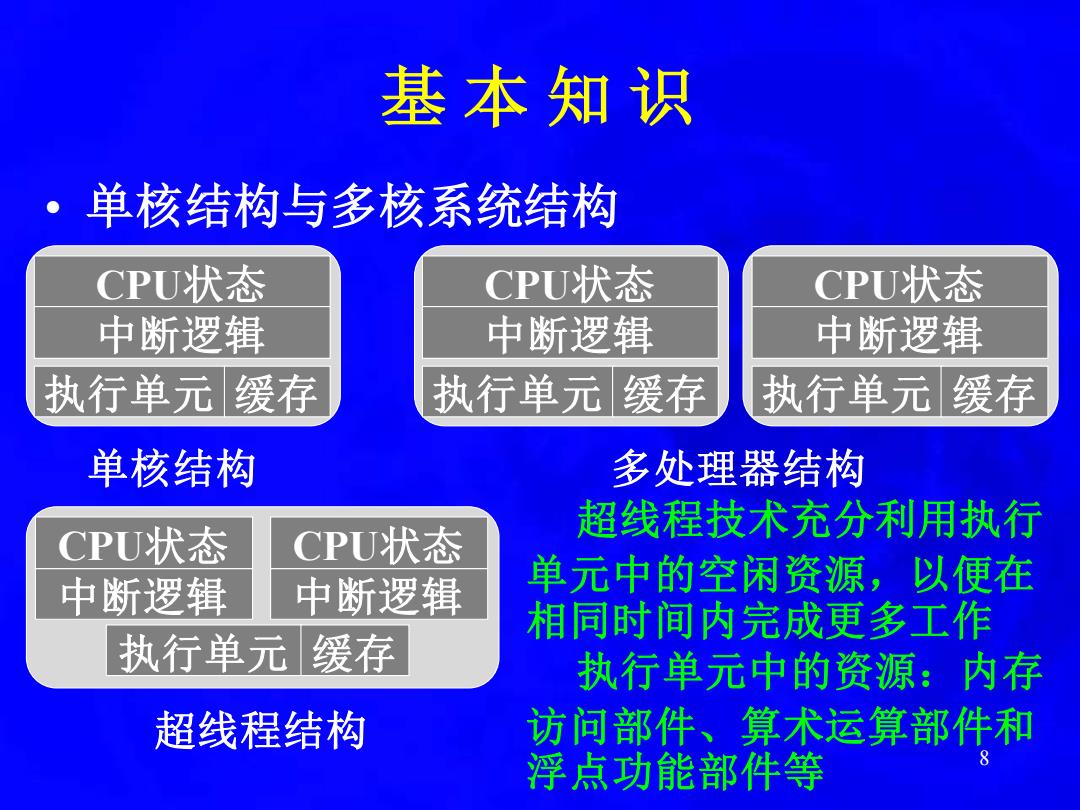

基本知识 单核结构与多核系统结构 CPU状态 CPU状态 CPU状态 中断逻辑 中断逻辑 中断逻辑 执行单元缓存 执行单元缓存 执行单元缓存 单核结构 多处理器结构 超线程技术充分利用执行 CPU状态 CPU状态 中断逻辑 中断逻辑 单元中的空闲资源,以便在 相同时间内完成更多工作 执行单元缓存 执行单元中的资源:内存 超线程结构 访问部件、算术运算部件和 浮点功能部件等

基 本 知 识 • 单核结构与多核系统结构 执行单元 缓存 CPU状态 中断逻辑 执行单元 缓存 CPU状态 中断逻辑 执行单元 缓存 CPU状态 中断逻辑 单核结构 多处理器结构 执行单元 缓存 CPU状态 中断逻辑 CPU状态 中断逻辑 超线程结构 超线程技术充分利用执行 单元中的空闲资源,以便在 相同时间内完成更多工作 执行单元中的资源:内存 访问部件、算术运算部件和 浮点功能部件等 8

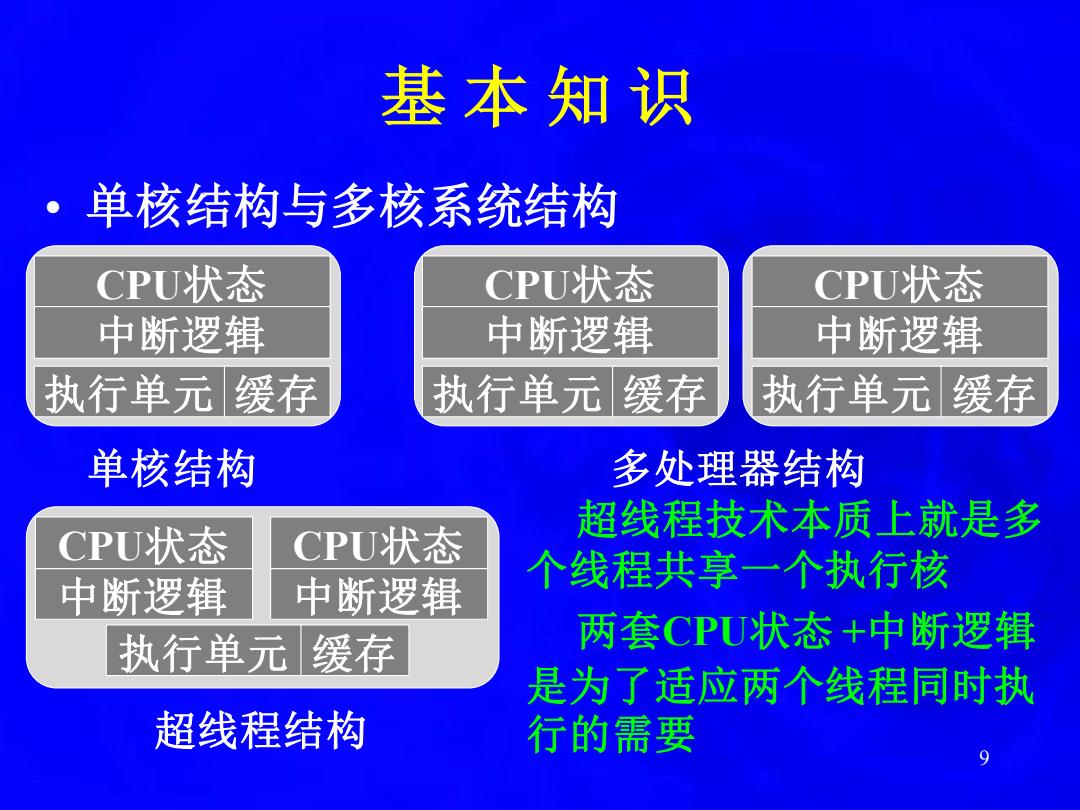

基本知识 单核结构与多核系统结构 CPU状态 CPU状态 CPU状态 中断逻辑 中断逻辑 中断逻辑 执行单元缓存 执行单元缓存 执行单元缓存 单核结构 多处理器结构 超线程技术本质上就是多 CPU状态 CPU状态 个线程共享一个执行核 中断逻辑 中断逻辑 执行单元缓存 两套CPU状态+中断逻辑 是为了适应两个线程同时执 超线程结构 行的需要

基 本 知 识 • 单核结构与多核系统结构 执行单元 缓存 CPU状态 中断逻辑 执行单元 缓存 CPU状态 中断逻辑 执行单元 缓存 CPU状态 中断逻辑 单核结构 多处理器结构 执行单元 缓存 CPU状态 中断逻辑 CPU状态 中断逻辑 超线程结构 超线程技术本质上就是多 个线程共享一个执行核 两套CPU状态 +中断逻辑 是为了适应两个线程同时执 行的需要 9

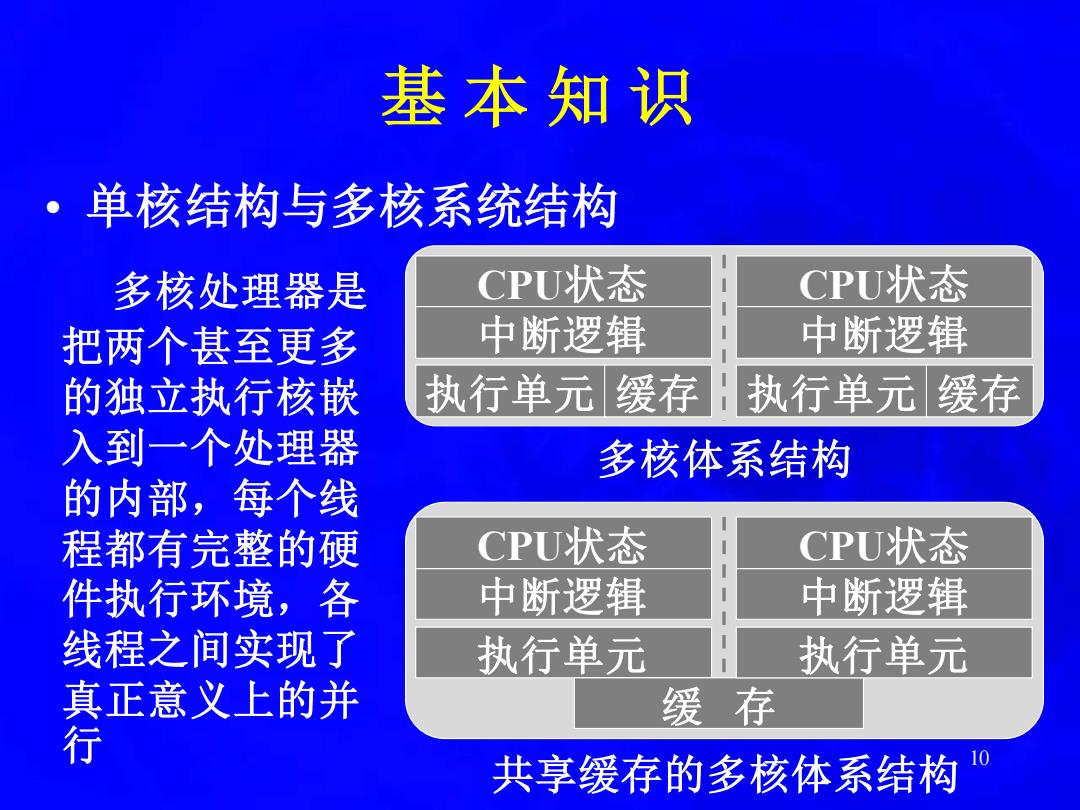

基本知识 ·单核结构与多核系统结构 多核处理器是 CPU状态 CPU状态 把两个甚至更多 中断逻辑 中断逻辑 的独立执行核嵌 执行单元缓存 执行单元缓存 入到一个处理器 多核体系结构 的内部,每个线 程都有完整的硬 CPU状态 CPU状态 件执行环境,各 中断逻辑 中断逻辑 线程之间实现了 执行单元 执行单元 真正意义上的并 缓存 行 共享缓存的多核体系结构 10

基 本 知 识 • 单核结构与多核系统结构 共享缓存的多核体系结构 执行单元 缓存 CPU状态 中断逻辑 执行单元 缓存 CPU状态 中断逻辑 多核体系结构 执行单元 缓 存 CPU状态 中断逻辑 执行单元 CPU状态 中断逻辑 多核处理器是 把两个甚至更多 的独立执行核嵌 入到一个处理器 的内部,每个线 程都有完整的硬 件执行环境,各 线程之间实现了 真正意义上的并 行 10

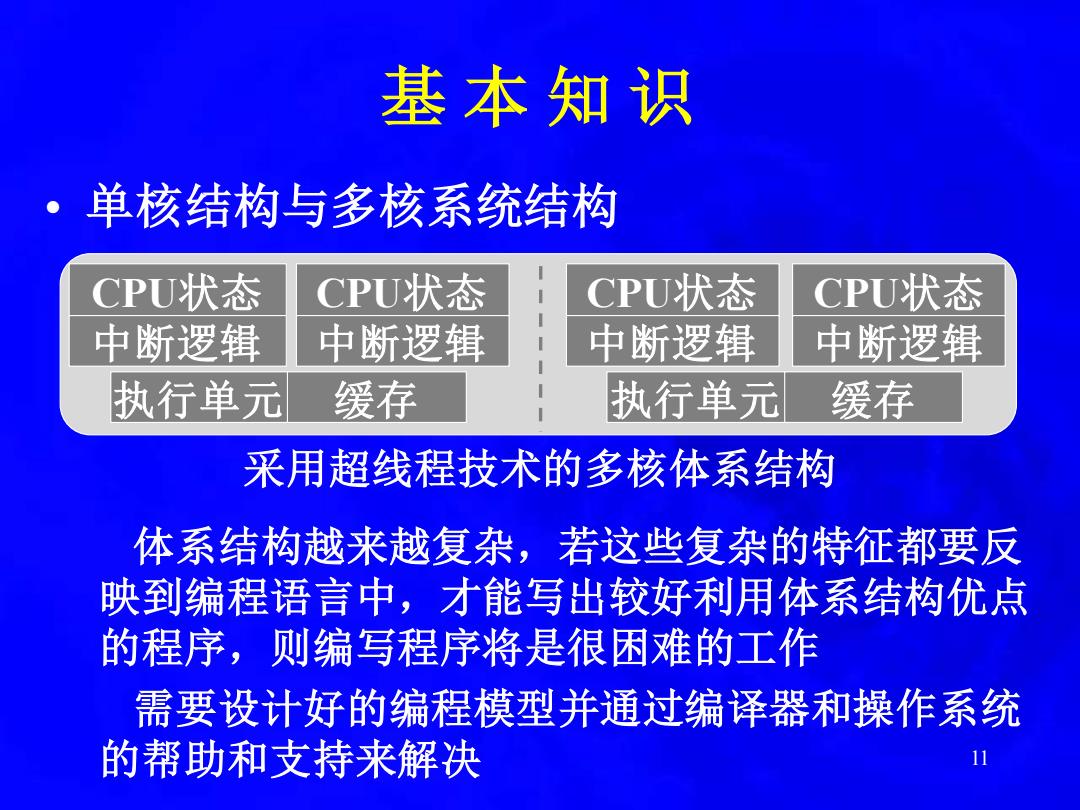

基本知识 ·单核结构与多核系统结构 CPU状态 CPU状态 CPU状态 CPU状态 中断逻辑 中断逻辑 中断逻辑 中断逻辑 执行单元 缓存 执行单元 缓存 采用超线程技术的多核体系结构 体系结构越来越复杂,若这些复杂的特征都要反 映到编程语言中,才能写出较好利用体系结构优点 的程序,则编写程序将是很困难的工作 需要设计好的编程模型并通过编译器和操作系统 的帮助和支持来解决

基 本 知 识 • 单核结构与多核系统结构 体系结构越来越复杂,若这些复杂的特征都要反 映到编程语言中,才能写出较好利用体系结构优点 的程序,则编写程序将是很困难的工作 需要设计好的编程模型并通过编译器和操作系统 的帮助和支持来解决 采用超线程技术的多核体系结构 执行单元 缓存 CPU状态 中断逻辑 CPU状态 中断逻辑 执行单元 缓存 CPU状态 中断逻辑 CPU状态 中断逻辑 11