第十章 依赖于机器的优化 在指令级并行的机器上,程序的运行速度依 赖于下面几个因素 程序中潜在的并行 处理器上可用的并行 从串行程序提取并行的能力 在给定的调度约束下发现最佳并行调度的能力 并行的提取和并行执行的调度都可以静态地 在软件中或动态地在硬件中完成

第十章 依赖于机器的优化 • 在指令级并行的机器上,程序的运行速度依 赖于下面几个因素 – 程序中潜在的并行 – 处理器上可用的并行 – 从串行程序提取并行的能力 – 在给定的调度约束下发现最佳并行调度的能力 • 并行的提取和并行执行的调度都可以静态地 在软件中或动态地在硬件中完成

第十章 依赖于机器的优化 本章内容 使用指令级并行的基础问题 提取并行的数据相关性分析 代码调度的基本概念 基本块调度的技术、发现通用程序中的高度数据 相关控制流的方法、调度数值程序的软件流水线 技术 在多处理器系统上,使用数组的计算密集型程序 的并行化和数据局部性优化的概念和方法

第十章 依赖于机器的优化 • 本章内容 – 使用指令级并行的基础问题 – 提取并行的数据相关性分析 – 代码调度的基本概念 – 基本块调度的技术、发现通用程序中的高度数据 相关控制流的方法、调度数值程序的软件流水线 技术 – 在多处理器系统上,使用数组的计算密集型程序 的并行化和数据局部性优化的概念和方法

10.1处理器体系结构 在考虑指令级并行时,通常想象成一个处理 器在单个时钟周期内发射几个操作 事实上,在每周期内发射一个操作是可能的: 而指令级并行的获得是通过使用流水线技术 本节先解释流水线,然后讨论多指令发射

10.1 处理器体系结构 • 在考虑指令级并行时,通常想象成一个处理 器在单个时钟周期内发射几个操作 • 事实上,在每周期内发射一个操作是可能的, 而指令级并行的获得是通过使用流水线技术 • 本节先解释流水线,然后讨论多指令发射

10.1处理器体系结构 10.1.1指令流水线和分支延迟 i+1 i+2 i+3 i+4 1. F 5级指令流水线中 2. D F 的5条连续指令 3. EX D 4. MEM EX D 5. WB MEM EX 6. WB MEM EX D 7. WB MEM EX 8. 取指令F,译码D,执行操作EX, WB MEM 9. 访问内存MEM,回写结果WB WB

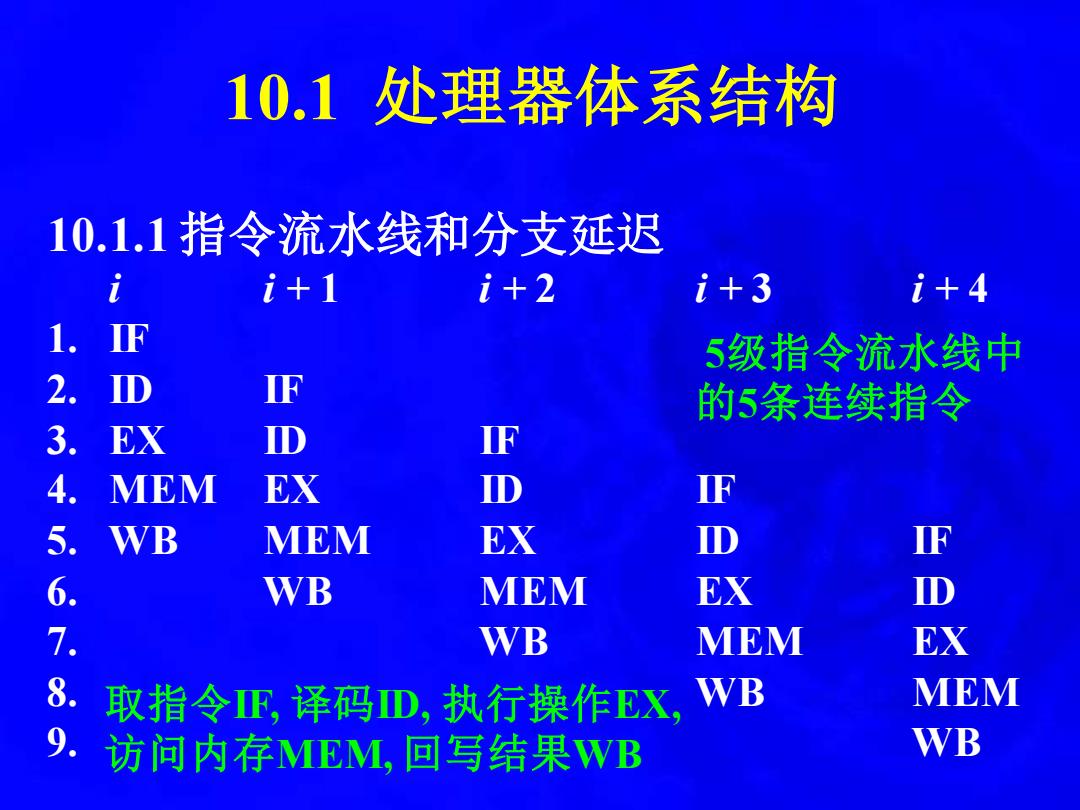

10.1 处理器体系结构 10.1.1 指令流水线和分支延迟 i i + 1 i + 2 i + 3 i + 4 1. IF 2. ID IF 3. EX ID IF 4. MEM EX ID IF 5. WB MEM EX ID IF 6. WB MEM EX ID 7. WB MEM EX 8. WB MEM 9. WB 取指令IF, 译码ID, 执行操作EX, 访问内存MEM, 回写结果WB 5级指令流水线中 的5条连续指令

10.1处理器体系结构 10.1.1指令流水线和分支延迟 分支延迟 发现应该执行一个分支而不是直接后继 转向一个分支时会引起取分支目的地址指令的延 迟并引起指令流水线“打嗝” 可以通过使用硬件,根据分支的执行历史来预测 分支结果并从预测的目的地址预取指令 分支延迟不可避免,因为分支预测会发生偏差

10.1 处理器体系结构 10.1.1 指令流水线和分支延迟 • 分支延迟 – 发现应该执行一个分支而不是直接后继 – 转向一个分支时会引起取分支目的地址指令的延 迟并引起指令流水线“打嗝” – 可以通过使用硬件,根据分支的执行历史来预测 分支结果并从预测的目的地址预取指令 – 分支延迟不可避免,因为分支预测会发生偏差