(1)82C55一可编程的通用并行接口电路(3个8位V0口); (2)81C55一可编程的1O/RAM扩展接口电路(2个8位/O口, 1个6位VO口,256个RAM字节单元,1个14位的减法计数器)。 它们都可以和AT89S52单片机直接连接,且接口逻辑十分简 单。本章仅介绍AT89S52单片机扩展VO接口芯片82C55的设计。 11

11 (1)82C55—可编程的通用并行接口电路(3个8位I/O口); (2)81C55—可编程的IO/RAM扩展接口电路(2个8位I/O口, 1个6位I/O口,256个RAM字节单元,1个14位的减法计数器)。 它们都可以和AT89S52单片机直接连接,且接口逻辑十分简 单。本章仅介绍AT89S52单片机扩展I/O接口芯片82C55的设计

9.2AT89S51扩展VO接口芯片82C55的设计 本节首先简要介绍可编程并行VO接口芯片82C55的应用特 性,然后介绍AT89S52单片机与82C55的接口电路设计以及 软件设计。 9.2.182C55芯片简介 82C55是Intel公司生产的可编程并行Vo接口芯片,它具有 3个8位的并行VO口,3种工作方式,可通过编程改变其功能, 因而使用灵活方便,可作为单片机与多种外围设备连接时的中 间接口电路。82C55的引脚及内部结构如图9-1和图9-2所示。 12

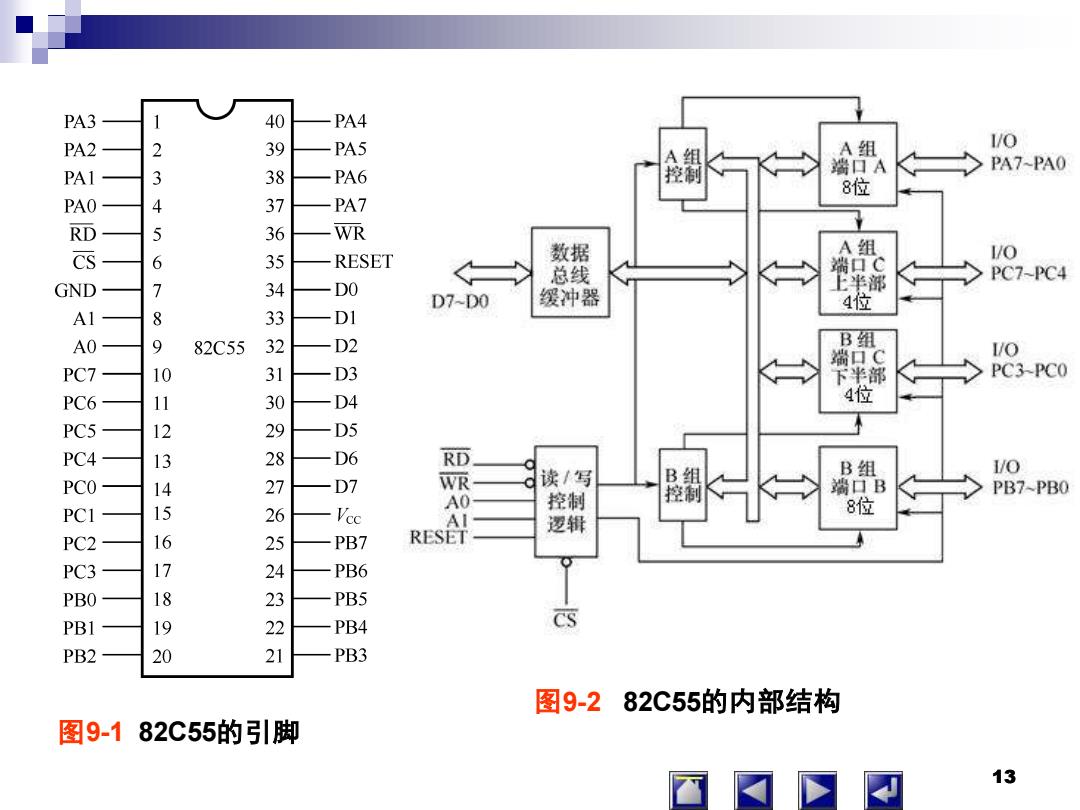

12 9.2 AT89S51扩展I/O接口芯片82C55的设计 本节首先简要介绍可编程并行I/O接口芯片82C55的应用特 性,然后介绍AT89S52单片机与82C55的接口电路设计以及 软件设计。 9.2.1 82C55芯片简介 82C55是Intel公司生产的可编程并行I/O接口芯片,它具有 3个8位的并行I/O口,3种工作方式,可通过编程改变其功能, 因而使用灵活方便,可作为单片机与多种外围设备连接时的中 间接口电路。82C55的引脚及内部结构如图9-1和图9-2所示。 12

PA3 40 PA4 PA2 2 39 PA5 A组 I/O A组 控制 端口A PA7-PAO PA1 3 38 PA6 8位 PAO 4 31 PA7 RD 5 36 W丞 A组 cs 35 RESET 数据 VO 6 总线 端口C PC7-PC4 GND 个 34 DO 上半部 D7-D0 缓冲器 4位 Al 8 33 DI A0 9 82C55 9 D2 B组 端口C PC7 10 D3 下半部 PC3-PCO PC6 11 12 13029 D4 4位 PC5 D5 PC4 13 2 D6 RD B组 1O PCO 14 27 D7 W 读/写 B 控制 端口B PB7-PBO 15 26 Vee A0 控制 PC1 8位 逻辑 PC2 16 25 PB7 RESET PC3 17 24 PB6 PBO 18 PB5 PB1 19 22 PB4 CS PB2 20 21 PB3 图9-282C55的内部结构 图9-182C55的引脚 13

13 图 9 - 1 82C55的引脚 图 9 - 2 82 C55的内部结构

1.引脚说明 由图91可知,82C55共有40个脚,采用双列直插式封装, 各引脚功能如下。 D7~D0:三态双向数据线,与单片机的P0口连接,用来与单 片机之间传送数据信息。 CS*:片选信号线,低电平有效,表示本芯片被选中。 RD*:读信号线,用来读出82C55端口数据的控制信号。 WR*:写信号线,用来向82C55写入端口数据的控制信号。 Vcc:+5V电源。 14

14 1.引脚说明 由图9-1可知,82C55共有40个引脚,采用双列直插式封装, 各引脚功能如下。 D7~D0:三态双向数据线,与单片机的P0口连接,用来与单 片机之间传送数据信息。 CS*:片选信号线,低电平有效,表示本芯片被选中。 RD*:读信号线,用来读出82C55端口数据的控制信号。 WR*:写信号线,用来向82C55写入端口数据的控制信号。 Vcc:+5V电源

PA7~PA0:端口A输入/输出线。 PB7~PB0:端口B输入/输出线。 PC7~PC0:端口C输入/输出线。 A1、A0:地址线,用来选择82C55内部的4个端口。 RESET:复位引脚,高电平有效。 2.内部结构 82C55内部结构见图9-2,包括3个并行数据输入输出端口, 两种工作方式的控制电路,一个读/写控制逻辑电路和一个8位 数据总线缓冲器。图9-2中左侧的引脚与单片机相连,右侧的引 脚与外设连接。各部件的功能如下。 15

15 PA7~PA0:端口A输入/输出线。 PB7~PB0:端口B输入/输出线。 PC7~PC0:端口C输入/输出线。 A1、A0:地址线,用来选择82C55内部的4个端口。 RESET:复位引脚,高电平有效。 2.内部结构 82C55内部结构见图9-2,包括3个并行数据输入/输出端口, 两种工作方式的控制电路,一个读/写控制逻辑电路和一个8位 数据总线缓冲器。图9-2中左侧的引脚与单片机相连,右侧的引 脚与外设连接。各部件的功能如下