3数字频率计的设计 设计要求 设计一个能测量方波信号频率的频率计,测量结果用十进制数显示 2.测量的频率范围是1~10KHz,分成两个频段,即1~999H2,1KH210KHz,用三 位数码管显示测量频率,用LED显示表示单位,如亮绿灯表示Hz,亮红灯表示 KHz。 3且有白动验和刚品两种功能,即能用标准时钟炒验侧品结度 4.具有超量程报警功能,在超出目前量程档的测量范围时,发出灯光和音响信号。 单位显 陆存器 LD E 图1颜率计系统框图。 设计提示 ●脉冲信号的频率就是在单位时间内所产生的脉冲个数,其表达式为=NT,f 为被测信号的频率,N为计数器所累计的脉冲个数,T为产生N个脉冲所需 的时间。所以,在1秒时间内计数器所记录的结果,就是被测信号的频率。 ·测量校验选择模块* 计数器模块 ·送存选择报警模块 ·锁存模块 。扫描显示模块 。测量校验选择模块* 输入信号:选择信号selet被测信号meas测试信号test 输出信号:CP1 当selet=-0时,为测量状态,CPI=meas: 当selet=1时,为校验状态,CPI=test。 校验与测量共用一个电路,只是被测信号CP1不同而已。 少定时信号(周期为2秒),在1秒定时时间内的所有被测信号送计数 器输入端。 ·计数器对CP1信号进行计数,在1秒定时结束后,将计数器结果送锁存器锁

3 数字频率计的设计 设计要求 1.设计一个能测量方波信号频率的频率计,测量结果用十进制数显示。 2. 测量的频率范围是 110KHz,分成两个频段,即 1999Hz,1KHz10KHz,用三 位数码管显示测量频率,用 LED 显示表示单位,如亮绿灯表示 Hz,亮红灯表示 KHz。 3. 具有自动校验和测量两种功能,即能用标准时钟校验测量精度。 4. 具有超量程报警功能,在超出目前量程档的测量范围时,发出灯光和音响信号。 设计提示 ⚫ 脉冲信号的频率就是在单位时间内所产生的脉冲个数,其表达式为 f=N/T,f 为被测信号的频率,N 为计数器所累计的脉冲个数,T 为产生 N 个脉冲所需 的时间。所以,在 1 秒时间内计数器所记录的结果,就是被测信号的频率。 ⚫ 测量/校验选择模块* ⚫ 计数器模块 ⚫ 送存选择报警模块 ⚫ 锁存模块 ⚫ 扫描显示模块 ⚫ 测量/校验选择模块* 输入信号:选择信号 selet 被测信号 meas 测试信号 test 输出信号:CP1 当 selet=0 时,为测量状态,CP1=meas; 当 selet=1 时,为校验状态,CP1=test。 校验与测量共用一个电路,只是被测信号 CP1 不同而已。 ⚫ 设置 1 秒定时信号(周期为 2 秒),在 1 秒定时时间内的所有被测信号送计数 器输入端。 ⚫ 计数器对 CP1 信号进行计数,在 1 秒定时结束后,将计数器结果送锁存器锁

存,同时将计数器清零,为下一次采样测量做好准备。 ●设置量程档控制开关K,单位显示信号Y,当K=0时,为1~999Hz量程档 数码管显示的数值为被测信号频率值,Y显示绿色,即单位为H2:当K=1 时, 0KHz量程档,被测信号频率值为数码管显示的数值乘1000 即单位为KHz。 。设置超出量程档测量范围示警信号alert。计数器由四级十进制计数构成(带 进位C)。若被测信号频率小于1KHz(K=O),则计数器只进行三级十进制计 数,最大显示值为999.Hz,如果被测信号频率超过此范围,示警信号驱动灯 光、扬声器报警:若被测信号为1KHz10KH2(K=1),计数器进行四位十进 制计数,取高三位显示,最大显示值为9.99水Hz,如果被测信号频率超过此 范围,报警。 alert 单位显示 1Hz时钟源 被测信号 FPGA/CPLD meas 标准时钟 test k select % 购2 图2数字频率计硬件系統示意图 设计文档 一是的原归结成一句活,即在单位时间内对号进行计数。下图说 测频的原理及误差产生的原因。 Π几ΠΠ几几几 丢失(少一个腺冲) 计到7个脉冲 (比际密0x个条冲神) 图1测频的原理 在上图中,假设时基信号为1khz,则用此法测得待测信号为1khz*7=70kh2。但

存,同时将计数器清零,为下一次采样测量做好准备。 ⚫ 设置量程档控制开关 K,单位显示信号 Y,当 K=0 时,为 1999Hz 量程档, 数码管显示的数值为被测信号频率值,Y 显示绿色,即单位为 Hz;当 K=1 时,为 1KHz10KHz 量程档,被测信号频率值为数码管显示的数值乘 1000, Y 显示红色,即单位为 KHz。 ⚫ 设置超出量程档测量范围示警信号 alert。计数器由四级十进制计数构成(带 进位 C)。若被测信号频率小于 1KHz(K=0),则计数器只进行三级十进制计 数,最大显示值为 999.Hz,如果被测信号频率超过此范围,示警信号驱动灯 光、扬声器报警;若被测信号为 1KHz10KHz(K=1),计数器进行四位十进 制计数,取高三位显示,最大显示值为 9.99KHz,如果被测信号频率超过此 范围,报警。 设计文档 一、原理 测频的原理归结成一句话,即在单位时间内对被测信号进行计数。下图说明了 测频的原理及误差产生的原因。 图 1 测频的原理 在上图中,假设时基信号为 1khz,则用此法测得待测信号为 1khz*7=70khz。但

从图中可以看出,待测信号应该在77kz,误差约为777~9.1%。这个误差是比较大 的,实际上,测量的脉冲个数的误差会在±1间。假设所测得脉冲个数为,则所测 频率的最大误差为1/(n-1)*100%。显然,减小误差的方法就是增大n。本频率计 的要求测量结果以3位数表示,则测频误差应为1%0.1%,则的取值范围为: 100≤n<100 即时基信号的频率为量程中最低频率的1100(同时约为最高频率的11000)。通过 计算得出下表中的数据。 待测信号与时基信号的关系 待测信号hz 时基信号z 10-99.9 100 1-9.99 10 二、系统框图 分频器 各档时基信号 费想件号与 一发光二极管 状态机 七段数码管 一七股数码管 信号同步 译码电路 整形电路 锁存器 计数器 图2数字频率计系统框图 根据题意,各个模块的作用简述如下: 1、分频器:由于测频时不同量程需要不同的时基信号,分频模块是必不可少的

从图中可以看出,待测信号应该在 77khz,误差约为 7/77~9.1%。这个误差是比较大 的,实际上,测量的脉冲个数的误差会在 1 间。假设所测得脉冲个数为 n,则所测 频率的最大误差为 1/(n-1)*100%。显然,减小误差的方法就是增大 n。本频率计 的要求测量结果以 3 位数表示,则测频误差应为 1%~0.1%,则 n 的取值范围为: 100 n<100 即时基信号的频率为量程中最低频率的 1/100(同时约为最高频率的 1/1000)。通过 计算得出下表中的数据。 待测信号与时基信号的关系 待测信号/khz 时基信号/hz 10~99.9 100 1~9.99 10 二、系统框图 图 2 数字频率计系统框图 根据题意,各个模块的作用简述如下: 1、分频器:由于测频时不同量程需要不同的时基信号,分频模块是必不可少的

系统通过分频模块从晶振时钟(20Mz)分出系统所需要的几个时基信号,其中包 括状态机所需时钟。 2、计数器:从原理中可以看出,测频的本质上是计数,所以计数器也是系统中不 可或缺的模块。为实现量程的自动转换,本计数器需输出指示超量程和欠量程状态 的信是 3、状态机:题目要求本系统可以自动转换量程,如果把每个量程看成一个状态, 那么量程的切换实际上就是状态的转换。显然,用状态机来实现是最方便的。 4、其他:如锁存器(用来使显示数字稳定)、同步整形电路(用来处理超量程和欠 量程信号,避免状态机多次转移)和七段数码管译码电路等。 三、各功能模块的实现 1状态机的设计 系统的状态机是用来自动切换量程的。根据前面的分析,我们可以设立4个状 态,状态名及其对应的量程如下表所列 状态名 对应量程 时基信号州z F100K 10-99.9kHz 100 F10K 1-999kHz 10 OverError 超过数字频率计最高频率 100 LowError 低于数字频率计最低频率 10 假设计数器的超量程信号为over,欠量程信号为low,那么可以画出如下图所 示的状态转移图 图3状态转移图 根据此状态转移图,很容易就可以写出对应的状态机程序。状态机见附录1

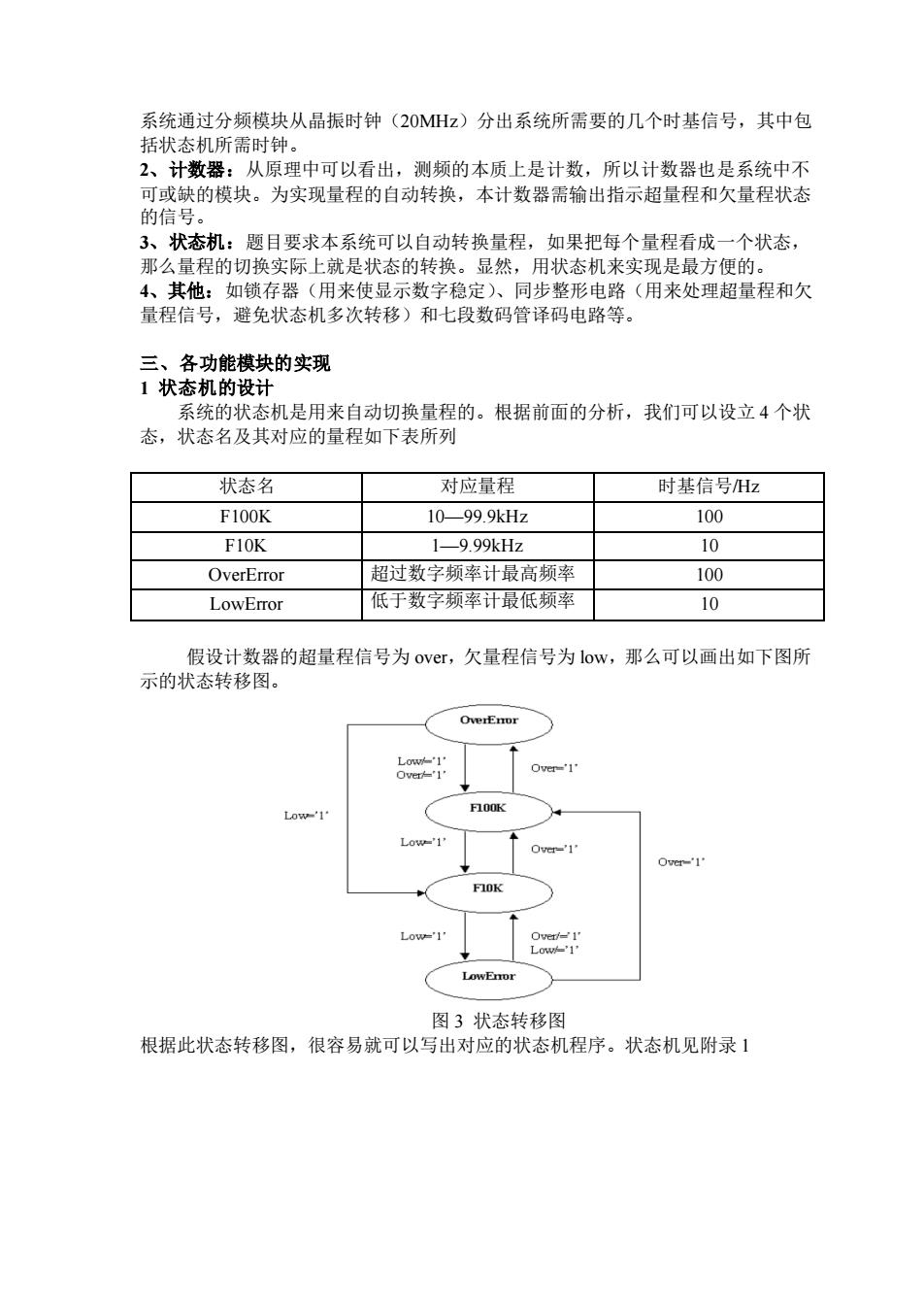

系统通过分频模块从晶振时钟(20MHz)分出系统所需要的几个时基信号,其中包 括状态机所需时钟。 2、计数器:从原理中可以看出,测频的本质上是计数,所以计数器也是系统中不 可或缺的模块。为实现量程的自动转换,本计数器需输出指示超量程和欠量程状态 的信号。 3、状态机:题目要求本系统可以自动转换量程,如果把每个量程看成一个状态, 那么量程的切换实际上就是状态的转换。显然,用状态机来实现是最方便的。 4、其他:如锁存器(用来使显示数字稳定)、同步整形电路(用来处理超量程和欠 量程信号,避免状态机多次转移)和七段数码管译码电路等。 三、各功能模块的实现 1 状态机的设计 系统的状态机是用来自动切换量程的。根据前面的分析,我们可以设立 4 个状 态,状态名及其对应的量程如下表所列 状态名 对应量程 时基信号/Hz F100K 10—99.9kHz 100 F10K 1—9.99kHz 10 OverError 超过数字频率计最高频率 100 LowError 低于数字频率计最低频率 10 假设计数器的超量程信号为 over,欠量程信号为 low,那么可以画出如下图所 示的状态转移图。 图 3 状态转移图 根据此状态转移图,很容易就可以写出对应的状态机程序。状态机见附录 1

图4状态机的仿真波形 2计数器的设计 计数器的原理很简单,计数值大于999,就将超量程信号Ovr置1:若计数值 小于100,则将欠量程信号Low置1。 本计数器在待计数信号的两个周期内完成计数与控制信号(Ov©r与Low)的 传输,在量程合适的情况下,将计数值输出。在这两个时钟周期内,第1个时钟周 期完成计数,第2个时钟周期完成控制信号的传输与计数值输出。这样做的好处是 稳定,将计数与控制信号传输分开进行,避免了时钟的跳变。 计数器的程序见附录2。 20ns 0s 60s -clack2 bw 号的 0T27305a7a9 0 O/nUmG 0020000a▣ numt 0 图5计数器仿真波形 3同步整形电路的设计 在实际应用中 外部输入的异步信号常常需要进行同步化(与系统时钟同步) 和整形(将输入信号整形为一个时钟周期长的信号脉冲),其波形图见图6。其 程序见附录3

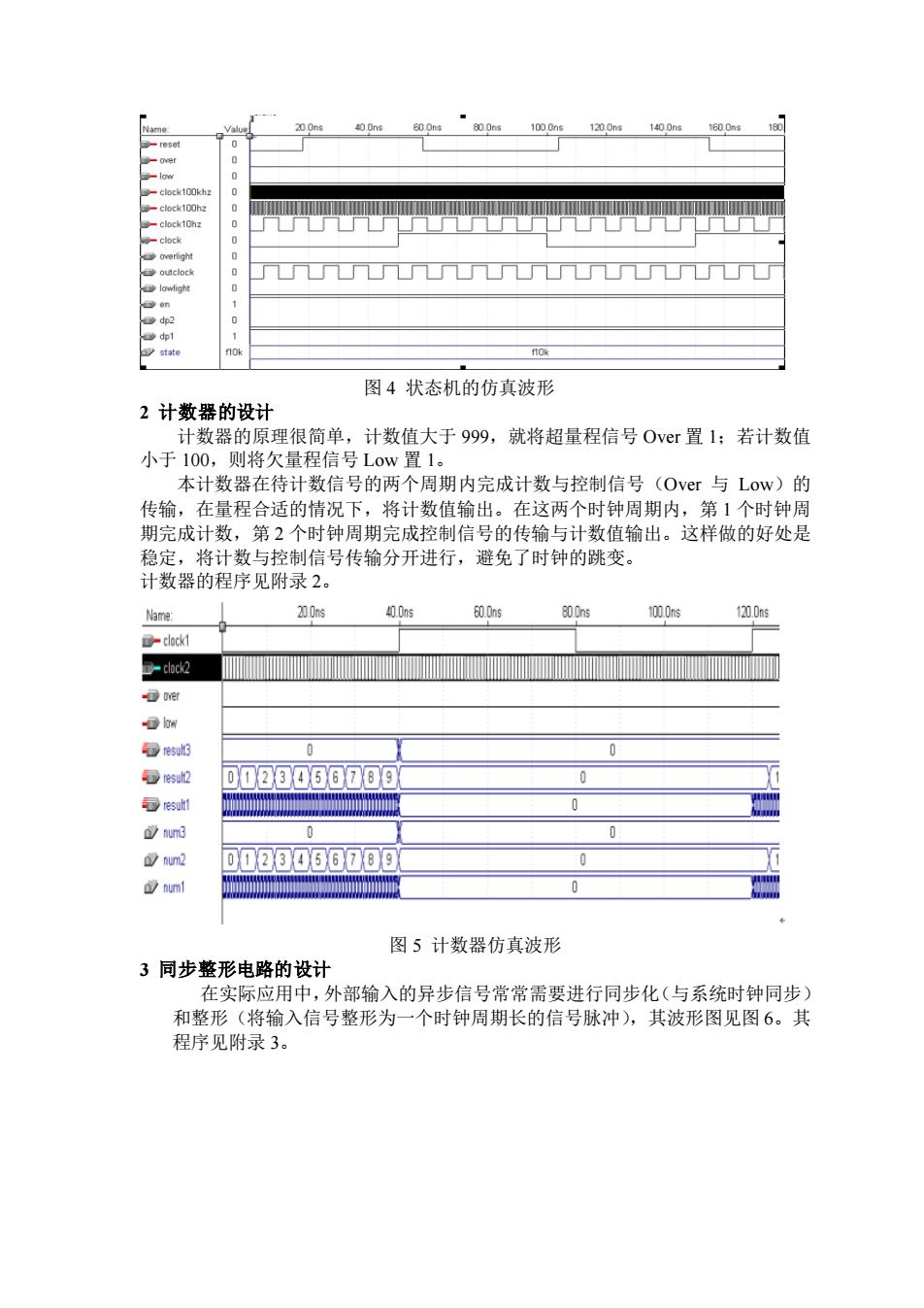

图 4 状态机的仿真波形 2 计数器的设计 计数器的原理很简单,计数值大于 999,就将超量程信号 Over 置 1;若计数值 小于 100,则将欠量程信号 Low 置 1。 本计数器在待计数信号的两个周期内完成计数与控制信号(Over 与 Low)的 传输,在量程合适的情况下,将计数值输出。在这两个时钟周期内,第 1 个时钟周 期完成计数,第 2 个时钟周期完成控制信号的传输与计数值输出。这样做的好处是 稳定,将计数与控制信号传输分开进行,避免了时钟的跳变。 计数器的程序见附录 2。 图 5 计数器仿真波形 3 同步整形电路的设计 在实际应用中,外部输入的异步信号常常需要进行同步化(与系统时钟同步) 和整形(将输入信号整形为一个时钟周期长的信号脉冲),其波形图见图 6。其 程序见附录 3