Name: Valu 500ns 100.0n 150.0ns signalin clock signalou 图6同步整形电路仿真波形 4分频器的设计 要得到状态机及各个功能模块所需的各种频率,就必须通过分频器从己知的 频率中得到,我们先实现了200分频和10分须,然后通过如下电路得到了所需 的频率: 速腿三南g udoha 图7分频器总图 10分频、200分频和分频模块的波形仿真如下: Name: 23s00s0s0s1msm0s10s1简0s1阅 oUUUUUUUUU 012345678901234567 图8十分频器仿真波形

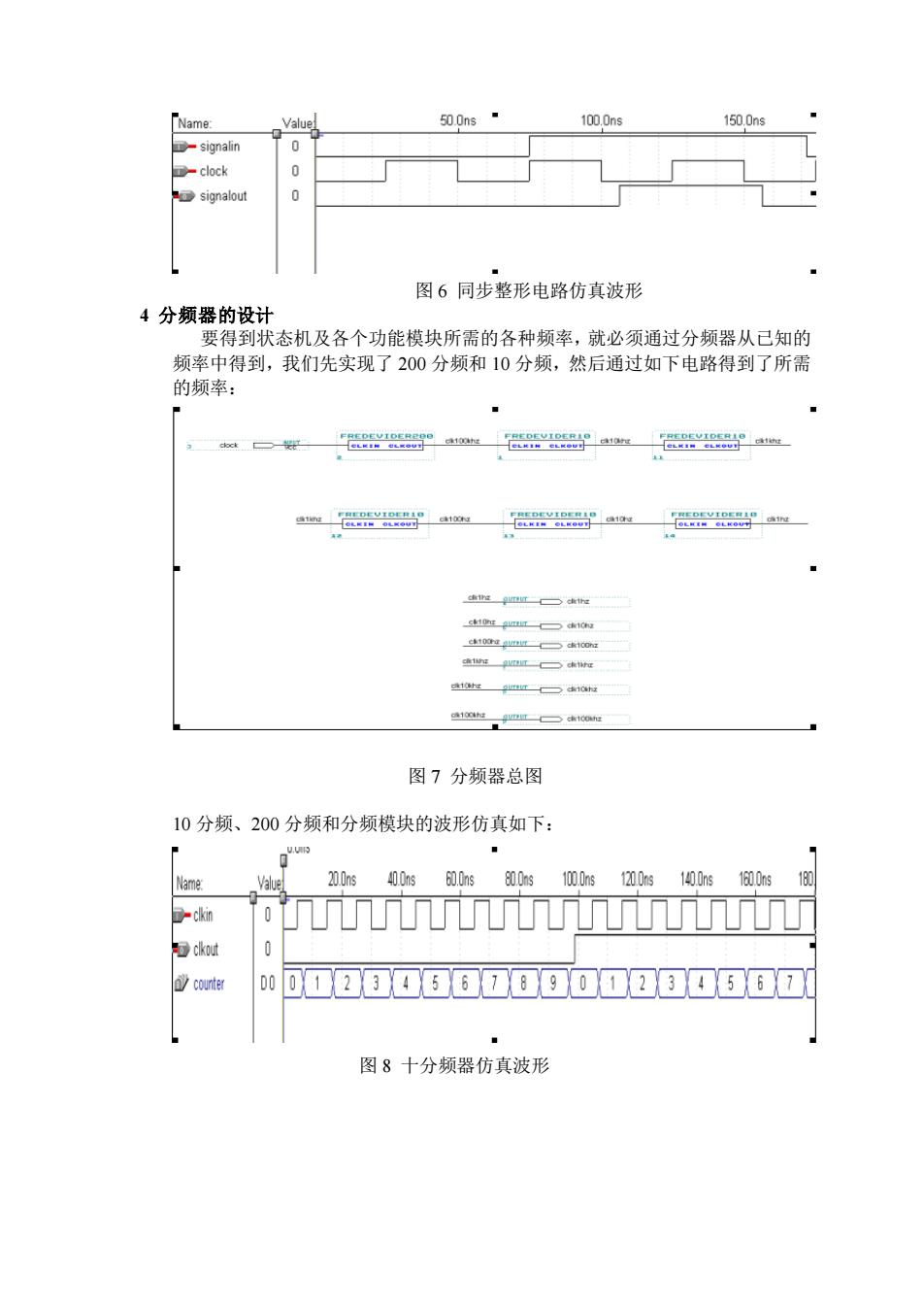

图 6 同步整形电路仿真波形 4 分频器的设计 要得到状态机及各个功能模块所需的各种频率,就必须通过分频器从已知的 频率中得到,我们先实现了 200 分频和 10 分频,然后通过如下电路得到了所需 的频率: 图 7 分频器总图 10 分频、200 分频和分频模块的波形仿真如下: 图 8 十分频器仿真波形

制ssms迎s阳s就0s做0ssg如s0sss】 TTTTTTT 0 丙无7刀网00m的8西国日丽的02阳网3第7阳丽 图9200分频仿真波形 100.ns 0s 300.0ns 400.0ns 50.0s 600.0ns 700.0ns B00.0ns 900.0 U @ckOk恒 Dch10h位 och恤 0 图10分频器模块仿真波形 10分频和200分频的程序见附录4。 5锁存器的设计 在本课题中,用的是一个正沿触发的D锁存器,它有一个数据输入端d, 一个 时钟输入端ck和 个数据输出端q。D锁存器的输出端只有在正脉冲沿过后,输入 端d的数据才传递到输出端q。用VHDL语言描述该D锁存器的程序见附录5。 上述D锁存器只是一个单输入输出的锁存器,通过元件例化将单输入输出的锁 存器扩张成3输入输出的锁存器。详见下图: 59 33 图11锁存器模块

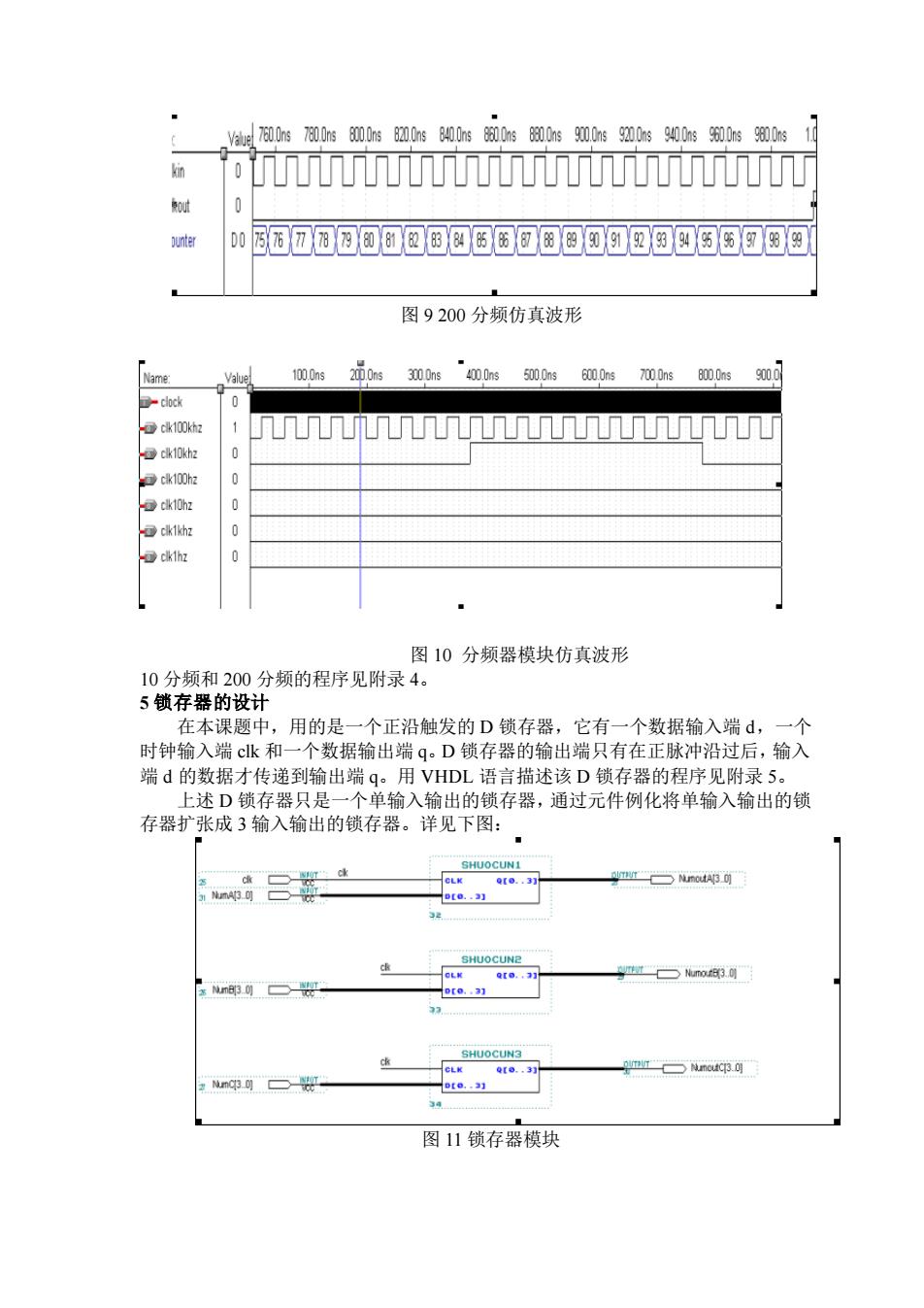

图 9 200 分频仿真波形 图 10 分频器模块仿真波形 10 分频和 200 分频的程序见附录 4。 5 锁存器的设计 在本课题中,用的是一个正沿触发的 D 锁存器,它有一个数据输入端 d,一个 时钟输入端 clk 和一个数据输出端 q。D 锁存器的输出端只有在正脉冲沿过后,输入 端 d 的数据才传递到输出端 q。用 VHDL 语言描述该 D 锁存器的程序见附录 5。 上述 D 锁存器只是一个单输入输出的锁存器,通过元件例化将单输入输出的锁 存器扩张成 3 输入输出的锁存器。详见下图: 图 11 锁存器模块