中国科学技术大学物理系微电子专业 金属半导体接触的势垒高度 当金属与半导体形成紧密接触时,在热平衡下两 种材料的费米能级必须相等。此外,真空能级必 须是连续的 对于这种理想的情况,势垒高度q中就是金属功 函数和半导体电子亲和能之差。对于理想的金属 分别与N型、P型半导体接触,其势垒高度为: qoen =g(on-x) 9中o=Eg-q(pm-X) 对给定的半导体,任何金属在n型衬底和p型 衬底上的势垒高度之和总等于Eg。 Eg=9中m+q9m Principle of Semiconductor Devices 2023/5/15 21

中国科学技术大学物理系微电子专业 2023/5/15 Monday 21 • 当金属与半导体形成紧密接触时,在热平衡下两 种材料的费米能级必须相等。此外,真空能级必 须是连续的。 • 对于这种理想的情况,势垒高度qфBn就是金属功 函数和半导体电子亲和能之差。对于理想的金属 分别与N型、P型半导体接触,其势垒高度为: ( ) q Bn q m ★ 金属半导体接触的势垒高度 ( ) q Bp Eg q m • 对给定的半导体,任何金属在n型衬底和p型 衬底上的势垒高度之和总等于Eg。 Eg q Bp q Bn Principle of Semiconductor Devices

中国科学技术大学物理系微电子专业 DaN =Oy-x OBp =Ee-ou+x N型半导体的内建电势为 V6=中m-中, 因此,其势垒高度还可以写成 Bn =Vbi+Vn 其中qV为半导体的导带底和费米能级之差 Principle of Semiconductor Devices 2023/5/15 22

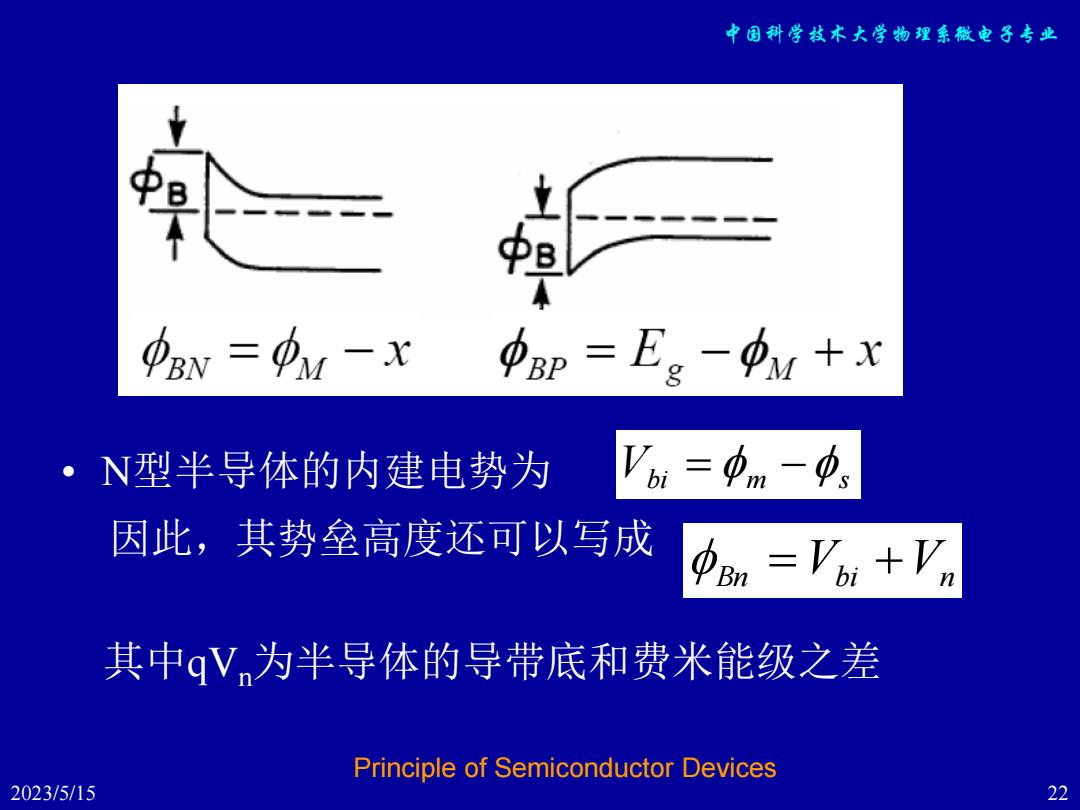

中国科学技术大学物理系微电子专业 2023/5/15 Monday 22 • N型半导体的内建电势为 因此,其势垒高度还可以写成 其中qVn为半导体的导带底和费米能级之差 Bn Vbi Vn Vbi m s Principle of Semiconductor Devices

中国科学技术大学物理系微电子专业 5、金属半导体接触的电容特性 金属与型半导体接触,金属一侧有负表面电荷, 半导体一侧存在等量的但极性相反的正空间电荷。 这种电荷分布和具有同样电场分布的P+N结完全 相同,由此得到半导体表面耗尽层宽度为: 28s (W-V) 金属相对n型半导体加正电压(正向偏置)时,上 式中外加电压V取正值;金属相对n型半导体加负 电压即反向偏置时,外加电压V取负值。 Principle of Semiconductor Devices 2023/5/15 23

中国科学技术大学物理系微电子专业 2023/5/15 Monday 23 5、 金属半导体接触的电容特性 • 金属与n型半导体接触,金属一侧有负表面电荷, 半导体一侧存在等量的但极性相反的正空间电荷。 这种电荷分布和具有同样电场分布的P + -N结完全 相同,由此得到半导体表面耗尽层宽度为: • 金属相对n型半导体加正电压(正向偏置)时,上 式中外加电压V取正值;金属相对n型半导体加负 电压即反向偏置时,外加电压V取负值。 ( ) 2 V V qN W bi D S Principle of Semiconductor Devices

中国科学技术大学物理系微电子专业 半导体内单位面积的空间电荷QsC (C/cm2) 和单位面积耗尽层电容C(F/cm)可表示为: Osc qNDW =2qN DEs(Vhi -V) qNDEs 或者 2(W-V) av 2(W-) qNDEs 即通过测量金半接触的C一V曲线,即 可得到杂质分布 Np- 2 Principle of Semiconductor Devices 2023/5/15 24

中国科学技术大学物理系微电子专业 2023/5/15 Monday 24 • 半导体内单位面积的空间电荷QSC(C/cm2) 和单位面积耗尽层电容C(F/cm2)可表示为: Q qN W 2qN (V V) SC D D S bi V V W qN V Q C S bi SC D S 2( ) D S bi qN V V C 1 2( ) 2 即通过测量金半接触的C-V曲线,即 可得到杂质分布 或者 ] (1/ )/ 1 [ 2 2 q d C dV N S D Principle of Semiconductor Devices

中国科学枝术大学物理系微电子专业 6、表面态对势垒高度的影响 理论上,金属一边的势垒高度 qφsB=qφns=Wm-X 但实际上,①$常常与金属的种类关系不太大,而 主要取决于表面态(界面态)的影响 n型Si和n型GaAs的势垒高度测量值显示,ΦBn随Wm 的增大而增大,但不是直线,这是因为在实际的金 属半导体接触中,由于晶格不连续,在接触界面处 产生大量的能量状态,这些能量状态叫做界面态或 表面态,它们连续分布在禁带内,可能起施主或受 主作用,影响势垒高度的实际值,对Si和GaAs,n 型势垒高度被低估,p型势垒高度被高估。 Principle of Semiconductor Devices 2023/5/15 25

中国科学技术大学物理系微电子专业 2023/5/15 Monday 25 6、表面态对势垒高度的影响 • 理论上, 金属一边的势垒高度 qΦ SB = qΦ ns = Wm –χ • 但实际上, Φ SB常常与金属的种类关系不太大,而 主要取决于表面态(界面态)的影响。 n型Si和n型GaAs的势垒高度测量值显示,Φ Bn随Wm 的增大而增大,但不是直线,这是因为在实际的金 属半导体接触中,由于晶格不连续,在接触界面处 产生大量的能量状态,这些能量状态叫做界面态或 表面态,它们连续分布在禁带内,可能起施主或受 主作用,影响势垒高度的实际值,对Si和GaAs,n 型势垒高度被低估,p型势垒高度被高估。 Principle of Semiconductor Devices