中国科学技术大学物理系微电子专业 第六章:新型半导体器件 §6.1现代MOS器件 §6.2CCD器件 §6.3存储器件 §6.4纳米器件 §6.5功率器件 §6.6微波器件 §6.7光电子器件 §6.8量子器件 Principle of Semiconductor Devices 2022/12/25

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 1 第六章: 新型半导体器件 §6.1 现代MOS器件 §6.2 CCD器件 §6.3 存储器件 §6.4 纳米器件 §6.5 功率器件 §6.6 微波器件 §6.7 光电子器件 §6.8 量子器件 Principle of Semiconductor Devices

中国科学技术大学物理系微电子专业 §6.1现代MOS器件 ULSI发展的两个主要方向:深亚微米与亚 0.1微米集成和系统的芯片集成 因此需要对深亚微米和亚0.1微米工艺、器 件和电路技术,器件的结构和相应的物理 机理的研究。微小MOSFET中的一些物理效 应,如器件尺寸变小,通常的一维器件模 型需要修正,出现二维、三维效应,同时 还会出现各种强电场效应。 Principle of Semiconductor Devices 2022/12/25 2

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 2 §6.1 现代MOS器件 • ULSI发展的两个主要方向:深亚微米与亚 0.1微米集成和系统的芯片集成。 • 因此需要对深亚微米和亚0.1微米工艺、器 件和电路技术,器件的结构和相应的物理 机理的研究。微小MOSFET中的一些物理效 应,如器件尺寸变小,通常的一维器件模 型需要修正,出现二维、三维效应,同时 还会出现各种强电场效应。 Principle of Semiconductor Devices

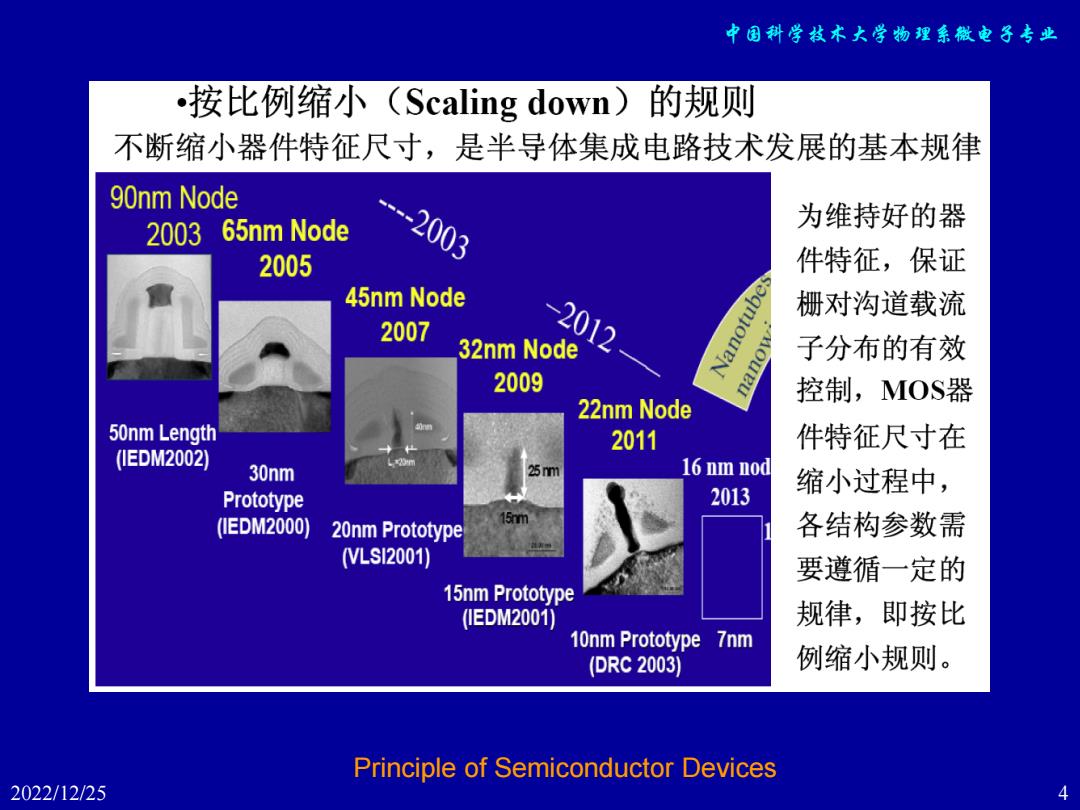

中国科学技术大学物理系微电子专业 一、MOSFET的按比例缩小、 近20年来,恒压按比例缩小规则的使用比较成功 但随着工艺的发展,器件性能和集成密度进一步 提高,日前逐渐逼近其基本的物理极限 。 如果要进一步提高集成电路的性能,则需要考虑 更多的因素,而不仅仅是简单的按比例缩小器件 尺寸。需要同时在降低电源电压、提高器件性能 和提高器件可靠性等三个方面之间进行折衷选择。 金属栅和高K栅介质的应用 Principle of Semiconductor Devices 2022/12/25 3

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 3 一、MOSFET的按比例缩小 • 近20年来,恒压按比例缩小规则的使用比较成功, 但随着工艺的发展,器件性能和集成密度进一步 提高,目前逐渐逼近其基本的物理极限。 • 如果要进一步提高集成电路的性能,则需要考虑 更多的因素,而不仅仅是简单的按比例缩小器件 尺寸。需要同时在降低电源电压、提高器件性能 和提高器件可靠性等三个方面之间进行折衷选择。 • 金属栅和高K栅介质的应用 Principle of Semiconductor Devices

中国科学技术大学物理系微电子专业 ·按比例缩小(Scaling down)的规则 不断缩小器件特征尺寸,是半导体集成电路技术发展的基本规律 90nm Node 2003 65nm Node -2003 为维持好的器 2005 件特征,保证 45nm Node -2012 栅对沟道载流 2007 32nm Node nano 子分布的有效 2009 控制,MOS器 22nm Node 50nm Length 2011 件特征尺寸在 (IEDM2002) 30nm 25m 16 nm nod 缩小过程中, Prototype 2013 (IEDM2000) 20nm Prototype 15m 各结构参数需 (VLSI2001) 要遵循一定的 15nm Prototype (IEDM2001) 规律,即按比 10nm Prototype 7nm (DRC2003) 例缩小规则。 Principle of Semiconductor Devices 2022/12/25 4

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 4 Principle of Semiconductor Devices

中国科学技术大学物理系微电子专业 实验结果表明,在进行折衷的过程中,源、漏结 的参数,尤其是结深、RD和结的突变性是至关重 要的因素。尽管这种经验方法不是很理想,而且 难以符合基于基本物理规律的按比例缩小规则, 但是这种经验方法更准确、更实用一些。这是由 于当器件横向尺寸的变化使器件的纵、横向以及 其他各方向上的参数错综复杂地相互作用时,器 件的三维特性越加突出;同时由于基本物理极限 的限制,对亚0.1um器件的进一步缩小变得非常困 难,这主要包括超薄栅氧化层的制作;源、漏超 浅结的形成以及小尺寸器件必须在很低的电源电 压下工作所带来的问题等。截至目前为止,器件 和ULSI CMOS工艺发展的实际情况是器件的各个 部分都在缩小。 Principle of Semiconductor Devices 2022/12/25 5

中国科学技术大学物理系微电子专业 2022/12/25 Sunday 5 • 实验结果表明,在进行折衷的过程中,源、漏结 的参数,尤其是结深、RSD和结的突变性是至关重 要的因素。尽管这种经验方法不是很理想,而且 难以符合基于基本物理规律的按比例缩小规则, 但是这种经验方法更准确、更实用一些。这是由 于当器件横向尺寸的变化使器件的纵、横向以及 其他各方向上的参数错综复杂地相互作用时,器 件的三维特性越加突出;同时由于基本物理极限 的限制,对亚0.1μm器件的进一步缩小变得非常困 难,这主要包括超薄栅氧化层的制作;源、漏超 浅结的形成以及小尺寸器件必须在很低的电源电 压下工作所带来的问题等。截至目前为止,器件 和ULSI CMOS工艺发展的实际情况是器件的各个 部分都在缩小。 Principle of Semiconductor Devices