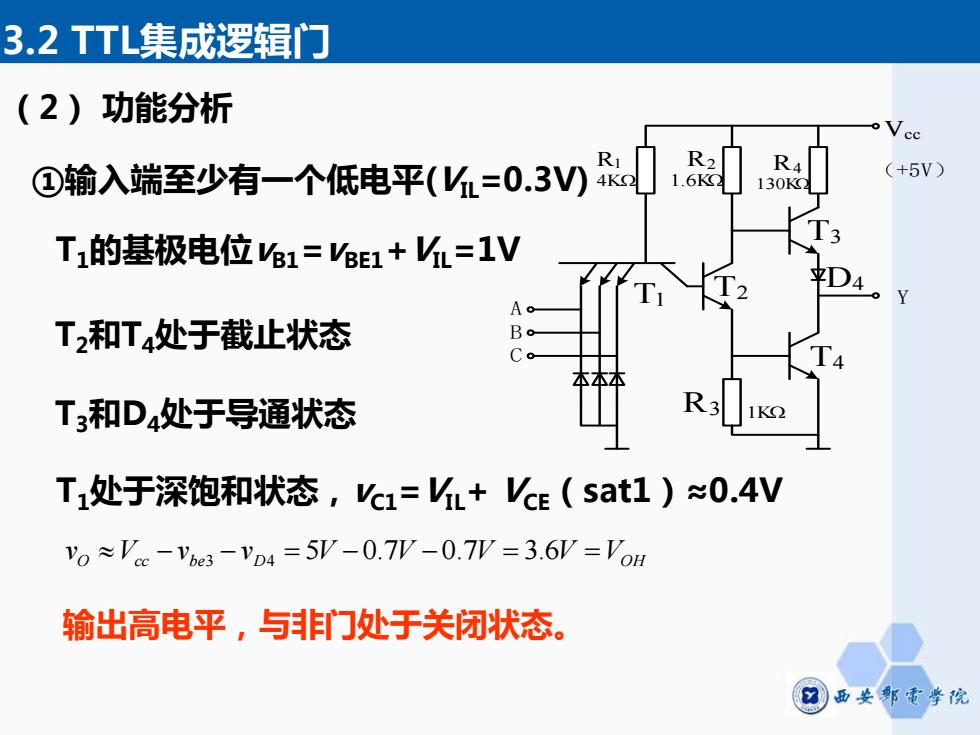

3.2TTL集成逻辑门 (2)功能分析 ①输入端至少有一个低电平(M=0.3 R2 R4 (+5V) 1.6K 130K2 T的基极电位e1=E1+=1V T2和T4处于截止状态 B。 T3和D4处于导通状态 T1处于深饱和状态,1=M+VcE(sat1)~0.4V o≈'.c-ye3-vp4=5Y-0.7V-0.7V=3.6V='om 输出高电平,与非门处于关闭状态

(2) 功能分析 ①输入端至少有一个低电平(VIL=0.3V) A B C (+5V) T1 T2 Y T3 T4 R1 R2 R3 D4 R4 4K Vcc 1.6K 130K 1K T1的基极电位vB1=vBE1+VIL=1V T2和T4处于截止状态 T1处于深饱和状态,vC1=VIL+ VCE(sat1)≈0.4V O cc be D V V V V VOH v V −v 3 −v 4 = 5 −0.7 −0.7 = 3.6 = 输出高电平,与非门处于关闭状态。 T3和D4处于导通状态 3.2 TTL集成逻辑门

3.2TTL集成逻辑门 ②输入端全部接高电平(M叫=3.6V) R R2 1.6 (+5V) 130K T管处于倒置工作状态。 T2和T4处于饱和状态。 B T3、D4处于截止状态。 输出电压%为: V%=VkEs4≈0.3V=V% 输出低电平,与非门处于开门状态

T1管处于倒置工作状态。 T2和T4处于饱和状态。 ② 输入端全部接高电平(VIH=3.6V) 输出电压vO为: VO =VCES4≈0.3V=VO 输出低电平,与非门处于开门状态 T3、D4处于截止状态。 3.2 TTL集成逻辑门 A B C (+5V) T1 T2 Y T3 T4 R1 R2 R3 D4 R4 4K Vcc 1.6K 130K 1K

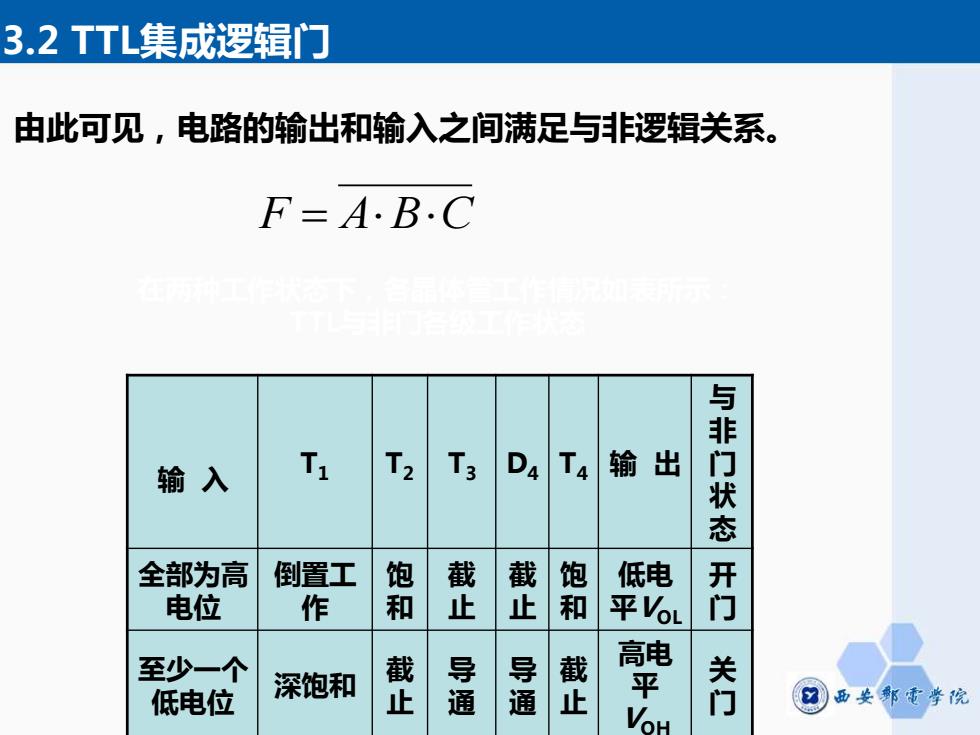

3.2TTL集成逻辑门 由此可见,电路的输出和输入之间满足与非逻辑关系。 F=A.B.C 输入 T2 T3 D4 T4 输出 非门状态 全部为高 倒置工 饱 截 截 饱 低电 开 电位 作 止 止 和 平Vou 至少一个 深饱和 导 截 高电 低电位 止 通 养 ⊙西重院

由此可见,电路的输出和输入之间满足与非逻辑关系。 F = ABC 在两种工作状态下,各晶体管工作情况如表所示: TTL与非门各级工作状态 输 入 T1 T2 T3 D4 T4 输 出 与 非 门 状 态 全部为高 电位 倒置工 作 饱 和 截 止 截 止 饱 和 低电 平VOL 开 门 至少一个 低电位 深饱和 截 止 导 通 导 通 截 止 高电 平 VOH 关 门 3.2 TTL集成逻辑门

3.2TTL集成逻辑门 (3)推拉输出电路和多发射极晶体管的作用 推拉输出电路的主要作用是提高带负载能力。当电路处于 关态时,输出级工作于射极输出状态,呈现低阻抗输出;当电 路处于开态时,T4处于饱和状态,输出电阻也很低。因此在稳 态时,电路均具有较低的输出阻抗,大大提高了带负载能力。 推拉输出电路和多发射极晶体管大大提高了电路的开关速 度。一般TTL与非门的平均延迟时间可以缩短到几十纳秒

推拉输出电路的主要作用是提高带负载能力。当电路处于 关态时,输出级工作于射极输出状态,呈现低阻抗输出;当电 路处于开态时,T4处于饱和状态,输出电阻也很低。因此在稳 态时,电路均具有较低的输出阻抗,大大提高了带负载能力。 推拉输出电路和多发射极晶体管大大提高了电路的开关速 度。一般TTL与非门的平均延迟时间可以缩短到几十纳秒。 3.2 TTL集成逻辑门 (3)推拉输出电路和多发射极晶体管的作用

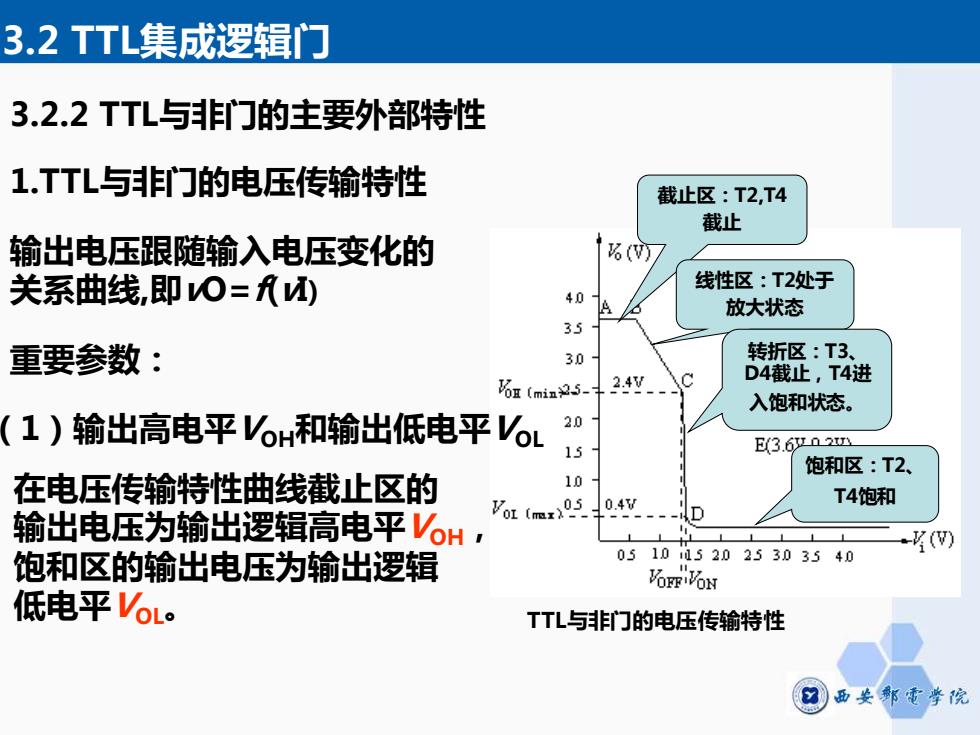

3.2TTL集成逻辑门 3.2.2TTL与非门的主要外部特性 1.TTL与非门的电压传输特性 截止区:T2,T4 截止 输出电压跟随输入电压变化的 6(7 关系曲线,即O=M) 线性区:T2处于 40色 放大状态 35 重要参数: 30 转折区:T3、 6r(min25-24y.-9 D4截止,T4进 入饱和状态。 (1)输出高电平V%H和输出低电平VoL E(3.6n2m 饱和区:T2、 在电压传输特性曲线截止区的 10 T4饱和 输出电压为输出逻辑高电平VoH, Vot (mx)05 viD 3(W) 饱和区的输出电压为输出逻辑 0510152025303540 名6N 低电平Vo. TTL与非门的电压传输特性

3.2.2 TTL与非门的主要外部特性 1.TTL与非门的电压传输特性 输出电压跟随输入电压变化的 关系曲线,即vO=f(vI) 截止区:T2,T4 截止 线性区:T2处于 放大状态 转折区:T3、 D4截止,T4进 入饱和状态。 饱和区:T2、 T4饱和 重要参数: (1)输出高电平VOH和输出低电平VOL TTL与非门的电压传输特性 在电压传输特性曲线截止区的 输出电压为输出逻辑高电平VOH, 饱和区的输出电压为输出逻辑 低电平VOL。 3.2 TTL集成逻辑门