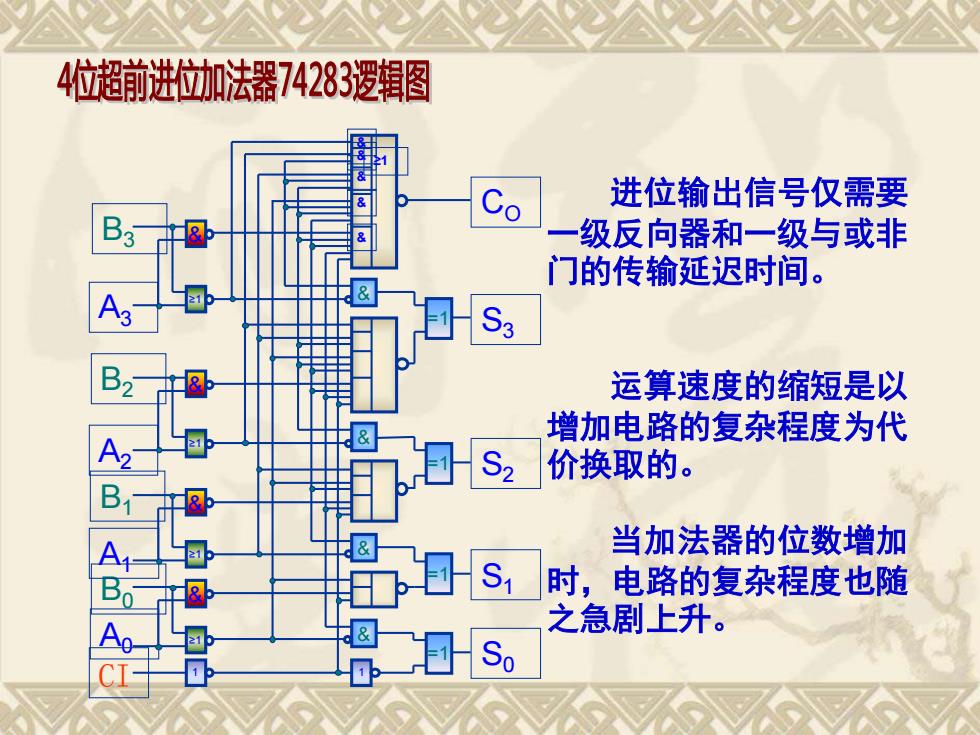

4位超前进位加法器74283逻辑图 进位输出信号仅需要 级反向器和一级与或非 门的传输延迟时间。 运算速度的缩短是以 增加电路的复杂程度为代 S2价换取的。 o& 当加法器的位数增加 S1 时,电路的复杂程度也随 之急剧上升。 So

进位输出信号仅需要 一级反向器和一级与或非 门的传输延迟时间。 运算速度的缩短是以 增加电路的复杂程度为代 价换取的。 当加法器的位数增加 时,电路的复杂程度也随 之急剧上升。 C O S 3 S 2 S 1 S 0 &&&&& ≥1 &&&& &&&& ≥1 ≥1 ≥1 ≥11 1 =1 =1 =1 =1 B 3 B 2 B 1 B 0 A 0 A 1 A 2 A 3 CI

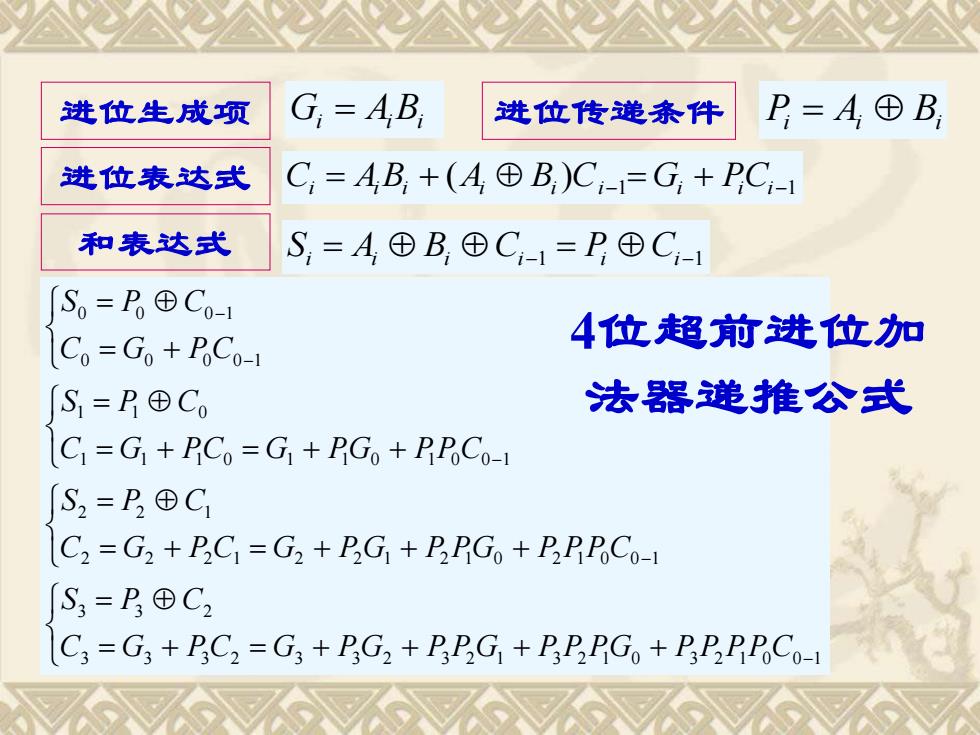

进位生成须 G=AB 进位传递条件 P=A⊕B 进位表达式 C=4B+(4B)C-=G+PC- 和表达式 S,=A田B,®C-1=卫⊕C-1 S。=P⊕C0- Co=Go+PoCo-1 4位超前进位加 S,=P⊕Co 法器递推公式 C=G+PCo=G+PGo+PPoCo-1 S2=P®C1 C2=G2+PC=G2+PG+PPGo+PPPoCo- S3=P3⊕C2 C3=Gs+PC2=G3+PG2+PPG+PPPGo+PPPPoCo-1

进位生成项 Gi = Ai Bi 进位传递条件 Pi = Ai Bi 1 1 ( ) 进位表达式 Ci = Ai Bi + Ai Bi Ci− = Gi + Pi Ci− = + = + + + + = = + = + + + = = + = + + = = + = − − − − − 3 3 3 2 3 3 2 3 2 1 3 2 1 0 3 2 1 0 0 1 3 3 2 2 2 2 1 2 2 1 2 1 0 2 1 0 0 1 2 2 1 1 1 1 0 1 1 0 1 0 0 1 1 1 0 0 0 0 0 1 0 0 0 1 C G PC G PG P P G P P PG P P PPC S P C C G PC G P G P PG P PPC S P C C G PC G PG PPC S P C C G PC S P C 和表达式 Si = Ai Bi Ci−1 = Pi Ci−1 4位超前进位加 法器递推公式

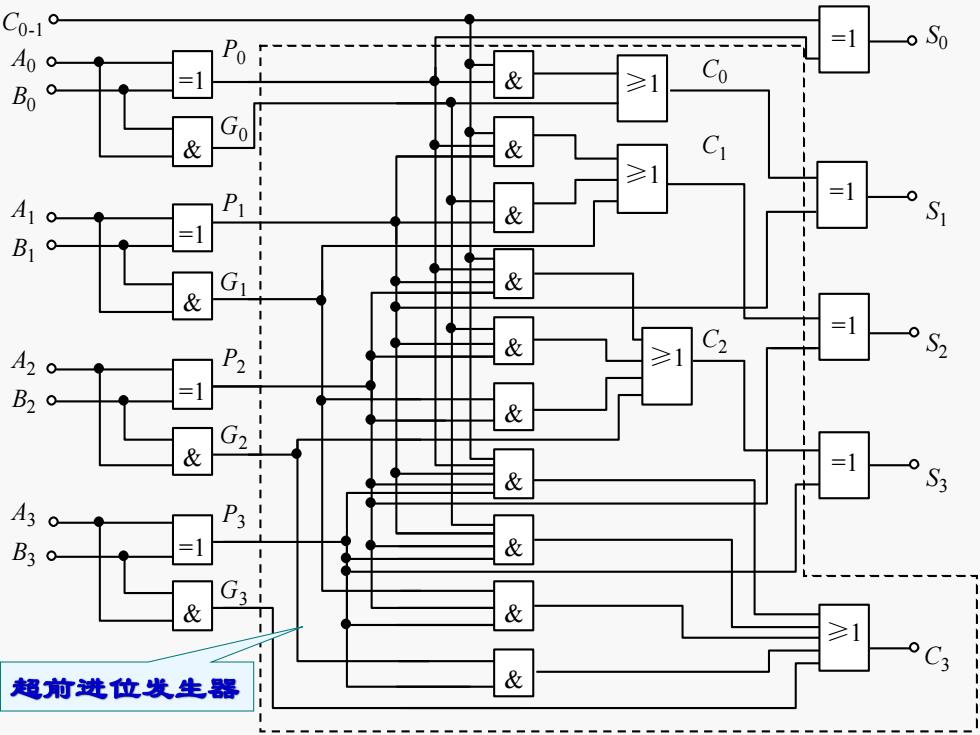

Co-1 So Ao 0 B 0 & A P Q =1 B1 S, A2 Q B2 Q & & & S3 A3 Q B3 & & 超前进位发生器 &

S0 S1 S2 S3 C3 C0-1 A0 B0 A1 B1 A2 B2 A3 B3 = 1 & & ≥1 P0 G0 P1 G1 P2 G2 P3 G3 ≥1 ≥1 = 1 & & & & = 1 & & & C0 C1 C2 ≥1 & & = 1 = 1 = 1 = 1 & = 1 & 超前进位发生器 &

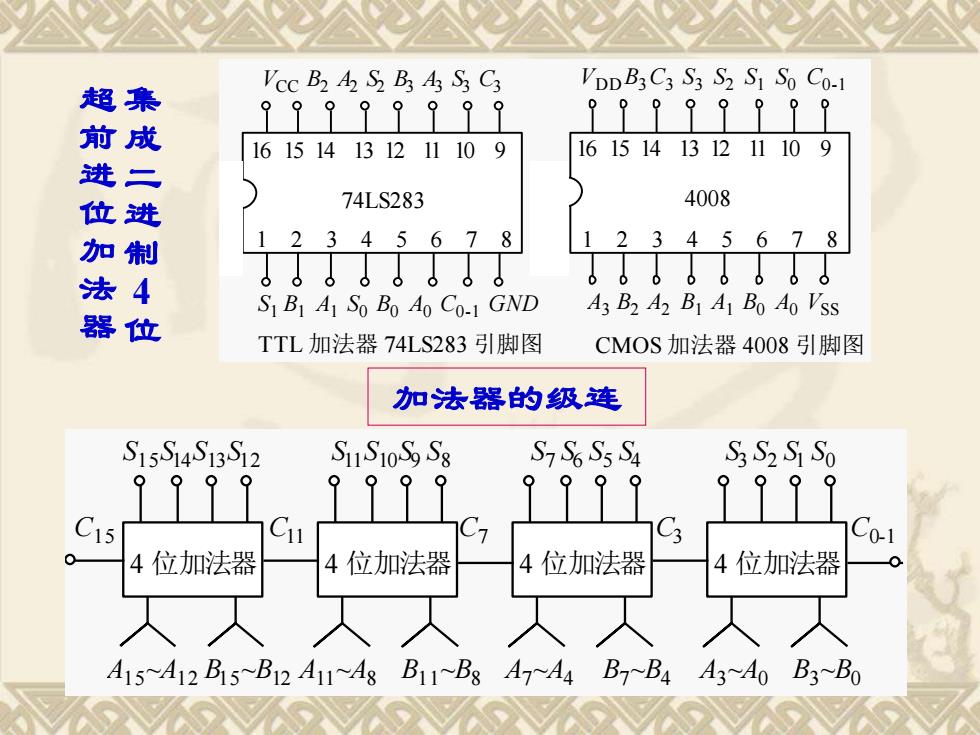

VDDB3 C3 S3 S2 S1 So Co-1 集 Vcc B2 A S B3 As S C3 99999999 9999999 超前进位加法器 成 161514131211109 161514131211109 74LS283 4008 制 12345678 1 2345678 。 。 位 S1 B1 A1 So Bo Ao Co-1 GND A3 B2 A2 B1 A1 Bo Ao Vss TTL加法器74LS283引脚图 CMOS加法器4008引脚图 加法器的级连 S15S14S13S12 STSIOS Ss S7$6S5S4 S3 S2S1 So 9 99 99 9 99 C15 Cu C1 C3 Co-i 4 位加法器 4位加法器 4位加法器 4 位加法器 A15~A12 B15-B12 A11~A8 B11~B8 ATA4 BTBA A3~40 B3~Bo

16 15 14 13 12 11 10 9 74LS283 1 2 3 4 5 6 7 8 VCC B2 A2 S2 B3 A3 S3 C3 TTL 加法器 74LS283 引脚图 16 15 14 13 12 11 10 9 4008 1 2 3 4 5 6 7 8 VD D B3C3 S3 S2 S1 S0 C0-1 CMOS 加法器 4008 引脚图 S1 B1 A1 S0 B 0 A 0 C0-1 GND A3 B 2 A 2 B1 A1 B 0 A 0 VSS A1 5 ~A12 B1 5 ~B12 A11 ~A8 B1 1 ~B8 A 7 ~A 4 B 7 ~B 4 A3~A0 B3~B 0 S1 5 S14 S13 S1 2 S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1 S0 4 位加法器 4 位加法器 4 位加法器 4 位加法器 C1 5 C11 C7 C3 C0-1 加法器的级连 集成二进制4位 超前进位加法器

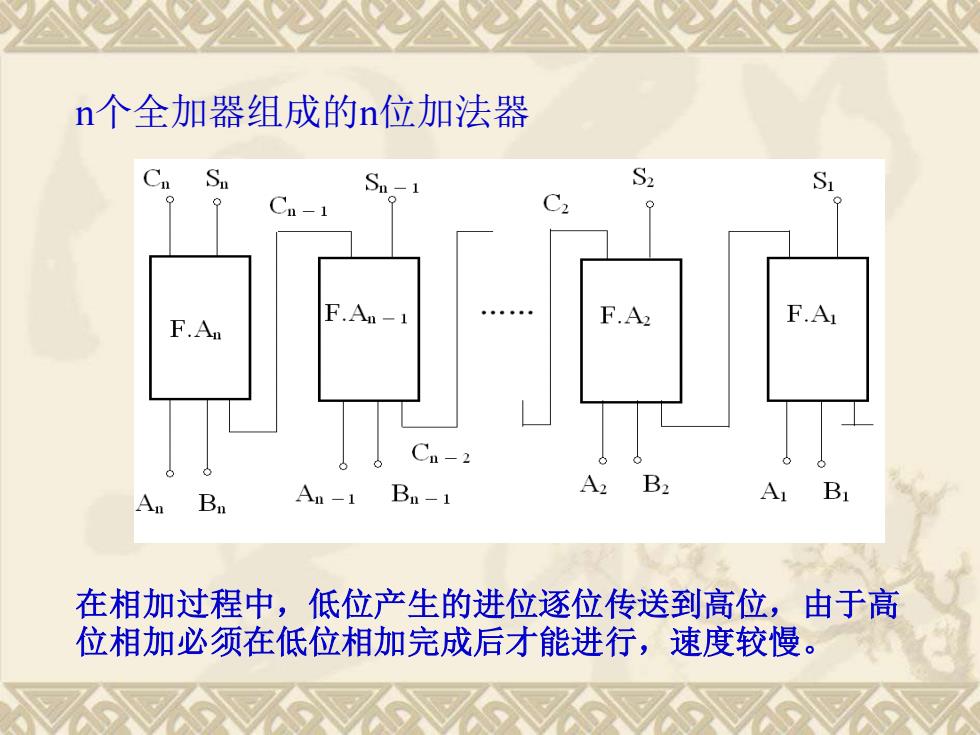

n个全加器组成的n位加法器 C C-1 Sm。 S2 F.An F.A-1 F.A2 F.A An -1 Bu A B2 A B 在相加过程中,低位产生的进位逐位传送到高位,由于高 位相加必须在低位相加完成后才能进行,速度较慢

n个全加器组成的n位加法器 在相加过程中,低位产生的进位逐位传送到高位,由于高 位相加必须在低位相加完成后才能进行,速度较慢