第4章组合逻辑电路

第4章 组合逻辑电路

第五节 译码器和数据分配器 把代码状态的特定含义翻译出来的过程称为译码, 实现译码操作的电路称为译码器。 译码器一将输入代码转换成特定的输出信号 1、二进制译码器 设二进制译码器的输入端为n个,则输出端为2n 个,且对应于输入代码的每一种状态,2个输出中 只有一个为1(或为0),其余全为0(或为1)。 二进制译码器可以译出输入变量的全部状态,故 又称为变量译码器

把代码状态的特定含义翻译出来的过程称为译码, 实现译码操作的电路称为译码器。 设二进制译码器的输入端为n个,则输出端为2 n 个,且对应于输入代码的每一种状态,2 n个输出中 只有一个为1(或为0),其余全为0(或为1)。 二进制译码器可以译出输入变量的全部状态,故 又称为变量译码器。 1、二进制译码器 第五节 译码器和数据分配器 译码器——将输入代码转换成特定的输出信号

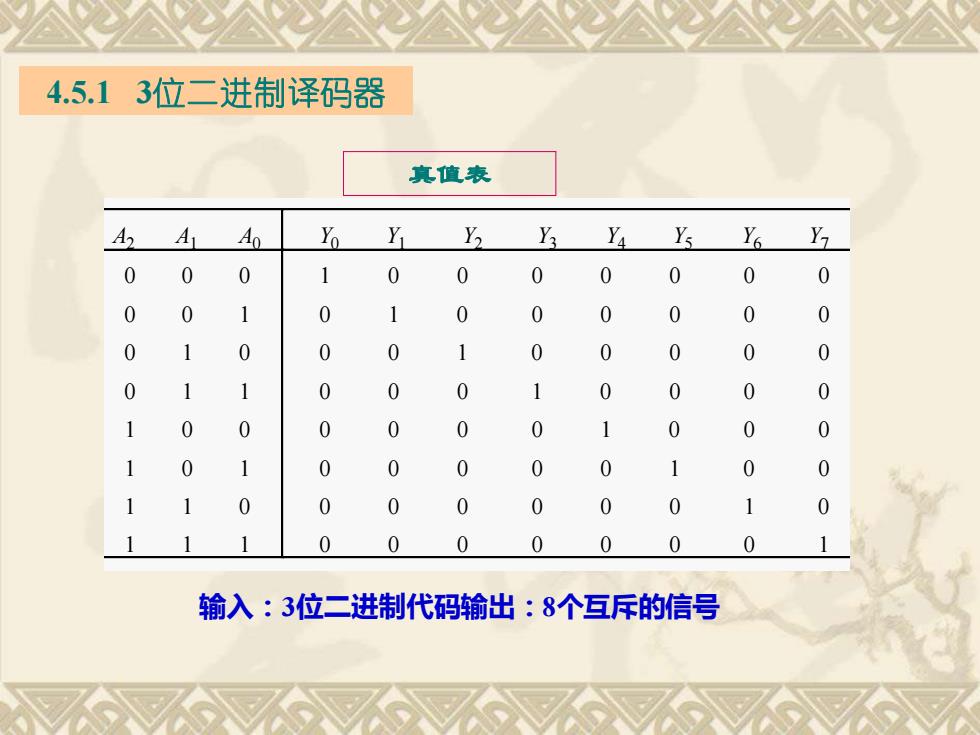

4.5.13位二进制译码器 真值表 A2 A Yo Y Y 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 2 输入:3位二进制代码输出:8个互斥的信号

4.5.1 3位二进制译码器 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 真值表 输入:3位二进制代码输出:8个互斥的信号

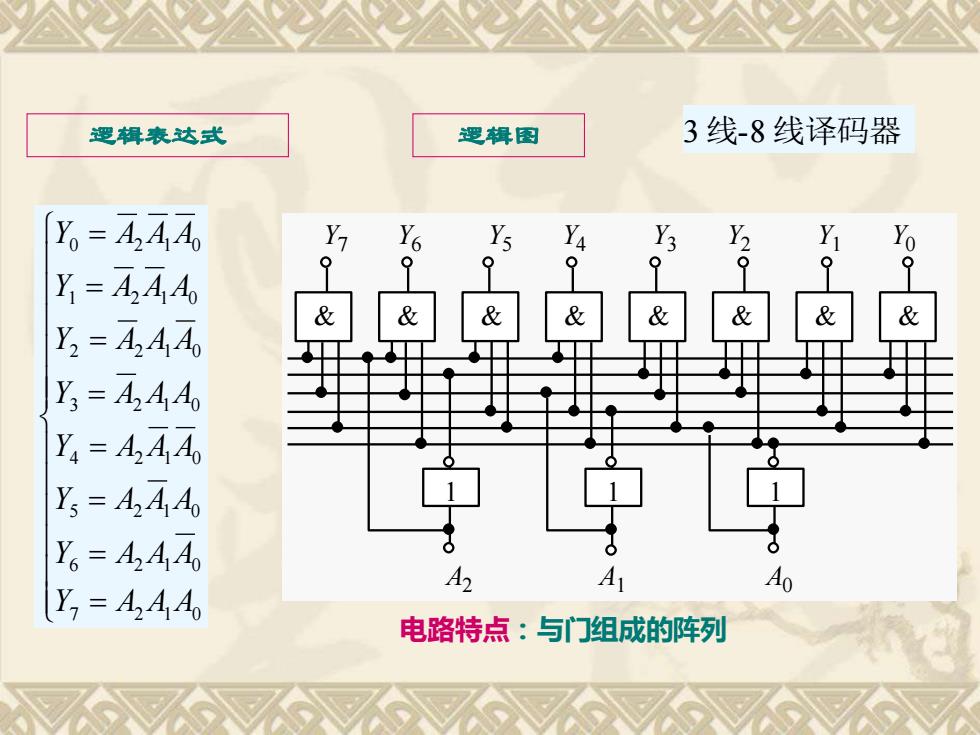

逻楫表达式 逻辑图 3线-8线译码器 Yo=42 44o Y7 Y6 Y5 Y4 Y3 Y=444 Y3=444o Y3=4AAo Y=444 Ys=44 4o Yo=A2A Ao A Ao Y=44 4o 电路特点:与门组成的阵列

= = = = = = = = 7 2 1 0 6 2 1 0 5 2 1 0 4 2 1 0 3 2 1 0 2 2 1 0 1 2 1 0 0 2 1 0 Y A A A Y A A A Y A A A Y A A A Y A A A Y A A A Y A A A Y A A A & & & & & & & & 1 1 1 A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 逻辑表达式 逻辑图 电路特点:与门组成的阵列 3 线-8 线译码器

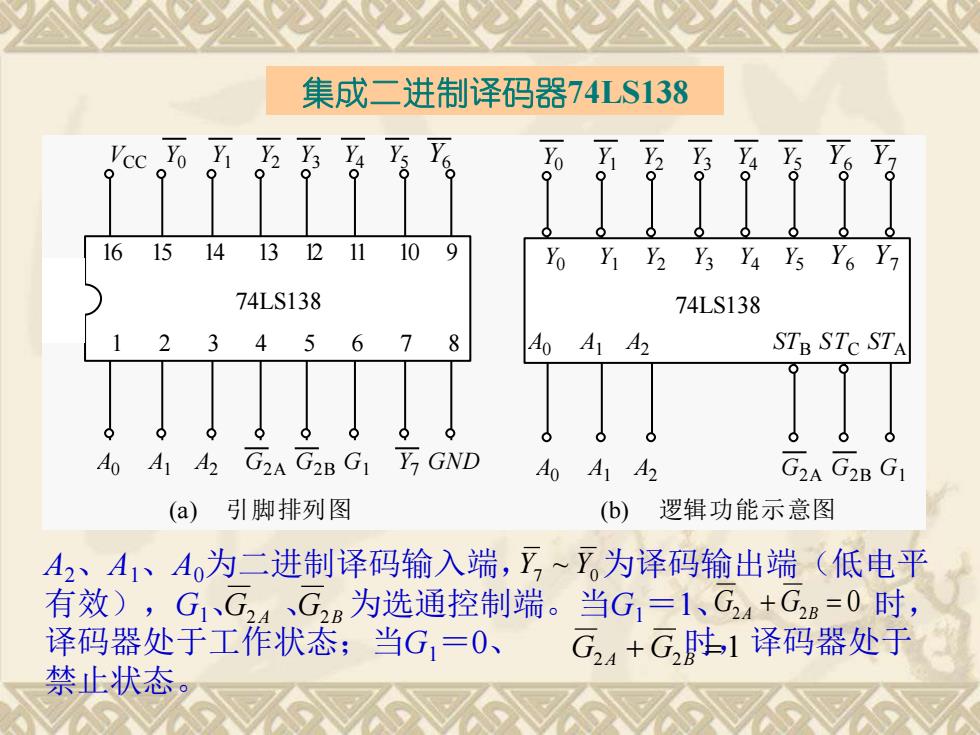

集成二进制译码器74LS138 cc方五gz Yo 。 】 16151413121110 9 Yo Y1 Y2 Y3 Y4 Y5 Y6 Y7 74LS138 74LS138 2 3 5 67 8 A1A2 STB STC STA ●】 40 A1 42 G2A G2B G1 Y7 GND A0 A1 A2 G2A G2B GI (a)引脚排列图 (b)逻辑功能示意图 A2、A1、A0为二进制译码输入端,~,为译码输出端(低电平 有效),G1、G24、G2B为选通控制端。当G1=1、G4+GB=0时, 译码器处于工作状态;当G1=0、 G24+G,时1译码器处于 禁止状态

集成二进制译码器74LS138 16 15 14 13 12 11 10 9 74LS138 1 2 3 4 5 6 7 8 VCC Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 G2 A G2 B G1 Y7 GND 74LS138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 G2 A G2 B G1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 STB S TC STA (a) 引脚排列图 (b) 逻辑功能示意图 A2、A1、A0为二进制译码输入端, 为译码输出端(低电平 有效),G1、 、 为选通控制端。当G1 =1、 时, 译码器处于工作状态;当G1 =0、 时,译码器处于 禁止状态。 Y7 ~ Y0 G2A G2B 0 G2A + G2B = G2A + G2B =1