G24+G2B 真值表 输 输 出 使 能 选择 6 A2 A Ao Y 5 4 × × × × 1 1 1 0 + × 1 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 0 0 1 1 0 1 0 0 1 0 1 0 1 0 0 0 0 输入:自然二进制码 输出:低电平有效

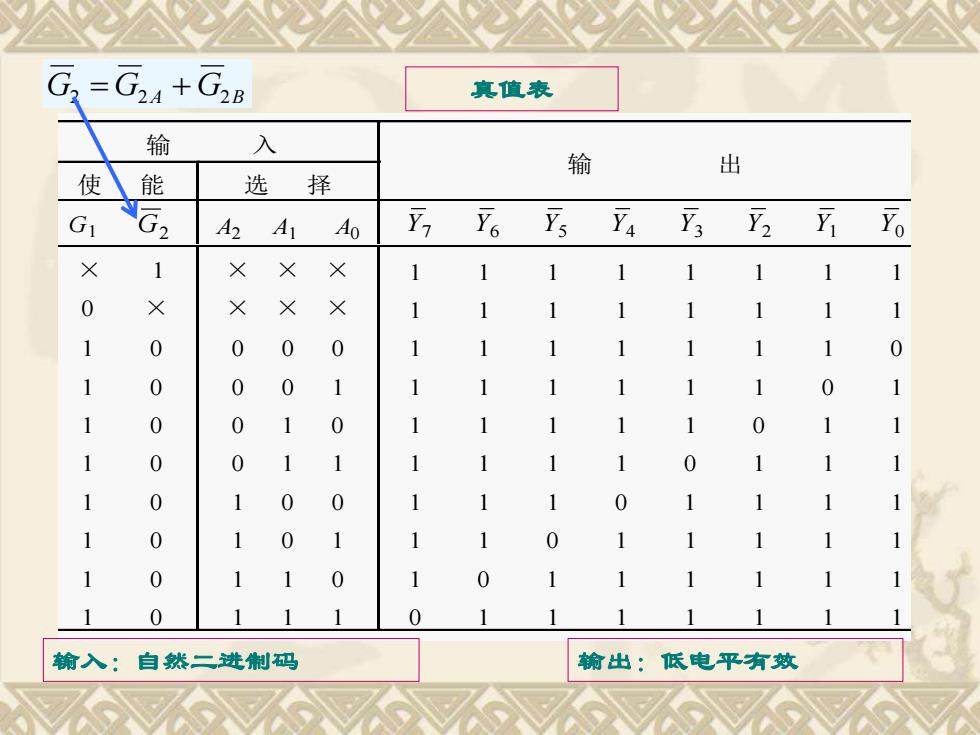

真值表 输 入 使 能 选 择 输 出 G1 G2 A2 A1 A0 7 6 5 4 3 2 1 0 Y Y Y Y Y Y Y Y × 1 0 × 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 × × × × × × 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 输入:自然二进制码 输出:低电平有效 G2 = G2A + G2B

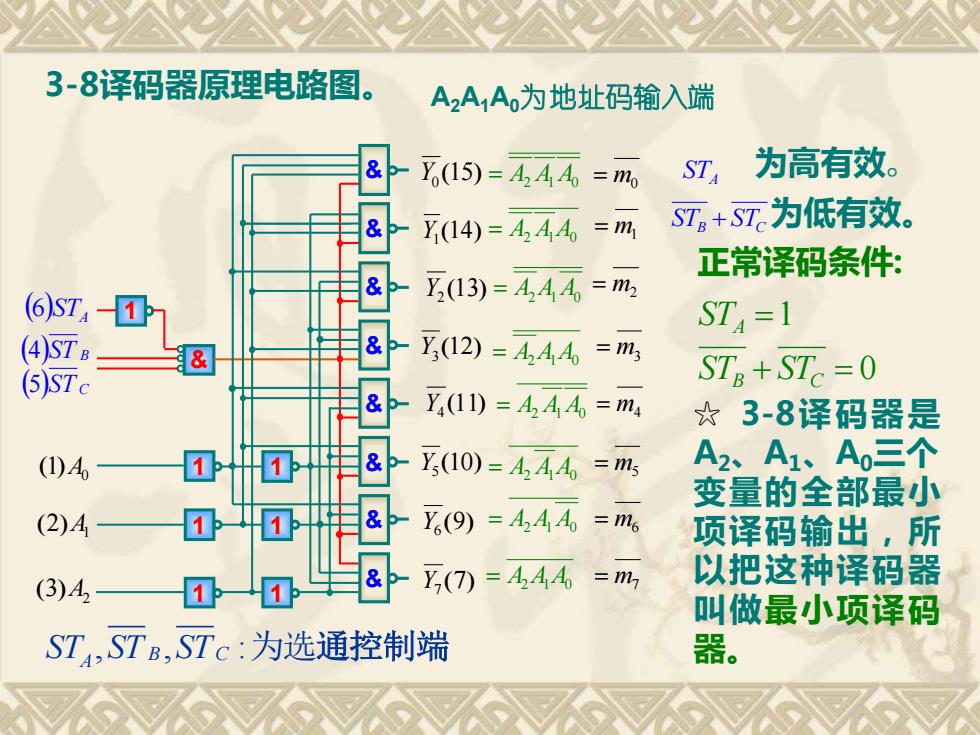

3-8译码器原理电路图。 A2A1A,为地址码输入端 & X15)=A4A=m ST 为高有效。 & Z(14)=A244=m ST+ST为低有效。 正常译码条件: (6sT4① & Y2(13)=A,A4A=m ST4=1 (4)S7B & & Y,12)=A,44,=m (5)STc STR+STc=0 & Y4(11)=AA4=m4 ☆3-8译码器是 (1)4 6 Y,(10)=4,A4=ms A2、 A1、A三个 变量的全部最小 (2)4 & Y6(9)=A,4A6 =m6 项译码输出,所 (3)42 & Z,(7=4440 =m2 以把这种译码器 叫做最小项译码 ST,STa,STc:为选通控制端 器

( ) 6 STA (4)ST B (5)ST C ( )1 A0 ( ) 2 A1 ( ) 3 A2 (15) Y0 (14) Y1 (13) Y2 (11) Y4 (10) Y5 (9) Y6 (7) Y7 (12) Y3 3-8译码器原理电路图。 , , : B C A ST ST ST 为选通控制端 STA STB + STC =1 A STSTB + STC = 0 为高有效。 为低有效。 正常译码条件: = A2 A1 A0 = A2 A1 A0 = A2 A1 A0 = A2 A1 A0 = A2 A1 A0 = A2 A1 A0 = A2 A1 A0 = A2 A1 A0 = m0 = m1 = m2 = m3 = m4 = m5 = m6 = m7 ☆ 3-8译码器是 A2、A1、A0三个 变量的全部最小 项译码输出,所 以把这种译码器 叫做最小项译码 器。 A2A1A0为地址码输入端 & & & & & & & & 1 1 1 1 1 1 1 &

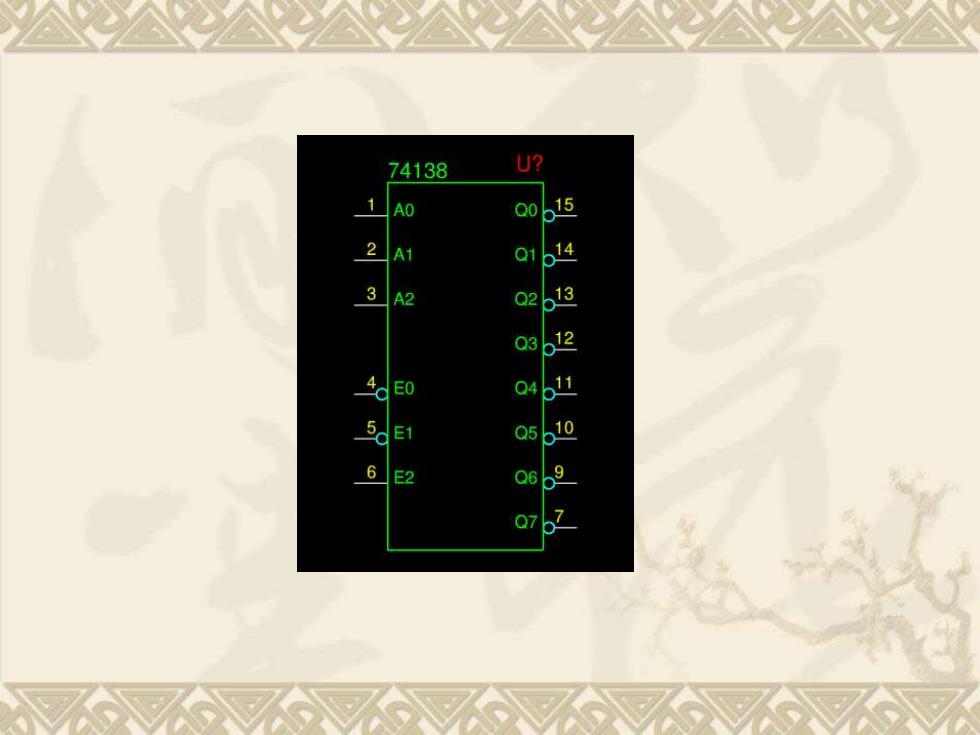

74138 U? AO 2 A1 868 14 3 A2 4 5。 E1 6 E2

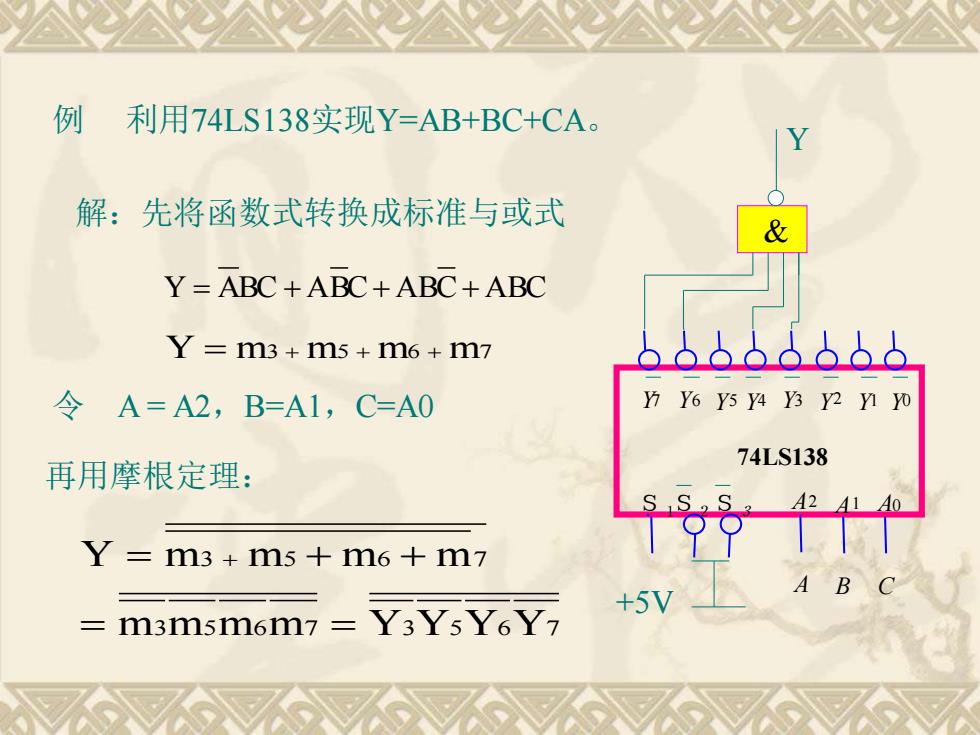

例 利用74LS138实现Y=AB+BC+CA。 解:先将函数式转换成标准与或式 Y=ABC+ABC+ABC+ABC Y=m3+m5+m6+m7 令A=A2,B=A1,C=A0 7Y6Y5432o 74LS138 再用摩根定理: A2 A1 A0 Y=m3+m5+m6+m7 +5V =m3m5m6m7

例 利用74LS138实现Y=AB+BC+CA。 解:先将函数式转换成标准与或式 Y = ABC + ABC+ ABC+ ABC Y = m3 + m5 + m6 + m7 令 A = A2,B=A1,C=A0 再用摩根定理: 3 5 6 7 3 5 6 7 3 5 6 7 m m m m Y Y Y Y Y m m m m = = = + + + S 1 1 A 0 74LS138 S2S A2 3 A Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 & Y A B C +5V

4.5.2二-十进制译码器 把二-十进制代码翻译成10个十进制数字 信号的电路,称为二-十进制译码器。 二-十进制译码器的输入是十进制数的4 位二进制编码(BCD码),分别用A、A2、A1、 A,表示;输出的是与10个十进制数字相对应 的10个信号,用。~%表示。由于二-十进 制译码器有4根输入线,10根输出线,所以 又称为4线10线译码器

二-十进制译码器的输入是十进制数的4 位二进制编码(BCD码),分别用A3、A2、A1、 A0表示;输出的是与10个十进制数字相对应 的10个信号,用Y9 ~Y0表示。由于二-十进 制译码器有4根输入线,10根输出线,所以 又称为4线-10线译码器。 4.5.2 二-十进制译码器 把二-十进制代码翻译成10个十进制数字 信号的电路,称为二-十进制译码器