DBUS IBUS 数据 指令 Cache Cache ALU 地细 数据 地 OP 地址字段 C2 5 7 101 MOV R0,R1 6 100 102 LAD R1,6 RO 66 103 ADD R1,R2 R1 用寄存器 10 77 104 STO R2,R3) R2 105 JMP 101 ●●● R3 30 40 106 AND R1,R3 31 107 数据 地址总线 指令 地址总线 数据缓冲寄存器DR AR地址寄存器 +1 PC程序计数器 状态字PSW 通C1 C2, 时序发生器 指令译码 操作控制器 口 OC OP 地址字段 指令集确定后,检查指令系统,根据指令功能,设计 R指令寄存器 ALU,确定数据通路、控制部件!!I

ALU C1 R0 R1 R2 R3 C2 通 用 寄 存 器 数据缓冲寄存器DR 状态字PSW 通 往 I/O 接 口 地址 数据 5 70 6 100 7 66 10 77 . . 30 40 31 数据 Cache AR地址寄存器 地址 OP 101 MOV 102 LAD 103 ADD 104 STO 105 JMP 106 AND 107 Cache 指令 地址字段 R0,R1 R1,6 R1,R2 R2,(R3) 101 R1,R3 PC程序计数器 +1 地址总线 地址总线 DBUS 数据 指令 时序发生器 操作控制器 指令译码 OP 地址字段 C1 C2 Cn Ci 指令集确定后,检查指令系统,根据指令功能,设计 IR指令寄存器 ALU,确定数据通路、控制部件!!! IBUS OC

三、CPU中的主要寄存器 CPU中至少有如下六类寄存器 1PC程序计数器 2指令寄存器 3地址寄存器 4数据缓冲器 5累加寄存器及通用寄存器 6状态条件寄存器PSW

三、CPU中的主要寄存器 CPU中至少有如下六类寄存器 1 PC程序计数器 2 指令寄存器 3 地址寄存器 4数据缓冲器 5累加寄存器及通用寄存器 6 状态条件寄存器PSW

程序计数器(PC) 指示(指出)下一条指令的内存地址

程序计数器(PC) 指示(指出)下一条指令的内存地址

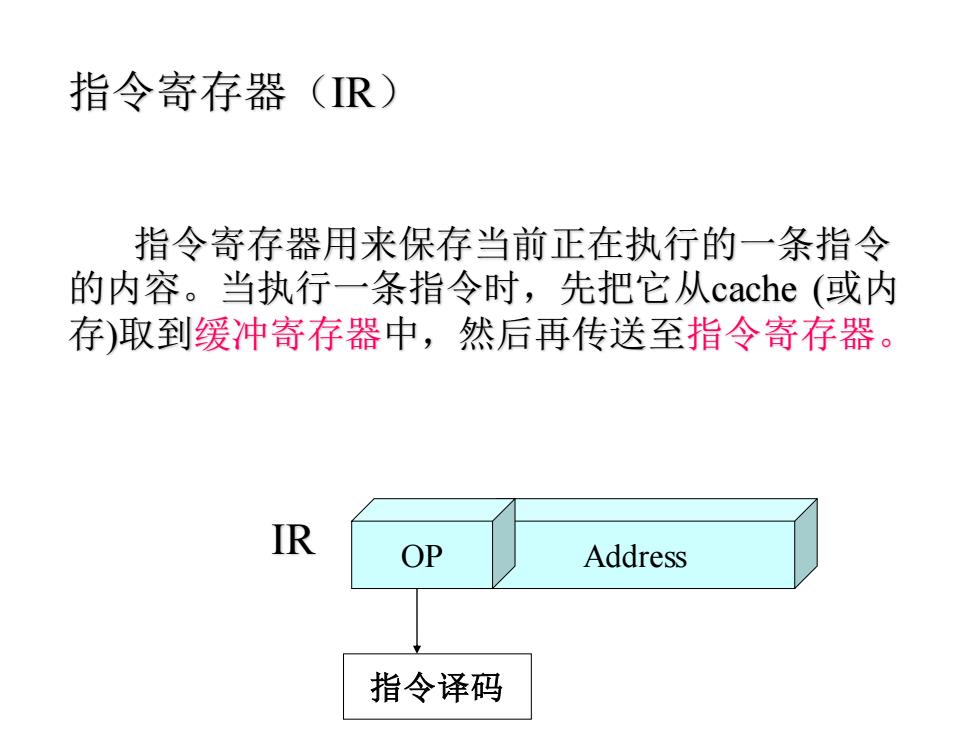

指令寄存器(R) 指令寄存器用来保存当前正在执行的一条指令 的内容。当执行一条指令时,先把它从cache(或内 存)取到缓冲寄存器中,然后再传送至指令寄存器。 IR OP Address 指令译码

指令寄存器(IR) 指令寄存器用来保存当前正在执行的一条指令 的内容。当执行一条指令时,先把它从cache (或内 存)取到缓冲寄存器中,然后再传送至指令寄存器。 OP Address IR 指令译码

数据地址寄存器(AR,MAR) 地址寄存器用来保存当前CPU所访问的Cache或 内存单元的地址,直到内存的读/写操作完成为止

数据地址寄存器(AR,MAR) 地址寄存器用来保存当前CPU所访问的 Cache或 内存单元的地址,直到内存的读/写操作完成为止