2 University of Electronic Science Technology of China(UESTC) Chapter 2 Hardware System Real-Time System Lab LIAO Yong

2 Real-Time System Lab LIAO Yong University of Electronic Science & Technology of China (UESTC) Chapter 2 Hardware System

3 1 Overview University of Electronic Science Technology of China(UESTC) Basic component of embedded Hardware(H/W)system Design of H/W system Real-Time System Lab LIAO Yong

3 Real-Time System Lab LIAO Yong University of Electronic Science & Technology of China (UESTC) 1 Overview Basic component of embedded Hardware (H/W) system Design of H/W system

4 2 Basic component University of Electronic Science Technology of China(UESTC) GPRS/CDMA How is this evaluation board changed into a MP4? How to debug the software of this embedded board? What's the difference between the embedded board and the PC board Real-Time System Lab LIAO Yong

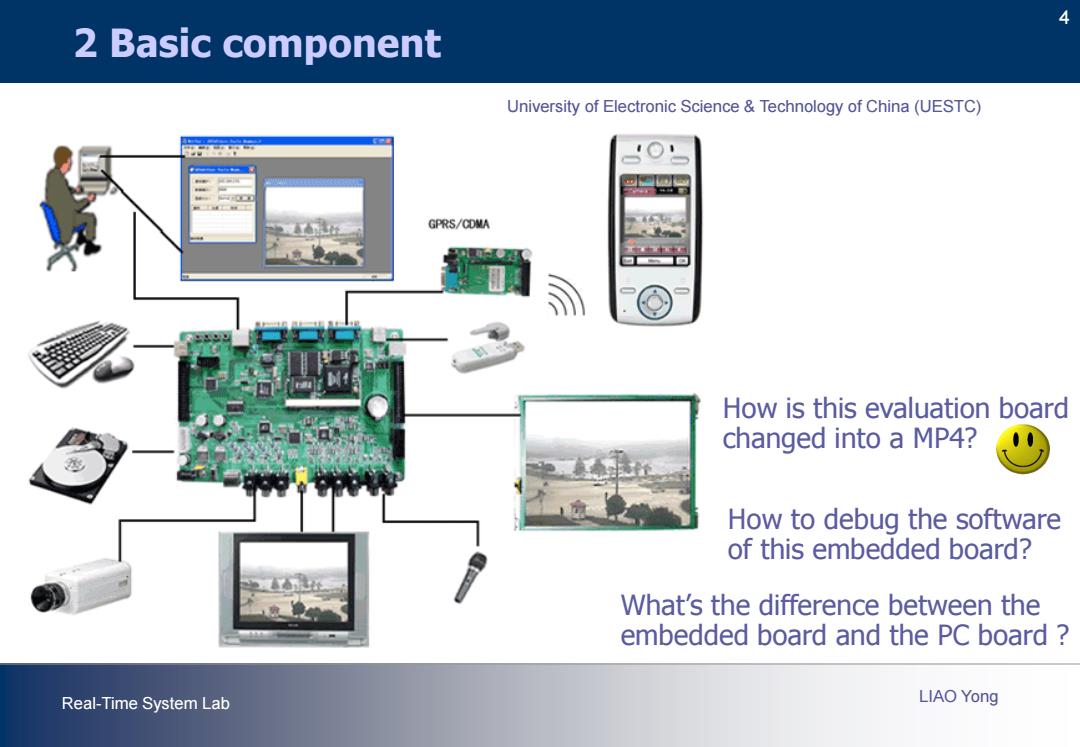

4 Real-Time System Lab LIAO Yong University of Electronic Science & Technology of China (UESTC) 2 Basic component What’s the difference between the embedded board and the PC board ? How to debug the software of this embedded board? How is this evaluation board changed into a MP4?

5 2 Basic component University of Electronic Science Technology of China(UESTC) Processor Input output actuators Output Memory input sensors CPU Bus mem embedded computer Real-Time System Lab LIAO Yong

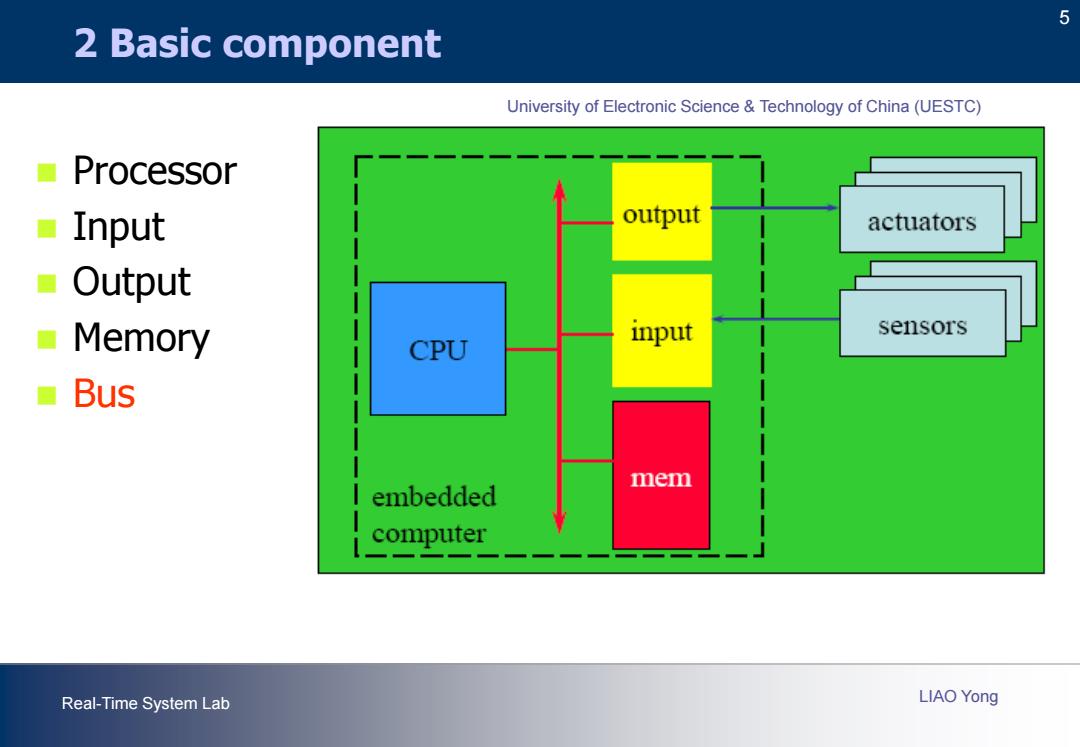

5 Real-Time System Lab LIAO Yong University of Electronic Science & Technology of China (UESTC) 2 Basic component Processor Input Output Memory Bus

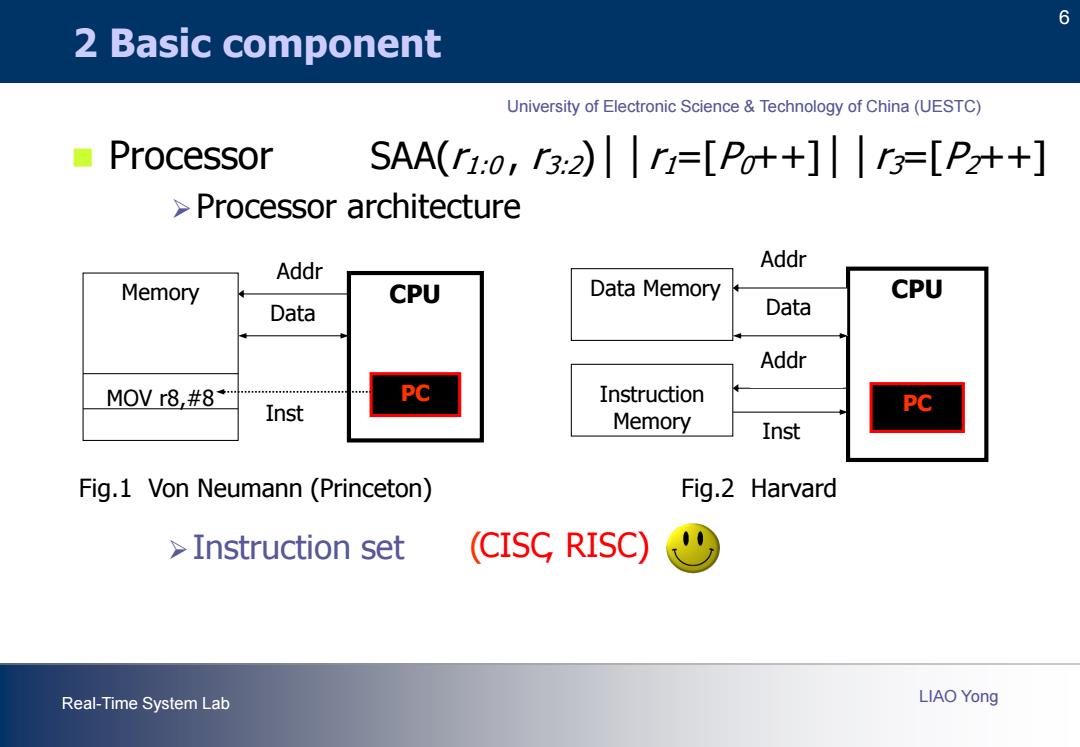

6 2 Basic component University of Electronic Science Technology of China(UESTC) ■Processor SAA(r1:o,r3:2)|r=[Pt+]|r3=[P++] >Processor architecture Addr Addr Memory CPU Data Memory CPU Data Data Addr MOV r8,#8 PC Instruction Inst PC Memory Inst Fig.1 Von Neumann(Princeton) Fig.2 Harvard >Instruction set (CISC RISC) Real-Time System Lab LIAO Yong

6 Real-Time System Lab LIAO Yong University of Electronic Science & Technology of China (UESTC) 2 Basic component Processor Processor architecture Addr Data Memory MOV r8,#8 CPU PC Inst Fig.1 Von Neumann (Princeton) Instruction set (CISC , RISC) Inst CPU PC Addr Data Memory Instruction Memory Addr Data Fig.2 Harvard SAA(r1:0 , r3:2)││r1=[P0++]││r3=[P2++]