TMS320VC5402芯片结构 (1)存储空间 >多总线结构。片内有3条16位数据总线(CB、DB、EB)、1条16位的程序总线 (PB)、以及4条对应的地址总线(PAB、CAB、DAB、EAB)。 >地址线20根,可寻址程序空间1M字,数据和VO空间各64K字。 >片内ROM容量为4K×16位(5402A是16K×16位) >片内双寻址RAM(DARAM)容量为16KX16位。 (2)在片内外围电路 >软件可编程等待状态发生器和可编程分区切换逻辑电路。 >带有内部振荡器或用外部时钟源的片内锁相环(PLL)时钟发生器。 >2个高速、全双工多通道缓冲串行口(McBSP)(5402A是3个) >增强型8位并行主机接口(HPI8) >2个16位定时器)(5402A是1个) >6通道DMA控制器 >具有符合EEE1149.1标准的在片仿真接口JTAG。 (3)电源、时钟与封装 >单周期定点指令的执行周期为10ns(100MIPS)(5402A是160MHz,6.25ns) >I/O电源电压3.3V,内核1.8V(5402A是1.6V) >可用IDLE1、IDLE2、IDLE3指令控制芯片功耗以工作在省电方式。 > 144号引脚的薄形四边形引脚扁平封装(LQFP)或144脚的球栅阵列封装(BA)

• TMS320VC5402芯片结构 • (1)存储空间 ➢ 多总线结构。片内有3条16位数据总线(CB、DB、EB)、1条16位的程序总线 (PB)、以及4条对应的地址总线(PAB、 CAB、DAB、EAB)。 ➢ 地址线20根,可寻址程序空间1M字,数据和I/O空间各64K字。 ➢ 片内ROM容量为4K×16位(5402A是16K×16位) ➢ 片内双寻址RAM(DARAM)容量为16K×16位。 • (2)在片内外围电路 ➢ 软件可编程等待状态发生器和可编程分区切换逻辑电路。 ➢ 带有内部振荡器或用外部时钟源的片内锁相环(PLL)时钟发生器。 ➢ 2个高速、全双工多通道缓冲串行口(McBSP)(5402A是3个) ➢ 增强型8位并行主机接口(HPI8) ➢ 2个16位定时器)(5402A是1个) ➢ 6通道DMA控制器 ➢ 具有符合IEEE1149.1标准的在片仿真接口JTAG。 • (3)电源、时钟与封装 ➢ 单周期定点指令的执行周期为10ns(100MIPS)(5402A是160 MHz, 6.25ns) ➢ I/O电源电压3.3V,内核1.8V(5402A是 1.6V) ➢ 可用IDLE1、IDLE2、IDLE3指令控制芯片功耗以工作在省电方式。 ➢ 144引脚的薄形四边形引脚扁平封装(LQFP)或144脚的球栅阵列封装(BGA)。 11

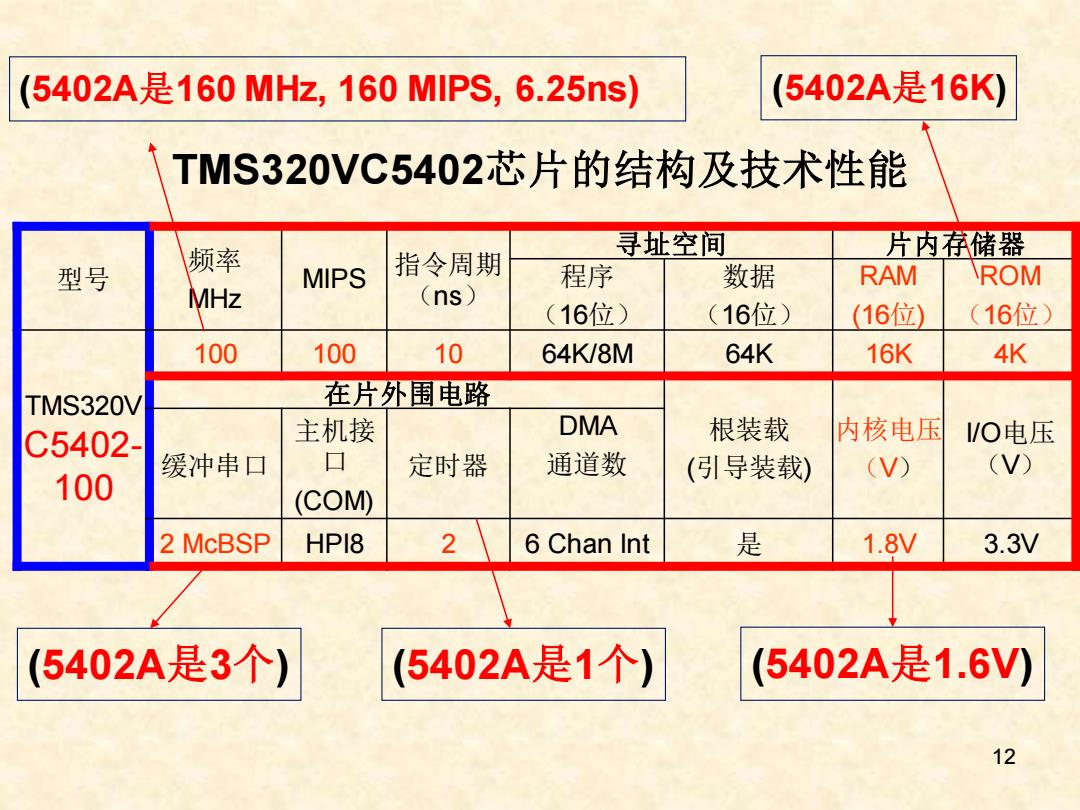

(5402A是160MHz,160MIPS,6.25ns) (5402A是16K) TMS320VC5402芯片的结构及技术性能 频率 寻址空间 片内存储器 型号 MIPS 指令周期 程序 数据 RAM ROM MHz (ns) (16位) (16位) (16位) (16位) 100 100 10 64K/8M 64K 16K 4K TMS320V 在片外围电路 DMA C5402. 主机接 根装载 内核电压 VO电压 缓冲串口 口 定时器 通道数 (引导装载) (V) (V) 100 (COM) 2 McBSP HPI8 2 6 Chan Int 是 1.8V 3.3V (5402A是3个) (5402A是1个) (5402A是1.6V) 12

TMS320VC5402芯片的结构及技术性能 型号 频率 MHz MIPS 指令周期 (ns) 寻址空间 片内存储器 程序 (16位) 数据 (16位) RAM (16位) ROM (16位) TMS320V C5402- 100 100 100 10 64K/8M 64K 16K 4K 在片外围电路 根装载 (引导装载) 内核电压 (V) I/O电压 缓冲串口 (V) 主机接 口 (COM) 定时器 DMA 通道数 2 McBSP HPI8 2 6 Chan Int 是 1.8V 3.3V (5402A是3个) (5402A是1个) (5402A是1.6V) (5402A是160 MHz, 160 MIPS, 6.25ns) (5402A是16K) 12

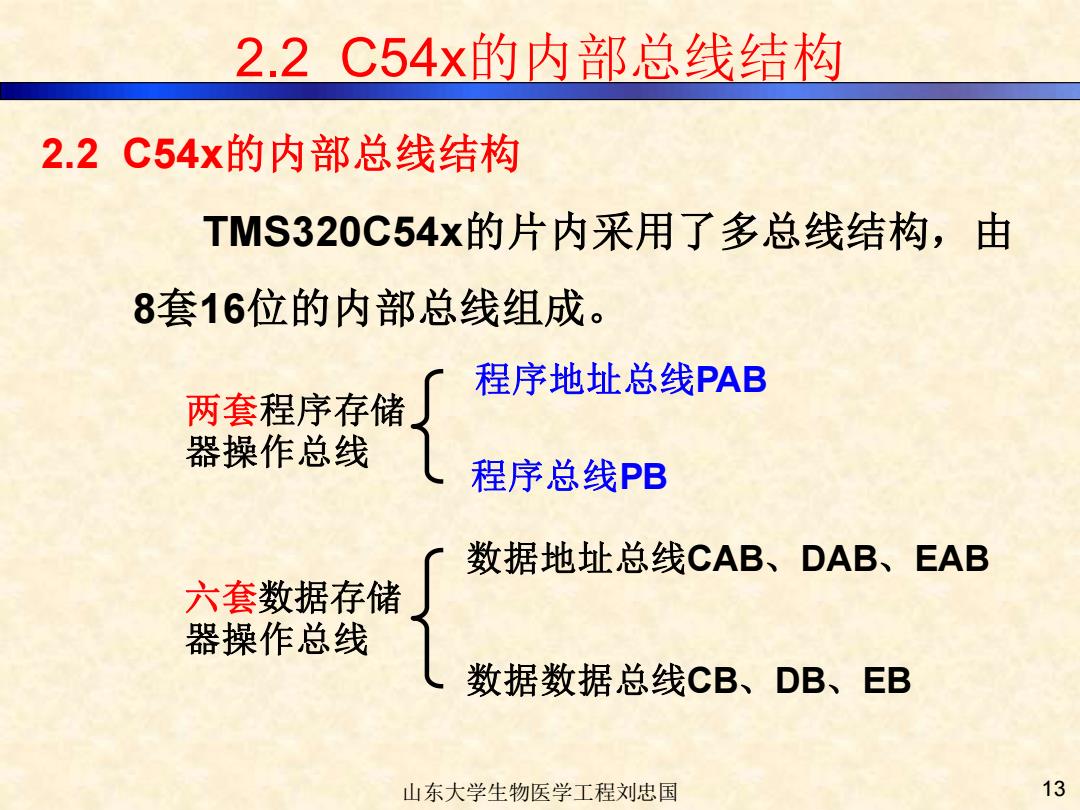

2.2C54x的内部总线结构 2.2C54x的内部总线结构 TMS320C54x的片内采用了多总线结构,由 8套16位的内部总线组成。 程序地址总线PAB 两套程序存储 器操作总线 程序总线PB 数据地址总线CAB、DAB、EAB 六套数据存储 器操作总线 数据数据总线CB、DB、EB 山东大学生物医学工程刘忠国 13

2.2 C54x的内部总线结构 TMS320C54x的片内采用了多总线结构,由 8套16位的内部总线组成。 两套程序存储 器操作总线 程序地址总线PAB 程序总线PB 六套数据存储 器操作总线 数据地址总线CAB、DAB、EAB 数据数据总线CB、DB、EB 13 2.2 C54x的内部总线结构 山东大学生物医学工程刘忠国

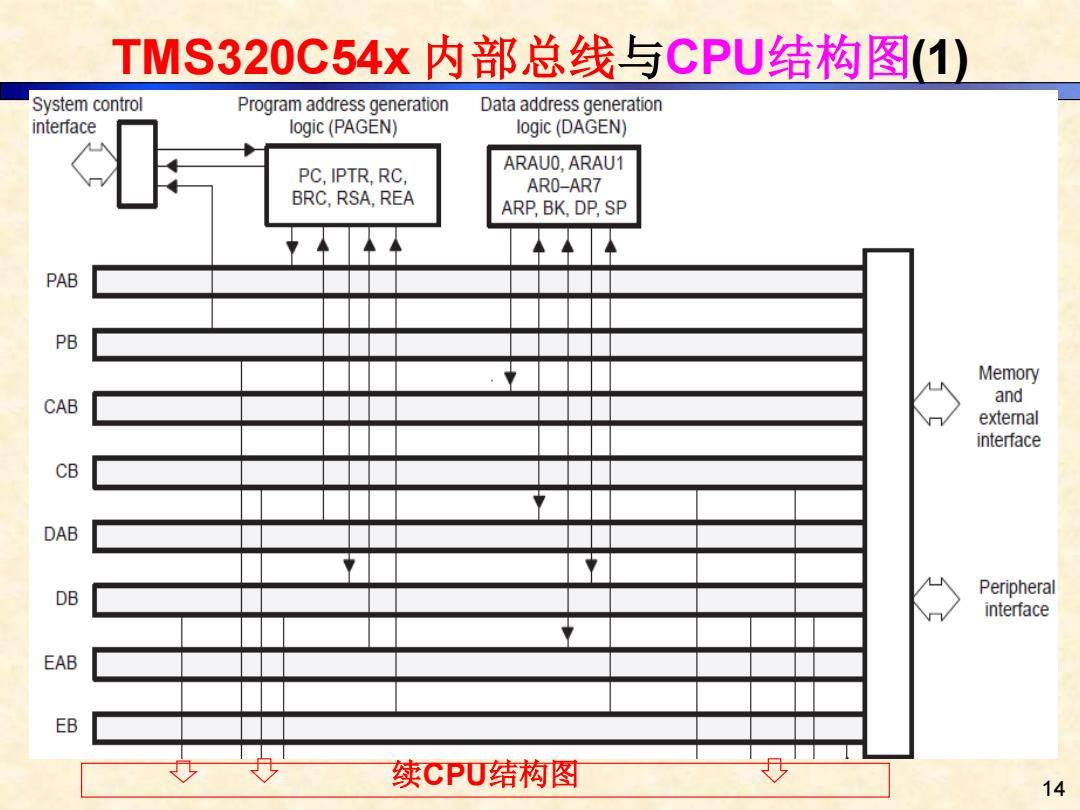

TMS320C54x内部总线与CPU结构图(1) System control Program address generation Data address generation interface logic(PAGEN) logic(DAGEN) ARAUO,ARAU1 PC,IPTR,RC, ARO-AR7 BRC,RSA,REA ARP,BK,DP,SP PAB PB Memory CAB and external interface CB DAB DB Peripheral interface EAB EB 续CPU结构图 14

TMS320C54x 内部总线与CPU结构图(1) 续CPU结构图 14

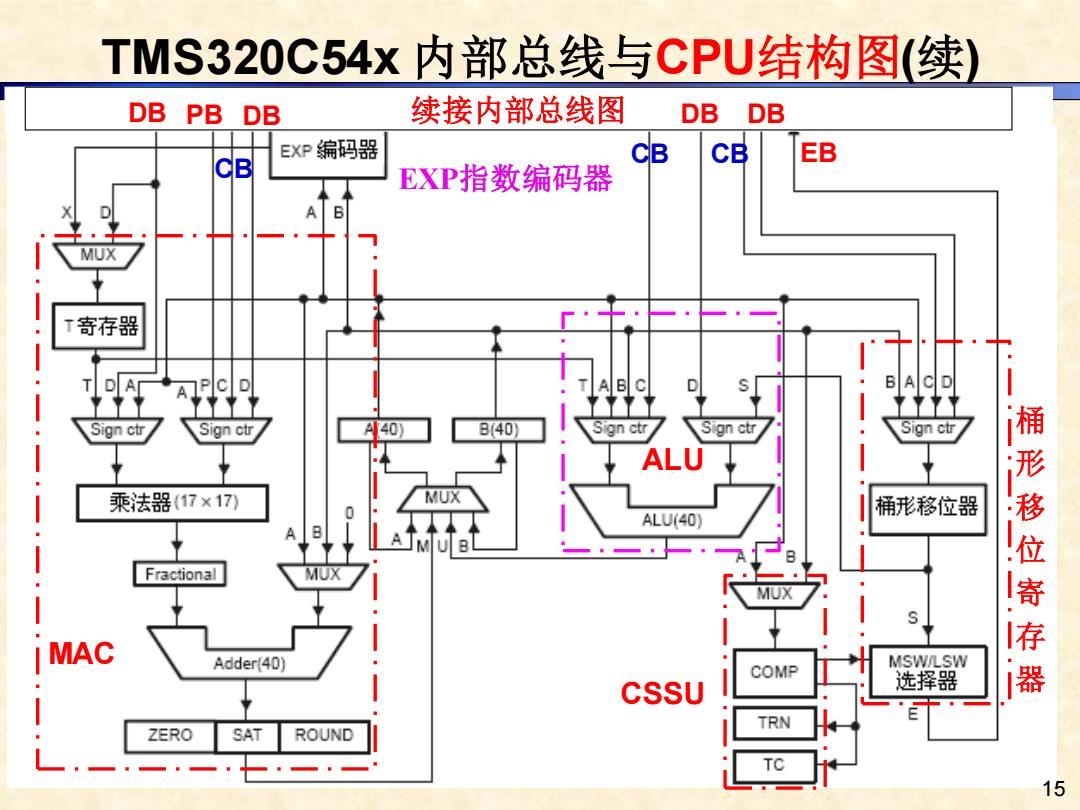

TMS320C54x内部总线与CPU结构图(续) DB PB DB 续接内部总线图 DB DB EXP编码器 CB CB EB CB EXP指数编码器 A B MUX ◆ T 寄存器 A PC D A B C Sign ctr Sign ctr 8(40の Sign ctr Sign ctr Sign ctr ALU 乘法器(17×17) MUX 桶形移位器 ALU(40 A Fractional MUX MUX 桶形移位寄存 MAC Adder(40) COMP MSW/LSW CSSU 选择器 TRN ZERO SAT ROUND TC 15

TMS320C54x 内部总线与CPU结构图(续) 续接内部总线图 15 DB PB DB CB DB CB DB CB MAC EXP指数编码器 CSSU ALU 桶 形 移 位 寄 存 器 EB