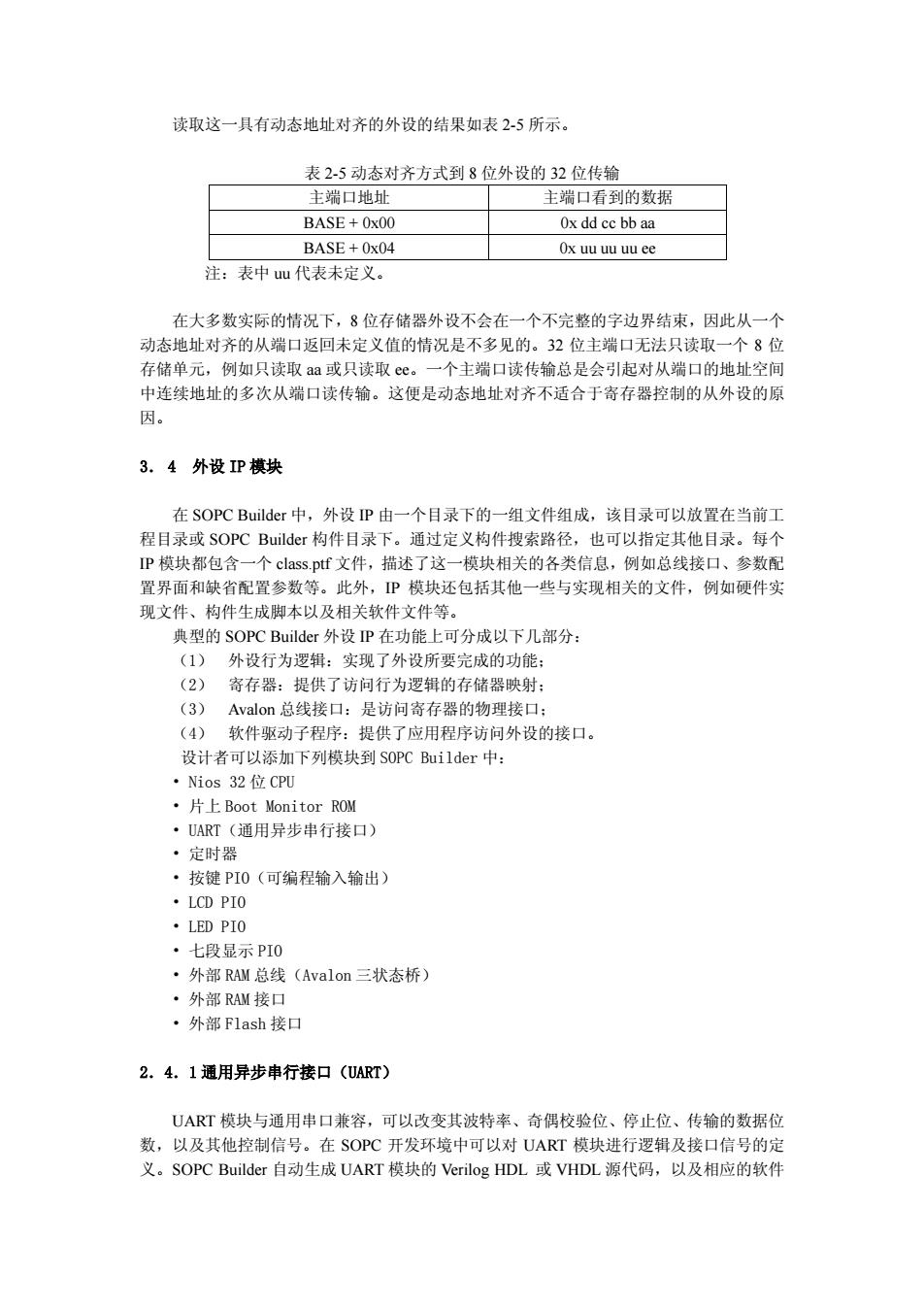

读取这一具有动态地址对齐的外设的结果如表2-5所示。 表2-5动态对齐方式到8位外设的32位传输 主端口地址 主端口看到的数据 BASE+0x00 Ox dd cc bb aa BASE +0x04 Ox uu uuuu ee 注:表中uu代表未定义。 在大多数实际的情况下,8位存储器外设不会在一个不完整的字边界结束,因此从一个 动态地址对齐的从端口返回未定义值的情况是不多见的。32位主端口无法只读取一个8位 存储单元,例如只读取aa或只读取ee。一个主端口读传输总是会引起对从端口的地址空间 中连续地址的多次从端口读传输。这便是动态地址对齐不适合于寄存器控制的从外设的原 因。 3.4外设P模块 在SOPC Builder中,外设P由一个目录下的一组文件组成,该目录可以放置在当前工 程目录或SOPC Builder构件目录下。通过定义构件搜索路径,也可以指定其他目录。每个 P模块都包含一个class.ptf文件,描述了这一模块相关的各类信息,例如总线接口、参数配 置界面和缺省配置参数等。此外,P模块还包括其他一些与实现相关的文件,例如硬件实 现文件、构件生成脚本以及相关软件文件等。 典型的SOPC Builder外设IP在功能上可分成以下几部分: (1)外设行为逻辑:实现了外设所要完成的功能: (2)寄存器:提供了访问行为逻辑的存储器映射: (3)Avalon总线接口:是访问寄存器的物理接口: (4)软件驱动子程序:提供了应用程序访问外设的接口。 设计者可以添加下列模块到SOPC Builder中: ·Nios32位CPU ·片上Boot Monitor ROM ·UART(通用异步串行接口) ·定时器 ·按键PI0(可编程输入输出) ·LCD PIO ·LED PIO ·七段显示PI0 ·外部RAM总线(Avalon三状态桥) ·外部RAM接口 ·外部Flash接口 2.4.1通用异步串行接口(UART) UART模块与通用串口兼容,可以改变其波特率、奇偶校验位、停止位、传输的数据位 数,以及其他控制信号。在SOPC开发环境中可以对UART模块进行逻辑及接口信号的定 义。SOPC Builder自动生成UART模块的Verilog HDL或VHDL源代码,以及相应的软件

读取这一具有动态地址对齐的外设的结果如表 2-5 所示。 表 2-5 动态对齐方式到 8 位外设的 32 位传输 主端口地址 主端口看到的数据 BASE + 0x00 0x dd cc bb aa BASE + 0x04 0x uu uu uu ee 注:表中 uu 代表未定义。 aa 或只读取 ee。一个主端口读传输总是会引起对从端口的地址空间 中连 3. 的一组文件组成,该目录可以放置在当前工 程目录或 SOPC Builder 构件目录下。通过定义构件搜索路径,也可以指定其他目录。每个 class.ptf 文件,描述了这一模块相关的各类信息,例如总线接口、参数配 界面和缺省配置参数等。此外,IP 模块还包括其他一些与实现相关的文件,例如硬件实 现文件、构件生成脚本以及相关软 典型的 SOPC Builder 外设 IP 在功能上可分成以下几部分: (1) 外设行为逻辑:实现了外设所要完成的功能; (2) 寄存器:提供了访问行为逻辑的存储器映射; (3) Avalon 总线接口:是访问寄存器的物理接口; (4) 软件驱动子程序:提供了应用程序访问外设的接口。 设计者可以添加下列模块到 SOPC Builder 中: • Nios 32 位 CPU • 片上 Boot Monitor ROM • 按键 PIO(可编程输入输出) 2.4 1 通用异步串行接口(UART) 在大多数实际的情况下,8 位存储器外设不会在一个不完整的字边界结束,因此从一个 动态地址对齐的从端口返回未定义值的情况是不多见的。32 位主端口无法只读取一个 8 位 存储单元,例如只读取 续地址的多次从端口读传输。这便是动态地址对齐不适合于寄存器控制的从外设的原 因。 4 外设 IP 模块 在 SOPC Builder 中,外设 IP 由一个目录下 IP 模块都包含一个 置 件文件等。 • UART(通用异步串行接口) • 定时器 • LCD PIO • LED PIO • 七段显示 PIO • 外部 RAM 总线(Avalon 三状态桥) • 外部 RAM 接口 • 外部 Flash 接口 . UART 模块与通用串口兼容,可以改变其波特率、奇偶校验位、停止位、传输的数据位 数,以及其他控制信号。在 SOPC 开发环境中可以对 UART 模块进行逻辑及接口信号的定 义。SOPC Builder 自动生成 UART 模块的 Verilog HDL 或 VHDL 源代码,以及相应的软件

接口子程序。 (1)功能描述 Nios Uart用于在Altera的FPGA中实现简单的RS-232异步发送和接收逻辑。UART通过 两个外部引脚(TxD和RxD)发送和接收串口数据。软件通过五个16位寄存器对UART进行控 制,以完成串行口通信。 为了与RS-232的电压信号相匹配,在RxD/TxD输入输出引脚与相应的外部RS-232连接 之间需要有电平转换芯片(如LTC-1386)。RxD/TxD输入输出引脚允许的电压范围根据Altera 器件的引脚配置决定。UART采用同步的单一时钟输入(ck)。 UART外设可以连接到DMA控制器上,这种方式允许在UART与存储器之间进行流模式 数据传输。 可以为模拟定制UART外设。在高速系统模拟时,UART的模拟则显得特别慢。为了提 高模拟速度,UART在模拟时可以采用较小的波特率分频值,使得UART运行在一半的系统 时钟速度上。 ·传送逻辑 UART传送逻辑含有一个7位、8位或9位的txdata保持寄存器,以及一个7位、8位 或9位的传送移位寄存器(寄存器的数据位数由PTF参数data bits决定)。软件可以直接写 入txdata保持寄存器。在未进行串行传输移位操作时,txdata保持寄存器中的值会自动装入 到传送移位寄存器。传送移位寄存器直接连接到TxD数据引脚,数据的LSB首先移出到 TxD。 保持和移位两个寄存器提供双重缓冲。软件可以在前一个字符正在移出时向txdata寄存 器写入新的数据。软件可以读取status寄存器的trdy位(传送器准备好)、tmt位(传送移位寄 存器空)和to位(传送溢出错误),从而监视传送器的状态。 传送逻辑可以自动根据RS-232通信协议在连续的TxD数据流中插入正确的开始位、停 止位和奇偶校验位。具体的参数在PT℉文件中进行定义。 ·接收逻辑 UART接收逻辑含有一个7位、8位或9位的接收移位寄存器,以及一个7位、8位或9位的 xdata保持寄存器(寄存器的数据位数由PTF文件中的data bits参数决定)。软件可以直接读取 xdata保持寄存器,每当一个新的字符完全接收后,接收移位寄存器自动向xdata保持寄存器 装载新的数据。 接收和移位两个寄存器提供双重缓冲,xdata寄存器可以保持前一个收到的字符同时在 接收移位寄存器中移入下一个字符。 软件可以读取status寄存器的rrdy位(读准备好)、roe位(接收溢出错误)、brk位(检测到 停顿)、p心位(奇偶校验错)和fe位(帧错误),从而监视接收器的状态。接收逻辑根据RS-232 通信协议在连续的RxD数据流中自动检测正确的开始位、停止位和奇偶校验位,并且根据 接收数据中的四种异常情况自动设置status寄存器中的相应位(fe、pe、roe或brk)。 ·波特率生成 UART的内部波特时钟根据UART的主时钟输入,也就是Avalon总线的系统时钟来生成。 其速率由一个时钟分频器决定。分频器的值可以由以下的方式确定: (a)由UART的PTF参数baud以及系统的PTF参数clock freq共同决定的常量 (b)主机可设置的16位divisor寄存器值

接口子程序。 (1)功能描述 Nios UART用于在Altera的FPGA中实现简单的RS-232异步发送和接收逻辑。UART通过 两个外部引脚(TxD和RxD)发送和接收串口数据。软件通过五个16位寄存器对UART进行控 制,以完成串行口通信。 为了与RS-232的电压信号相匹配,在RxD/TxD输入输出引脚与相应的外部RS-232连接 之间需要有电平转换芯片(如LTC-1386)。RxD/TxD输入输出引脚允许的电压范围根据Altera 器件 得UART运行在一半的系统 时钟速度上。 · 传送逻辑 UART 传送逻辑含有一个 7 位 位或 9 存器,以及一个 7 位、8 位 或 9 位的传送移位寄存器(寄存器的 位数 data_bits 决定)。软件可以直接写 入 txdata 保持寄存器。在未进行串 输移位 ata 保持寄存器中的值会自动装入 到传送移位寄存器。 送移位寄存 接连接 LSB 首先移出到 TxD。 保持和移位两个寄存器提供双重缓冲。软件可以在前一个字符正在移出时向 txdata 寄存 器写入新的数据。软件可以读取 s 存器 送器准备好)、tmt 位(传送移位寄 存器空)和 toe 位(传送溢出错误), 视传 传送逻辑可以自动根据 RS-232 信协议在连续的 TxD 数据流中插入正确的开始位、停 止位和奇偶校验位。 体的参数在 文件中进行定义。 · 接收逻辑 UART接收逻辑含有一个7位、 9位的接收移位寄存器,以及一个7位、8位或9位的 存器(寄存器的数据位数由PTF文件中的data_bits参数决定)。软件可以直接读取 rxdat rxdata保持寄存器 装载新的数据。 以读取 status 寄存器的 rrdy 位(读准备好)、roe 位(接收溢出错误)、brk 位(检测到 停顿 baud以及系统的PTF参数 共同决定的常量 设置的16 divisor寄存器值。 的引脚配置决定。UART采用同步的单一时钟输入(clk)。 UART外设可以连接到DMA控制器上,这种方式允许在UART与存储器之间进行流模式 数据传输。 可以为模拟定制UART外设。在高速系统模拟时,UART的模拟则显得特别慢。为了提 高模拟速度,UART在模拟时可以采用较小的波特率分频值,使 、8 位的 txdata 保持寄 数据 由 PTF 参数 行传 操作时,txd 传 器直 到 TxD 数据引脚,数据的 tatus 寄 的 trdy 位(传 从而监 送器的状态。 通 具 PTF 8位或 rxdata保持寄 a保持寄存器,每当一个新的字符完全接收后,接收移位寄存器自动向 接收和移位两个寄存器提供双重缓冲,rxdata 寄存器可以保持前一个收到的字符同时在 接收移位寄存器中移入下一个字符。 软件可 )、pe 位(奇偶校验错)和 fe 位(帧错误),从而监视接收器的状态。接收逻辑根据 RS-232 通信协议在连续的 RxD 数据流中自动检测正确的开始位、停止位和奇偶校验位,并且根据 接收数据中的四种异常情况自动设置 status 寄存器中的相应位(fe、pe、roe 或 brk)。 · 波特率生成 UART的内部波特时钟根据UART的主时钟输入,也就是Avalon总线的系统时钟来生成。 其速率由一个时钟分频器决定。分频器的值可以由以下的方式确定: (a)由UART的PTF参数 clock_freq (b)主机可 位

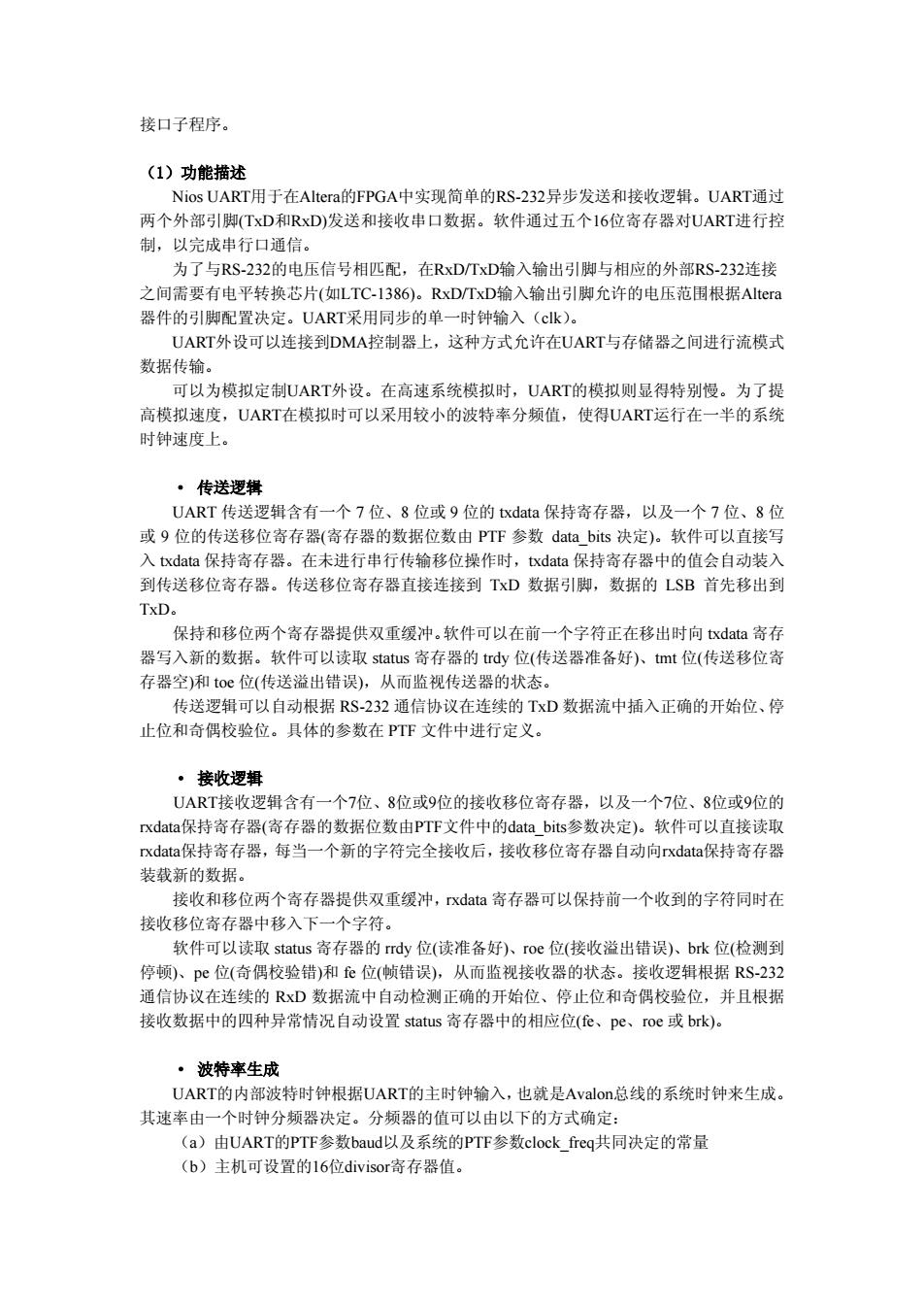

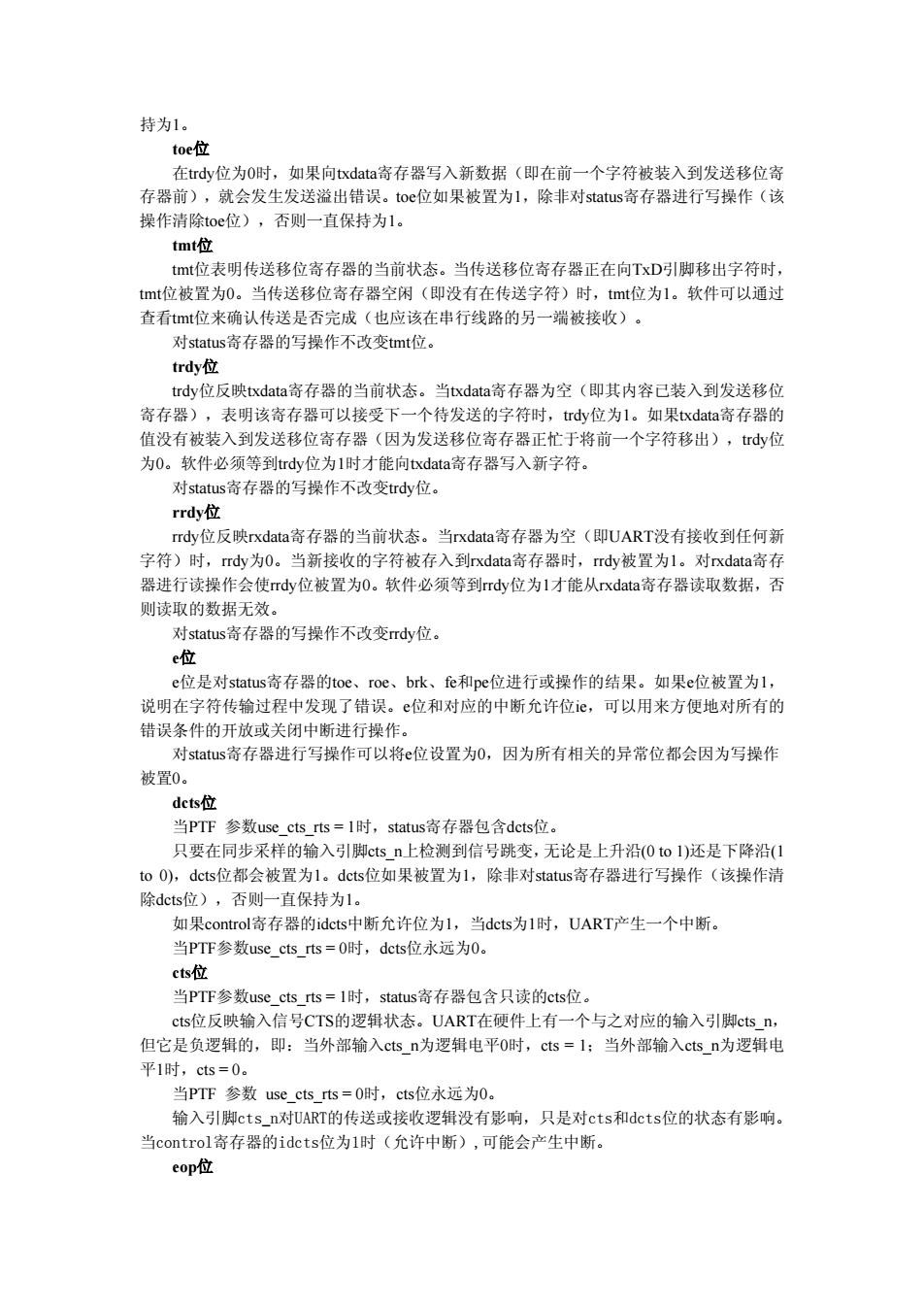

当UART的PTF参数fixed baud为0时,UART使用一个主机可设置的16位divisor寄存器。 当UART的PTF参数fixed baud为l时,UART使用固定的波特率值。 ·中断输出 UART产生一个IRQ输出信号作为其Avalon总线接口的一部分。当一个或多个内部条件 发生,并且对应的control寄存器的中断允许位也为1时,UART发出一个中断请求。在复位 时,所有的中断允许位设置为0。因此,只有软件将一个或多个中断允许位设置为1时,UART 才能发出中断请求。 每一个可能的中断条件都在status寄存器和control寄存器中有相应的位。当发生任何中 断条件时,相应的状态位设置为1并且一直保持为l,直到软件清除status寄存器。软件向status 寄存器进行写操作就可以清除status寄存器(忽略写入的值)。 所有可能的中断条件以及相应的status和control(中断允许)位都列在表6.6和表6.7中。 每个条件的详细信息在每个状态位的描述中给出。当状态位设置为1并且control寄存器中的 中断允许位也为1时,RQ输出会置为有效。 (2)UART寄存器 表2-6UART寄存器表 A2.A0 Register R/W Description/Register Bits Name 15.121109876543210 0 rxdata RO RxData txdata WO TxData 2 status (1) RW eop cts dcts-e(2)rrdy trdy tmt toe roe brk fe pe 3 control RW ieop rts idcts trbk ieirrdy itrdy itmt itoe iroe ibrk ife ipe 4 divisor RW Baud Rate Divisor(optional) endofpacket RW End-packet value 注:(I)对status寄存器的写操作会清除dcts,e,toe,roe,brk,fe,和pe位 (2)status寄存器的第八位(e)是toe、roe、brk、fe、和pe位的逻辑”或” ·rxdata寄存器 软件可以从rxdata寄存器读取收到的字符。每当UART从RxD引脚接收到一个新字符, 就将其存入rxdata寄存器,同时把status寄存器的rrdy位设置为l。当软件读取rxdata寄存器时, status寄存器中的rdy位被清零。在rrdy位为I的情况下(即软件未将rxdata寄存器中的数据读 走),如果下一个字符被存入xdata寄存器,就会发生接收溢出错误(status寄存器的roe位 被置为1)。不论软件是否己经读取原有数据,新的字符总会被存入rxdata寄存器(因此数据 有被覆盖的可能)。向xdata寄存器写入数据没有任何作用。 ·txdata寄存器 软件可直接向txdata寄存器写入要发送的字符。只有当发送逻辑准备好传送一个新的字 符时(由status寄存器的trdy位表示),新字符才能写入txdata寄存器。如果在trdy为O时,将 一个字符写入txdata寄存器会产生未知的结果。向tⅸdata寄存器写入一个字符会使trdy被置为 0,当该字符从txdata寄存器装入到发送移位寄存器中时,trdy被置为1。 假定起始状态时UART空闲。软件将第一个字符写入txdata寄存器后trdy被置为0,当字 符从txdata寄存器装入到发送移位寄存器中时,trdy设置为l。此时软件可以向txdata寄存器写

当UART的PTF参数fixed_baud为0时,UART使用一个主机可设置的16位divisor寄存器。 当UART的PTF参数fixed_baud为1时,UART使用固定的波特率值。 · 中断输出 产生一个IRQ输出信号作为其Avalon总线接口的一部分。当一个或多个内部条件 发生 可能的中断条件都在status寄存器和control寄存器中有相应的位。当发生任何中 断条 表6.6和表6.7中。 每个条件的详细信息在每个状态位的描述中给出。当状态位设置为1并且control寄存器中的 中断允许位也为1时,IRQ输出会置为有效。 UART ,并且对应的control寄存器的中断允许位也为1时,UART发出一个中断请求。在复位 时,所有的中断允许位设置为0。因此,只有软件将一个或多个中断允许位设置为1时,UART 才能发出中断请求。 每一个 件时,相应的状态位设置为1并且一直保持为1,直到软件清除status寄存器。软件向status 寄存器进行写操作就可以清除status寄存器(忽略写入的值)。 所有可能的中断条件以及相应的status和control(中断允许)位都列在 (2)UART寄存器 表 2-6 UART 寄存器表 注: 可以从rxdata寄存器读取收到的字符。每当UART从RxD引脚接收到一个新字符, 就将 a寄存器,同时把status寄存器的rrdy位设置为1。当软件读取rxdata寄存器时, statu 将rxdata寄存器中的数据读 走) 器写入数据没有任何作用。 直接向txdata寄存器写入要发送的字符。只有当发送逻辑准备好传送一个新的字 符时 。如果在trdy为0时,将 一个 时UART空闲。软件将第一个字符写入txdata寄存器后trdy被置为0,当字 符从 置为1。此时软件可以向txdata寄存器写 (1) 对status寄存器的写操作会清除dcts, e, toe, roe, brk, fe,和 pe 位 (2) status寄存器的第八位(e)是toe、roe、brk、fe、和 pe位的逻辑”或” · rxdata 寄存器 软件 其存入rxdat s寄存器中的rrdy位被清零。在rrdy位为1的情况下(即软件未 ,如果下一个字符被存入rxdata寄存器,就会发生接收溢出错误(status寄存器的roe位 被置为1)。不论软件是否已经读取原有数据,新的字符总会被存入rxdata寄存器(因此数据 有被覆盖的可能)。向rxdata寄存 · txdata寄存器 软件可 (由status寄存器的trdy位表示),新字符才能写入txdata寄存器 字符写入txdata寄存器会产生未知的结果。向txdata寄存器写入一个字符会使trdy被置为 0,当该字符从txdata寄存器装入到发送移位寄存器中时,trdy被置为1。 假定起始状态 txdata寄存器装入到发送移位寄存器中时,trdy设

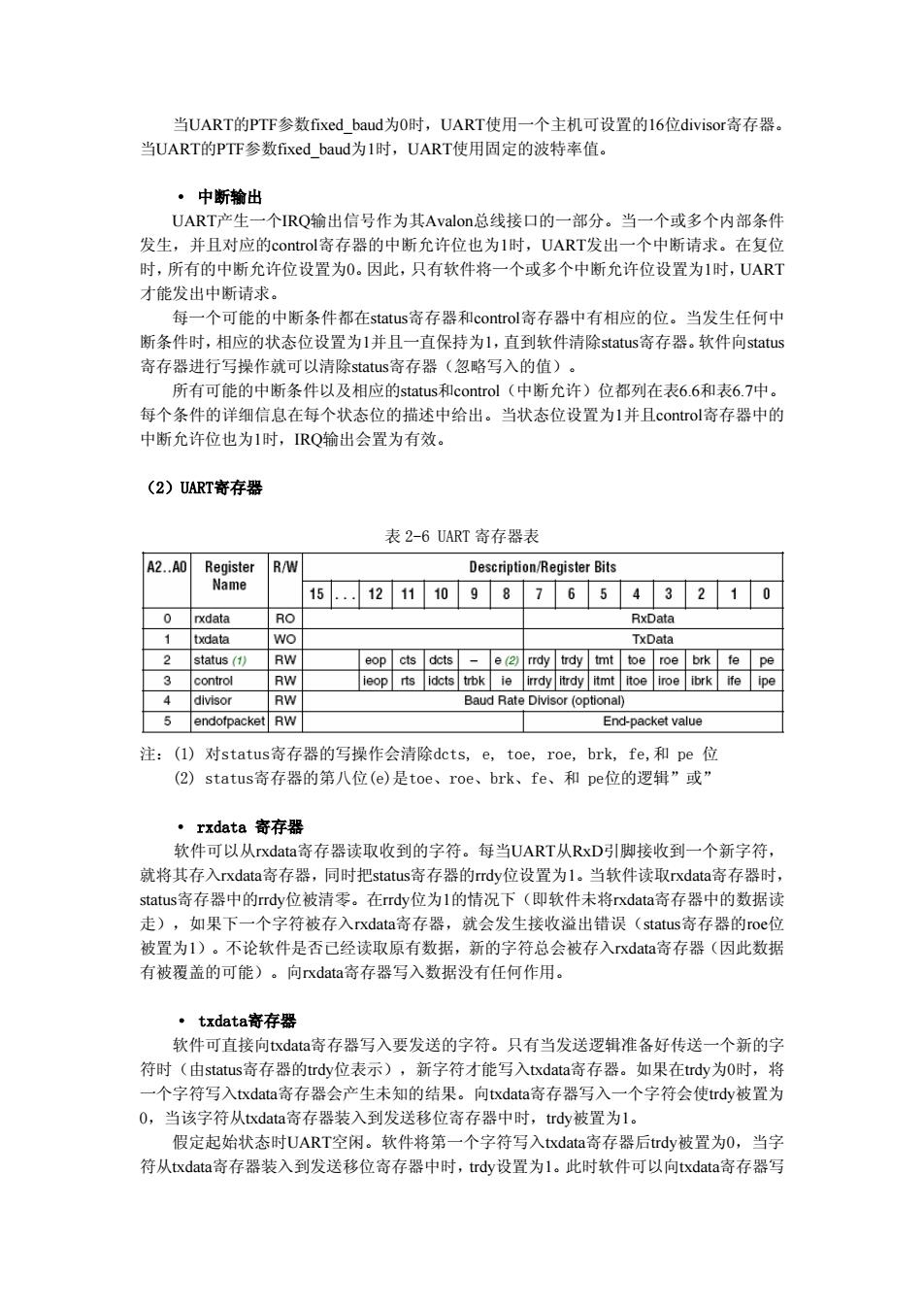

入第二个字符,ty再次被置为0。但是此时第一个字符仍旧占用着发送移位寄存器,其数 据仍然在低速地从TxD引脚发送。tdy位直到第一个字符完全被移出后才被置为1,然后第二 个字符被自动装入到传送移位寄存器中。从txdata寄存器读数据会得到未知的结果。 ·statusi寄存器 status寄存器由多个独立的状态位组成,反映UART内部状态。软件可以随时读取status 寄存器,而不会改变status寄存器的任何位。状态位与control寄存器的中断允许位一一对应。 当某个中断允许位为1时,如果与之对应的状态位为1,则会引起中断请求。 向status寄存器进行写操作时(写入的值被忽略),大多数状态位会被置为0。具体请 参考下面对每一位的描述。表2-7列出了status寄存器的位。 表2-7 status寄存器的位 位 名称 描 述 0 pe 奇偶校验位错误 1 fe 帧错误 2 brk 检测到停顿 3 roe 接收溢出错误 4 toe 传送溢出错误 5 tmt 发送寄存器为空 6 trdy 传送准备好 7 rrdy 接收字符准备好 8 e 异常 10 dcts 检测到CTS信号变化 11 cts CTS信号 12 eop 发生End of packet事件 pe位 若接收到的校验位不正确,会产生奇偶校验位错误,p位被置为l。 如果PTF参数parity为N”,不进行奇偶校验位检测,pe位永远为0。 pe位如果被置为1,除非对status寄存器进行写操作(该操作清除pe位),否则一直保持 为1。 fe位 当接收器不能检测到一个正确的停止位时,便发生帧错误。当UART收到一个含错误的 停止位的字符时,fe位被置为l。fe位如果被置为1,除非对status寄存器进行写操作(该操作 清除fe位),否则一直保持为l。当pe或fe位为l时,读xdata寄存器的值会产生未知结果。 brk位 当RxD连续保持低电平(逻辑0)的时间超过接收一个完整字符的时间(7、8或9位,再 加上起始位、停止位和奇偶校验位的周期)时,接收器认为检测到一个接收停顿。如果检测 到停顿,brk位设置为l。brk位如果被置为l,除非对status寄存器进行写操作(该操作清除brk 位),否则一直保持为1。 roe位 如果rxdata寄存器中的数据未被读取(这时候rrdy位为l),UART又接受到新的数据,就 会发生接收溢出错误。在这种情况下,roe位设置为l,同时rxdata寄存器的内容被新数据覆 盖。roe位如果被置为l,除非对status寄存器进行写操作(该操作清除roe位),否则一直保

入第 才被置为1,然后第二 个字符被自动装入到传送移位寄存器中。从txdata寄存器读数据会得到未知的结果。 tus寄存器 映UART内部状态。软件可以随时读取status 寄存 态位与control寄存器的中断允许位一一对应。 当某 表 2-7 status 寄存器的位 名 称 描 述 二个字符,trdy再次被置为0。但是此时第一个字符仍旧占用着发送移位寄存器,其数 据仍然在低速地从TxD引脚发送。trdy位直到第一个字符完全被移出后 · sta status寄存器由多个独立的状态位组成,反 器,而不会改变status寄存器的任何位。状 个中断允许位为1时,如果与之对应的状态位为1,则会引起中断请求。 向 status 寄存器进行写操作时(写入的值被忽略),大多数状态位会被置为0。具体请 参考下面对每一位的描述。表 2-7 列出了 status 寄存器的位。 位 0 pe 奇偶校验位错误 1 fe 帧错误 2 brk 检测到停顿 3 roe 接收溢出错误 4 toe 传送溢出错误 5 mt t 发送寄存器为空 6 trdy 传送准备好 7 rrdy 接收字符准备好 8 e 异常 10 dcts 检测到CTS信号变化 11 cts CTS 信号 12 eop 发生End of packet事件 pe位 若接收到的校验位不正确,会产生奇偶校验位错误,pe位被置为1。 如果PTF参数 ity为“N” 进行 测,pe位永远为0。 pe位如果被置 ,除非 us寄 除pe位),否则一直保持 为1。 fe位 当接收器不能检测到一个正确的停止位时,便发生帧错误。当UART收到一个含错误的 停止 写操作(该操作 清除 位、停止位和奇偶校验位的周期)时,接收器认为检测到一个接收停顿。如果检测 到停 1。brk位如果被置为1,除非对status寄存器进行写操作(该操作清除brk 位) dy位为1),UART又接受到新的数据,就 会发 溢出错误。在这种情况下,roe位设置为1,同时rxdata寄存器的内容被新数据覆 盖。 操作清除roe位),否则一直保 par ,不 奇偶校验位检 为1 对stat 存器进行写操作(该操作清 位的字符时,fe位被置为1。fe位如果被置为1,除非对status寄存器进行 fe位),否则一直保持为1。当pe或fe位为1时,读rxdata寄存器的值会产生未知结果。 brk位 当RxD连续保持低电平(逻辑0)的时间超过接收一个完整字符的时间(7、8或9位,再 加上起始 顿,brk位设置为 ,否则一直保持为1。 roe位 如果rxdata寄存器中的数据未被读取(这时候rr 生接收 roe位如果被置为1,除非对status寄存器进行写操作(该

持为1。 toe位 在trdy位为0时,如果向txdata寄存器写入新数据(即在前一个字符被装入到发送移位寄 存器前),就会发生发送溢出错误。toe位如果被置为l,除非对status寄存器进行写操作(该 操作清除toe位),否则一直保持为l。 tmt位 tmt位表明传送移位寄存器的当前状态。当传送移位寄存器正在向TxD引脚移出字符时, tmt位被置为0。当传送移位寄存器空闲(即没有在传送字符)时,tmt位为1。软件可以通过 查看tmt位来确认传送是否完成(也应该在串行线路的另一端被接收)。 对status寄存器的写操作不改变tmt位。 trdy位 trdy位反映txdata寄存器的当前状态。当txdata寄存器为空(即其内容已装入到发送移位 寄存器),表明该寄存器可以接受下一个待发送的字符时,try位为l。如果xdata寄存器的 值没有被装入到发送移位寄存器(因为发送移位寄存器正忙于将前一个字符移出),y位 为0。软件必须等到trdy位为l时才能向txdata寄存器写入新字符。 对status寄存器的写操作不改变trdy位。 rrdy位 rrdy位反映rxdata寄存器的当前状态。当rxdata寄存器为空(即UART没有接收到任何新 字符)时,rdy为0。当新接收的字符被存入到xdata寄存器时,rdy被置为l。对xdata寄存 器进行读操作会使rdy位被置为0。软件必须等到rrdy位为l才能从xdata寄存器读取数据,否 则读取的数据无效。 对status寄存器的写操作不改变rrdy位。 e位 e位是对status寄存器的toe、roe、brk、fe和pe位进行或操作的结果。如果e位被置为1, 说明在字符传输过程中发现了错误。e位和对应的中断允许位,可以用来方便地对所有的 错误条件的开放或关闭中断进行操作。 对status寄存器进行写操作可以将e位设置为0,因为所有相关的异常位都会因为写操作 被置0。 dcts位 当PTF参数use cts rts=I时,status寄存器包含dcts位。 只要在同步采样的输入引脚ctsn上检测到信号跳变,无论是上升沿(0to1)还是下降沿(1 to0),dcts位都会被置为l。dcts位如果被置为1,除非对status寄存器进行写操作(该操作清 除dcts位),否则一直保持为1。 如果control寄存器的idcts中断允许位为l,当dcts为1时,UART产生一个中断。 当PTF参数use cts rts=O时,dcts位永远为0。 cts位 当PTF参数use cts rts=l时,status寄存器包含只读的cts位。 cts位反映输入信号CTS的逻辑状态。UART在硬件上有一个与之对应的输入引脚cts_n, 但它是负逻辑的,即:当外部输入ctsn为逻辑电平0时,cts=1;当外部输入ctsn为逻辑电 平1时,cts=0。 当PTF参数use cts rts=O时,cts位永远为0。 输入引脚ctsn对UART的传送或接收逻辑没有影响,只是对cts和dcts位的状态有影响。 当control寄存器的idcts位为1时(允许中断),可能会产生中断。 eop位

持为 被装入到发送移位寄 存器 则一直保持为1。 t位 存器的当前状态。当传送移位寄存器正在向TxD引脚移出字符时, tmt位 atus寄存器的写操作不改变tmt位。 寄存器的当前状态。当txdata寄存器为空(即其内容已装入到发送移位 存 时,trdy位为1。如果txdata寄存器的 值没 寄存器正忙于将前一个字符移出),trdy位 为0。软件必须等到trdy位为1时才能向txdata寄存器写入新字符。 改变trdy位。 rrdy位反映rxdata寄存器的当前状态。当rxdata寄存器为空(即UART没有接收到任何新 收的字符被存入到rxdata寄存器时,rrdy被置为1。对rxdata寄存 器进行读操作会使rrdy位被置为0。软件必须等到rrdy位为1才能从rxdata寄存器读取数据,否 则读 位。 e位 e位 行或操作的结果。如果e位被置为1, 说明在 断允许位ie,可以用来方便地对所有的 错误条 对 常位都会因为写操作 被置0。 当PTF 参数use_cts_rts = 1时,status寄存器包含dcts位。 果control寄存器的idcts中断允许位为1,当dcts为1时,UART产生一个中断。 当PTF参数use_cts_rts = 0时,d us 存器包含只读的cts位。 输入 入引脚cts_n, 逻辑电平0时,cts = 1;当外部输入cts_n为逻辑电 。 eop位 1。 toe位 在trdy位为0时,如果向txdata寄存器写入新数据(即在前一个字符 前),就会发生发送溢出错误。toe位如果被置为1,除非对status寄存器进行写操作(该 操作清除toe位),否 tm tmt位表明传送移位寄 被置为0。当传送移位寄存器空闲(即没有在传送字符)时,tmt位为1。软件可以通过 查看tmt位来确认传送是否完成(也应该在串行线路的另一端被接收)。 对st trdy位 trdy位反映txdata 寄 器),表明该寄存器可以接受下一个待发送的字符 有被装入到发送移位寄存器(因为发送移位 对status寄存器的写操作不 rrdy位 字符)时,rrdy为0。当新接 取的数据无效。 对status寄存器的写操作不改变rrdy 是对status寄存器的toe、roe、brk、fe和pe位进 字符传输过程中发现了错误。e位和对应的中 件的开放或关闭中断进行操作。 status寄存器进行写操作可以将e位设置为0,因为所有相关的异 dcts位 只要在同步采样的输入引脚cts_n上检测到信号跳变,无论是上升沿(0 to 1)还是下降沿(1 to 0),dcts位都会被置为1。dcts位如果被置为1,除非对status寄存器进行写操作(该操作清 除dcts位),否则一直保持为1。 如 cts位永远为0。 cts位 当PTF参数 e_cts_rts = 1时,status寄 cts位反映 信号CTS的逻辑状态。UART在硬件上有一个与之对应的输 但它是负逻辑的,即:当外部输入cts_n为 平1时,cts = 0 当PTF 参数 use_cts_rts = 0时,cts位永远为0。 输入引脚cts_n对UART的传送或接收逻辑没有影响,只是对cts和dcts位的状态有影响。 当control寄存器的idcts位为1时(允许中断),可能会产生中断