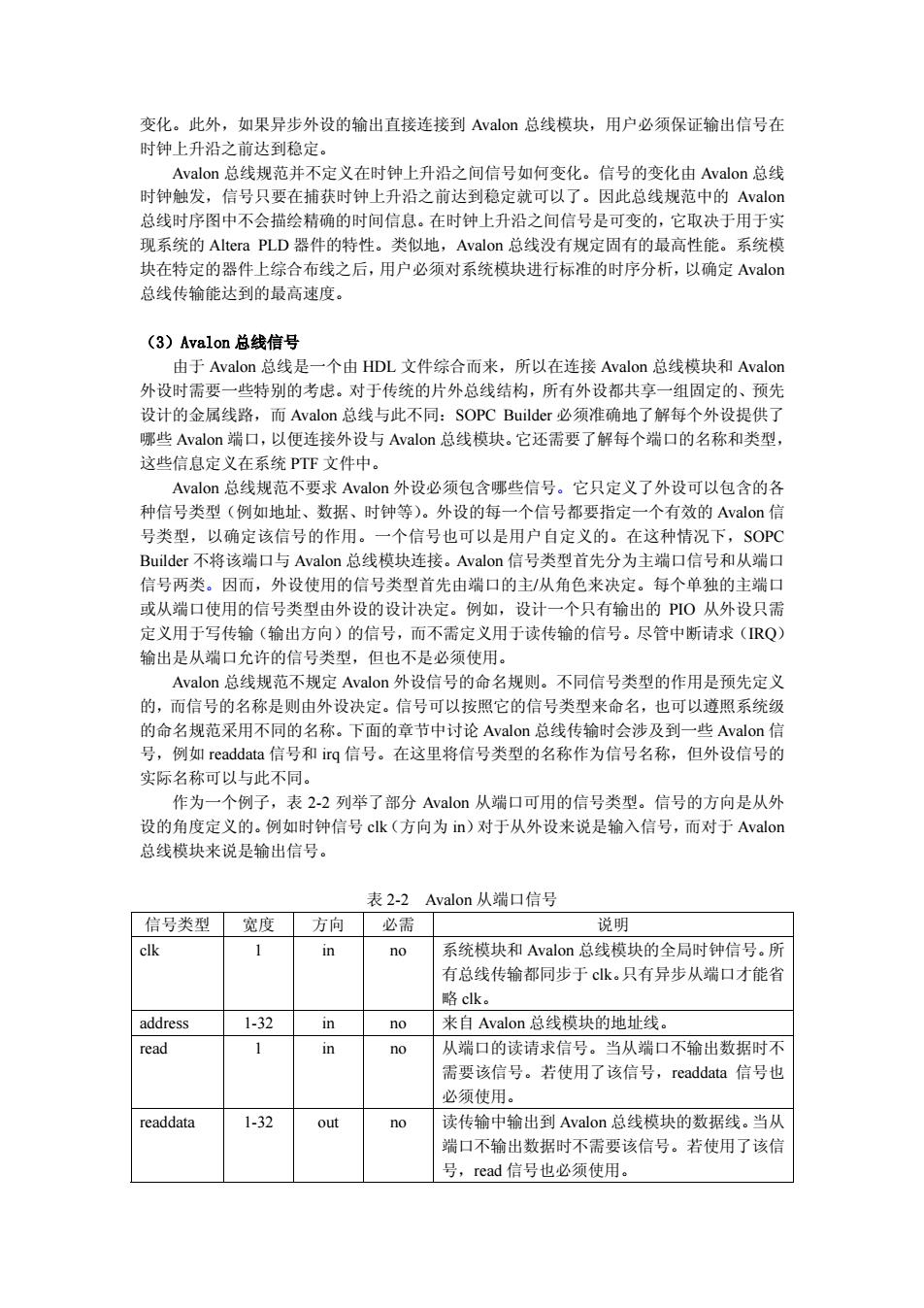

变化。此外,如果异步外设的输出直接连接到Avalon总线模块,用户必须保证输出信号在 时钟上升沿之前达到稳定。 Avalon总线规范并不定义在时钟上升沿之间信号如何变化。信号的变化由Avalon总线 时钟触发,信号只要在捕获时钟上升沿之前达到稳定就可以了。因此总线规范中的Avalon 总线时序图中不会描绘精确的时间信息。在时钟上升沿之间信号是可变的,它取决于用于实 现系统的Altera PLD器件的特性。类似地,Avalon总线没有规定固有的最高性能。系统模 块在特定的器件上综合布线之后,用户必须对系统模块进行标准的时序分析,以确定Avalon 总线传输能达到的最高速度。 (3)Avalon总线信号 由于Avalon总线是一个由HDL文件综合而来,所以在连接Avalon总线模块和Avalon 外设时需要一些特别的考虑。对于传统的片外总线结构,所有外设都共享一组固定的、预先 设计的金属线路,而Avalon总线与此不同:SOPC Builder必须准确地了解每个外设提供了 哪些Avalon端口,以便连接外设与Avalon总线模块。它还需要了解每个端口的名称和类型, 这些信息定义在系统PTF文件中。 Avalon总线规范不要求Avalon外设必须包含哪些信号。它只定义了外设可以包含的各 种信号类型(例如地址、数据、时钟等)。外设的每一个信号都要指定一个有效的Avalon信 号类型,以确定该信号的作用。一个信号也可以是用户自定义的。在这种情况下,SO℃ Builder不将该端口与Avalon总线模块连接。Avalon信号类型首先分为主端口信号和从端口 信号两类。因而,外设使用的信号类型首先由端口的主/从角色来决定。每个单独的主端口 或从端口使用的信号类型由外设的设计决定。例如,设计一个只有输出的PO从外设只需 定义用于写传输(输出方向)的信号,而不需定义用于读传输的信号。尽管中断请求(RQ) 输出是从端口允许的信号类型,但也不是必须使用。 Avalon总线规范不规定Avalon外设信号的命名规则。不同信号类型的作用是预先定义 的,而信号的名称是则由外设决定。信号可以按照它的信号类型来命名,也可以遵照系统级 的命名规范采用不同的名称。下面的章节中讨论Avalon总线传输时会涉及到一些Avalon信 号,例如readdata信号和irg信号。在这里将信号类型的名称作为信号名称,但外设信号的 实际名称可以与此不同。 作为一个例子,表2-2列举了部分Avalon从端口可用的信号类型。信号的方向是从外 设的角度定义的。例如时钟信号ck(方向为in)对于从外设来说是输入信号,而对于Avalon 总线模块来说是输出信号。 表2-2 Avalon从端口信号 信号类型 宽度 方向 必需 说明 clk in no 系统模块和Avalon总线模块的全局时钟信号。所 有总线传输都同步于ck。只有异步从端口才能省 略c。 address 1-32 in no 来自Avalon总线模块的地址线。 read in no 从端口的读请求信号。当从端口不输出数据时不 需要该信号。若使用了该信号,readdata信号也 必须使用。 readdata 1-32 out no 读传输中输出到Avalon总线模块的数据线。当从 端口不输出数据时不需要该信号。若使用了该信 号,read信号也必须使用

变化。此外,如果异步外设的输出直接连接到 Avalon 总线模块,用户必须保证输出信号在 时钟上升沿之前达到稳定。 Avalon 总线规范并不定义在时钟上升沿之间信号如何变化。信号的变化由 Avalon 总线 时钟触发,信号只要在捕获时钟上升沿之前达到稳定就可以了。因此总线规范中的 Avalon 总线时序图中不会描绘精确的时间信息。在时钟上升沿之间信号是可变的,它取决于用于实 现系统的 Altera PLD 器件的特性。类似地,Avalon 总线没有规定固有的最高性能。系统模 块在特定的器件上综合布线之后,用户必须对系统模块进行标准的时序分析,以确定 Avalon 总线传输能达到的最高速度。 (3)Avalon 总线信号 由于 Avalon 总线是一个由 HD 连接 Avalon 总线模块和 Avalon 设时需要一些特别的考虑。对于传统的片外总线结构,所有外设都共享一组固定的、预先 设计 线 。一个信号也可以是用户自定义的。在这种情况下,SOPC Buil 定义用于写传输(输出方向)的信号,而不需定义用于读传输的信号。尽管中断请求(IRQ) 输出是从端口允许的信号类型 线规范不规定 外 的命名规则。不同信 的作用是预先定义 而信号的名称是则由外设决定。信号可以按照它的信号类型来命名, 的命名规范采用不同的名称。下面的章节中讨 号,例如 readdata 信号和 irq 信号。在这里将信号类型的名称作为信号名称,但外设信号的 称可以与此不 。 个例子, 2-2 列举了部分 alon 设的角度定义的。例如时钟信号 clk(方向为 in n 来说是输出 。 2-2 lo 信号类型 宽度 方向 必需 L 文件综合而来,所以在 外 的金属 路,而 Avalon 总线与此不同:SOPC Builder 必须准确地了解每个外设提供了 哪些 Avalon 端口,以便连接外设与 Avalon 总线模块。它还需要了解每个端口的名称和类型, 这些信息定义在系统 PTF 文件中。 Avalon 总线规范不要求 Avalon 外设必须包含哪些信号。它只定义了外设可以包含的各 种信号类型(例如地址、数据、时钟等)。外设的每一个信号都要指定一个有效的 Avalon 信 号类型,以确定该信号的作用 der 不将该端口与 Avalon 总线模块连接。Avalon 信号类型首先分为主端口信号和从端口 信号两类。因而,外设使用的信号类型首先由端口的主/从角色来决定。每个单独的主端口 或从端口使用的信号类型由外设的设计决定。例如,设计一个只有输出的 PIO 从外设只需 ,但也不是必须使用。 Avalon 总 Avalon 设信号 号类型 的, 也可以遵照系统级 论 Avalon 总线传输时会涉及到一些 Avalon 信 实际名 同 作为一 表 Av 从端口可用的信号类型。信号的方向是从外 )对于从外设来说是输入信号,而对于 Avalo 总线模块 信号 表 Ava n 从端口信号 说明 clk 1 in no 系统 有总 。只有异步从端口才能省 略 c 模块和 Avalon 总线模块的全局时钟信号。所 线传输都同步于 clk lk。 address 1-32 in no 来自 Avalon 总线模块的地址线。 read 1 in no 从端 需要 必须使用。 口的读请求信号。当从端口不输出数据时不 该信号。若使用了该信号,readdata 信号也 readdata 1-32 out no 读传 端口 要该信号。若使用了该信 号, 输中输出到 Avalon 总线模块的数据线。当从 不输出数据时不需 read 信号也必须使用

write in no 从端口的写请求信号。当从端口不接收数据时不 需要该信号。若使用了该信号,writedata信号也 必须使用。 writedata 1-32 in no 写传输中来自Avalon总线模块的数据线。当从端 口不接收数据时不需要该信号。若使用了该信号, write信号也必须使用。 irq out no 中断请求。当从外设需要主外设服务时可触发 irgo 表2-2中列举的信号类型都是高电平有效。Avalon总线还提供了各个信号类型的反向形 式。在PT℉声明中,在信号类型名称后面添加””,便可将对应的端口声明为低电平有效。 这对许多使用低电平有效逻辑的片外外设非常有用。 不论外设实现在系统模块的内部还是外部,Avalon总线信号及操作都是相同的。在内 部实现的情况下,SOPC Builder自动将外设的主端口或从端口连接到Avalon总线模块。在 外部实现的情况下,用户必须手工地将主端口或从端口连接到系统模块。在任何情况下, Avalon总线信号的行为都是相同的。 (4)并发多主端口的Avalon总线需考虑的问题 Avalon总线允许多个主端口连接到Avalon总线模块。而且实现Avalon总线的并发多主 端口功能时,Avalon总线模块不需要额外的特殊信号。当多个主外设试图同时访问同一个 从外设时,Avalon总线模块内部的从端口仲裁逻辑会被用来解决冲突。仲裁机制对于Avalon 总线外设是完全透明的。因而,不论是否使用了仲裁,应用于主端口和从端口的Avalon总 线传输协议是相同的。 换句话说,从端口不会意识到有多个主外设同时请求总线传输。类似地,被仲裁逻辑强 制等待的主外设也不会意识到另一个获胜的主外设的存在。主端口只是简单地发现它的等待 请求信号被置为有效,并一直等待,直到目标从外设准备好处理总线传输。将仲裁的细节隐 藏在Avalon总线模块内部极大地简化了外设的设计,任何Avalon外设在单主端口和多主端 口结构中都可以使用。 2.3.3 Avalon三态接口 Avalon三态接口用于将片外设备通过PLD的I/O引脚直接连接到Avalon总线模块上。 PTF参数Bus_Type=“avalon_tristate”用来指定一个片外的外设使用了Avalon三态接口。大 多数系统都需要一个接口来连接某种形式的片外存储器设备。片外存储器设备经常在物理的 印刷电路板(PCB)上共享地址和数据总线线路。这需要一个包含三态的双向数据引脚的接 口,使得其他的外设也能够驱动数据线而不会引起信号的竞争。Avalon三态接口描述了一 个适当的接口用来通过设备的/O引脚连接简单的片外从设备,例如闪存、SRAM以及同步 SRAM(SSRAM)。某些Avalon传输模式不支持片外设备

write 1 in no 从端 需要该信号。若使用了该信号,writedata 信号也 必须 口的写请求信号。当从端口不接收数据时不 使用。 writedata 1-32 in no 写传 口不接收数据时不需要该信号。若使用了该信号, wri 输中来自 Avalon 总线模块的数据线。当从端 te 信号也必须使用。 irq 1 out no 中断 设需要主外设服务时可触发 irq。 请求。当从外 2-2 中列举的信号类型都是高电平有效。Avalon 总线还提供了各个信号类型的反向形 式。 非常有用。 相同的。 求总线传输。类似地,被仲裁逻辑强 制等 lon 总线模块内部极大地简化了外设的设计,任何 Avalon 外设在单主端口和多主端 口结 Avalon 三态接口用于将片外设备通过 PLD 的 I/O 引脚直接连接到 Avalon 总线模块上。 “avalon_tristate”用来指定一个片外的外设使用了 Avalon 三态接口。大 数系统都需要一个接口来连接某种形式的片外存储器设备。片外存储器设备经常在物理的 印刷 模式不支持片外设备。 表 在 PTF 声明中,在信号类型名称后面添加”_n”,便可将对应的端口声明为低电平有效。 这对许多使用低电平有效逻辑的片外外设 不论外设实现在系统模块的内部还是外部,Avalon 总线信号及操作都是相同的。在内 部实现的情况下,SOPC Builder 自动将外设的主端口或从端口连接到 Avalon 总线模块。在 外部实现的情况下,用户必须手工地将主端口或从端口连接到系统模块。在任何情况下, Avalon 总线信号的行为都是 (4)并发多主端口的 Avalon 总线需考虑的问题 Avalon 总线允许多个主端口连接到 Avalon 总线模块。而且实现 Avalon 总线的并发多主 端口功能时,Avalon 总线模块不需要额外的特殊信号。当多个主外设试图同时访问同一个 从外设时,Avalon 总线模块内部的从端口仲裁逻辑会被用来解决冲突。仲裁机制对于 Avalon 总线外设是完全透明的。因而,不论是否使用了仲裁,应用于主端口和从端口的 Avalon 总 线传输协议是相同的。 换句话说,从端口不会意识到有多个主外设同时请 待的主外设也不会意识到另一个获胜的主外设的存在。主端口只是简单地发现它的等待 请求信号被置为有效,并一直等待,直到目标从外设准备好处理总线传输。将仲裁的细节隐 藏在 Ava 构中都可以使用。 2.3.3 Avalon 三态接口 PTF 参数 Bus_Type = 多 电路板(PCB)上共享地址和数据总线线路。这需要一个包含三态的双向数据引脚的接 口,使得其他的外设也能够驱动数据线而不会引起信号的竞争。Avalon 三态接口描述了一 个适当的接口用来通过设备的 I/O 引脚连接简单的片外从设备,例如闪存、SRAM 以及同步 SRAM(SSRAM)。某些 Avalon 传输

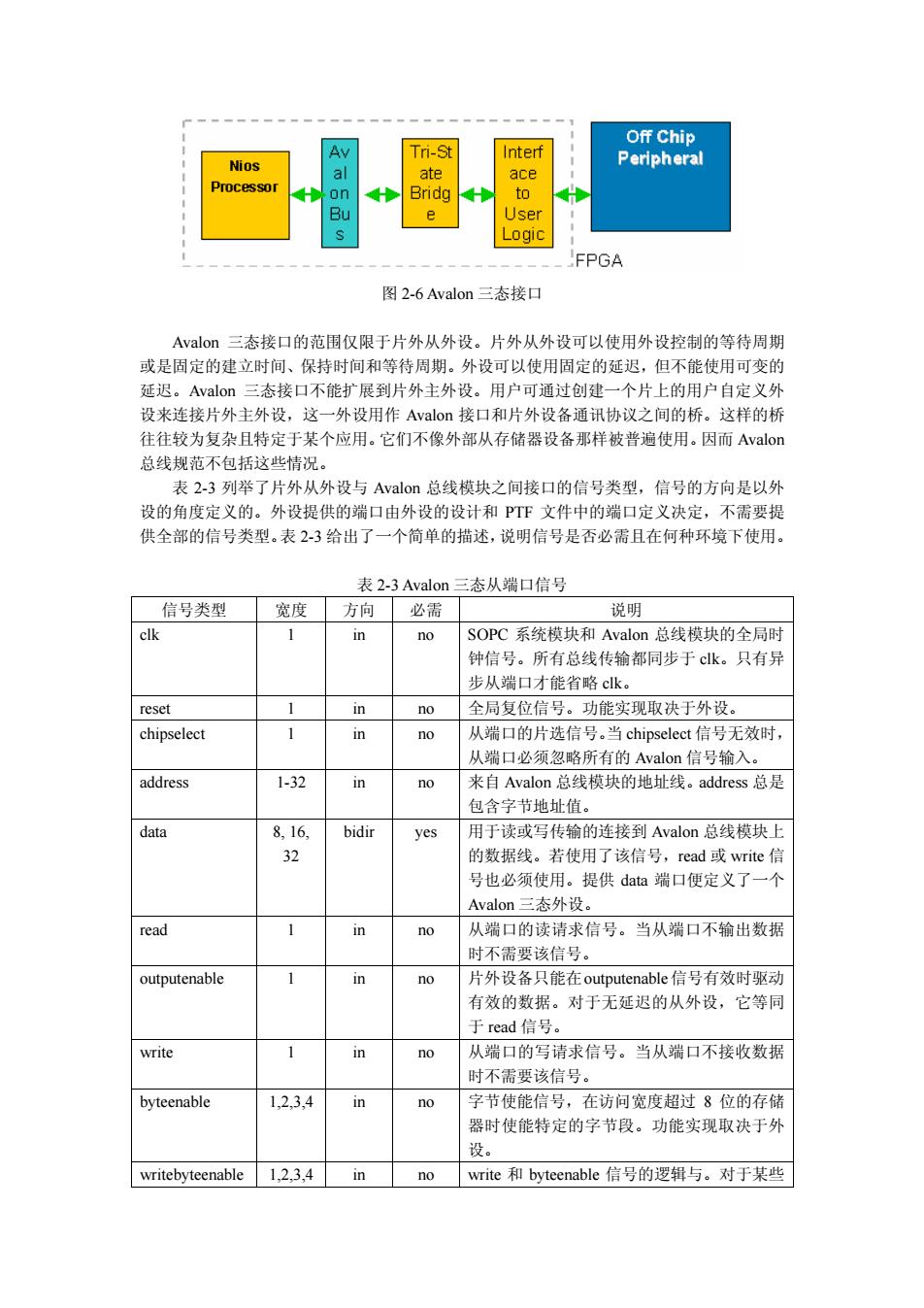

Off Chip Tri-St Interf Nios Peripheral al ate ace Processor on Bridg to Bu e User Logic FPGA 图2-6 Avalon三态接口 Avalon三态接口的范围仅限于片外从外设。片外从外设可以使用外设控制的等待周期 或是固定的建立时间、保持时间和等待周期。外设可以使用固定的延迟,但不能使用可变的 延迟。Avalon三态接口不能扩展到片外主外设。用户可通过创建一个片上的用户自定义外 设来连接片外主外设,这一外设用作Avalon接口和片外设备通讯协议之间的桥。这样的桥 往往较为复杂且特定于某个应用。它们不像外部从存储器设备那样被普遍使用。因而Avalon 总线规范不包括这些情况。 表2-3列举了片外从外设与Avalon总线模块之间接口的信号类型,信号的方向是以外 设的角度定义的。外设提供的端口由外设的设计和PT℉文件中的端口定义决定,不需要提 供全部的信号类型。表2-3给出了一个简单的描述,说明信号是否必需且在何种环境下使用。 表2-3 Avalon三态从端口信号 信号类型 宽度 方向 必需 说明 clk in no SOPC系统模块和Avalon总线模块的全局时 钟信号。所有总线传输都同步于ck。只有异 步从端口才能省略ck。 reset in no 全局复位信号。功能实现取决于外设。 chipselect 1 no 从端口的片选信号。当chipselect信号无效时, 从端口必须忽略所有的Avalon信号输入。 address 1-32 n no 来自Avalon总线模块的地址线。address总是 包含字节地址值。 data 8,16, bidir yes 用于读或写传输的连接到Avalon总线模块上 32 的数据线。若使用了该信号,read或write信 号也必须使用。提供data端口便定义了一个 Avalon三态外设。 read in no 从端口的读请求信号。当从端口不输出数据 时不需要该信号。 outputenable in no 片外设备只能在outputenable信号有效时驱动 有效的数据。对于无延迟的从外设,它等同 于read信号。 write in no 从端口的写请求信号。当从端口不接收数据 时不需要该信号。 byteenable 1,2,3,4 no 字节使能信号,在访问宽度超过8位的存储 器时使能特定的字节段。功能实现取决于外 设。 writebyteenable 1,2,3,4 n no write和byteenable信号的逻辑与。对于某些

图 2-6 Avalon 三态接口 Avalon 三态接口的范围仅限于片外从外设。片外从外设可以使用外设控制的等待周期 或是 可变的 延迟 这些情况。 使用。 信号类型 宽度 方向 必需 说明 固定的建立时间、保持时间和等待周期。外设可以使用固定的延迟,但不能使用 。Avalon 三态接口不能扩展到片外主外设。用户可通过创建一个片上的用户自定义外 设来连接片外主外设,这一外设用作 Avalon 接口和片外设备通讯协议之间的桥。这样的桥 往往较为复杂且特定于某个应用。它们不像外部从存储器设备那样被普遍使用。因而 Avalon 总线规范不包括 表 2-3 列举了片外从外设与 Avalon 总线模块之间接口的信号类型,信号的方向是以外 设的角度定义的。外设提供的端口由外设的设计和 PTF 文件中的端口定义决定,不需要提 供全部的信号类型。表 2-3 给出了一个简单的描述,说明信号是否必需且在何种环境下 表 2-3 Avalon 三态从端口信号 clk 1 in no SOPC 系统模块和 Avalon 总线模块的全局时 钟信号。所有总线传输都同步于 clk。只有异 步从端口才能省略 clk。 reset 1 in no 全局复位信号。功能实现取决于外设。 chipselect 1 in no 从端口的片选信号。当 chipselect 信号无效时, 从端口必须忽略所有的 Avalon 信号输入。 address 1-32 in no 来自 Avalon 总线模块的地址线。address 总是 包含字节地址值。 data 8, 16, bidir 写传输的连接到 Avalon 总线模块上 data 端口便定义了一个 alon 三态外设。 yes 用于读或 32 的数据线。若使用了该信号,read 或 write 信 号也必须使用。提供 Av read 1 当从端口不输出数据 时不需要 in no 从端口的读请求信号。 该信号。 outputenable 1 no 片外设备只能 le信号有效时驱动 有效的数据 从外设,它等同 于 read 信号 in 在outputenab 。对于无延迟的 。 write 1 no 从端口的写 端口不接收数据 时不需要该信 in 请求信号。当从 号。 byteenable 1,2,3,4 in no 字节使能信号,在访问宽度超过 8 位的存储 器时使能特定的字节段。功能实现取决于外 设。 writebyteenable 1,2,3,4 in no write 和 byteenable 信号的逻辑与。对于某些

特定类型的存储外设,特别是片外SSRAM是 有用的控制信号。 irq out no 中断请求。当从外设需要主外设服务时可触 发irqo begintransfer out no 在每个新的Avalon总线传输的第一个总线周 期期间有效。用途取决于外设。 同非三态的Avalon接口一样,所有的信号类型在添加了“n”之后便成为低电平有效 的形式,例如chipselect n和write n。 Avalon三态接口使用双向端口data代替分离的readdata和writedata端口。在写传输期 间,Avalon总线模块驱动data端口,从设备捕获data。在读传输期间,从设备驱动data端 口,Avalon总线模块捕获data。data端口是双向的,从外设和Avalon总线模块只能在特定 的时间驱动data信号线。 Avalon三态接口引入了共享端口的概念。共享端口在将Avalon总线连接到外部设备时 能够减少所需的外部引脚数量。PTF参数Is Shared用于声明一个端口是共享的。一个特定 类型的共享端口可以连接到多个片外从设备,并由它们共享。数据端口总是共享的。例如, 当Avalon总线模块的data端口连接到PLD的I/O引脚时,这些data引脚可以连接到多个片 外外设。其他端口例如address、read和write根据需要也可以共享。如果一个或多个其他外 设使用了一个同样类型的端口,并且这些外设的端口也都声明为共享,那么SOPC Builder 就会将这些共享端口复用到相同的设备I/O引脚上。Avalon三态从外设只能根据chipselect 和outputenable的定义,在特定时间响应共享信号。 使用Avalon三态接口的外设必须使用chipselect端口.片外从外设只能在它的chipselect 信号有效时接受传输。chipselect不会是共享信号,每个片外外设都由独立的chipselect信号 驱动。 Avalon三态接口为从端口读传输引入了outputenable信号类型。为避免data线上的信号 竞争,片外从外设只能在outputenable有效时驱动它们的data输出引脚。outputenable主要 用于具有延迟的片外存储器设备,例如SSRAM在发起读传输后的几个时钟周期之后驱动 data信号线。 2.3.4地址对齐 Avalon总线模块能够适应主从外设的各种不同的和不匹配的数据宽度。例如,32位的 主端口可以访问8位的从端口,16位的主端口可以访问32位的从端口。当系统中存在数据 宽度不匹配的主从端口对时,便要考虑地址对齐的问题。这一情形并不特定于Avalon总线, 它对于所有微处理器系统都存在。 在讨论数据宽度不同的主从端口之间的数据传输时,必须分清哪个外设的数据端口较 宽。在较宽的主端口访问较窄的从端口时,问题变为:当较宽的主端口读(或写)较窄的从 端口时,如何处理最高有效位(MSBs)?Avalon总线为处理这一情形提供了两种方法: ·静态地址对齐(Native Address Alignment)一在静态地址对齐方式下,主端口的 单个传输精确地对应于从端口的一次传输。例如,当32位的主端口读取16位的从端口时, Avalon总线模块返回一个32位的数据,但只有最低的16个有效位包含了来自从端口的数 据,最高有效位可以是0或未定义。这是许多嵌入式系统中典型的“主设备处理一切”的情 形。然而,控制主端口的软硬件设计必须意识到所有相关外设的物理地址宽度和编址方案。 这增加了主外设的设计复杂性

特定类型的存储外设,特别是片外 SSRAM 是 有用的控制信号。 irq 1 out no 中断请求。当从外设需要主外设服务时可触 发 irq。 begi ransfer 1 out no 在每个新的 Avalon 总线传输的第一个总线周 于外设。 nt 期期间有效。用途取决 同非三态的 Avalo 有的信号类型在添加 成为低电平有效 的形式,例如 chipselec Aval ata 代替分离的 readdata 和 writedata 端口。在写传输期 间, valon 总线模块驱动 data 端口,从设备捕获 data。在读传输期间,从设备驱动 data 端 口, 共享端口可以连接到多个片外从设备,并由它们共享。数据端口总是共享的。例如, 当 A lon 总线模块的 data 端口连接到 PLD 的 I/O 引脚时,这些 data 引脚可以连接到多个片 address、read 和 write 根据需要也可以共享。如果一个或多个其他外 使用了一个同样类型的端口,并且这些外设的端口也都声明为共享,那么 SOPC Builder 就会 为避免 data 线上的信号 竞争 ta 输出引脚。outputenable 主要 用于 输后的几个时钟周期之后驱动 data 2.3. 从外设的各种不同的和不匹配的数据宽度。例如,32 位的 主端 的主端口可以访问 32 位的从端口。当系统中存在数据 宽度不匹配的主从端口对时,便要考虑地址对齐的问题。这一情形并不特定于 Avalon 总线, 它对 的主从端口之间的数据传输时,必须分清哪个外设的数据端口较 宽。 口访问较窄的从端口时,问题变为:当较宽的主端口读(或写)较窄的从 端口时,如何处理最高有效位(MSBs)? Avalon 总线为处理这一情形提供了两种方法: nment)——在静态地址对齐方式下,主端口的 单个传输精确地对应于从端口的一次传输。例如,当 32 位的主端口读取 16 位的从端口时, Aval 32 位的数据,但只有最低的 16 个有效位包含了来自从端口的数 据, 高有效位可以是 0 或未定义。这是许多嵌入式系统中典型的“主设备处理一切”的情 须意识到所有相关外设的物理地址宽度和编址方案。 这增加了主外设的设计复杂性。 n 接口一样,所 了“_n”之后便 t_n 和 write_n。 on 三态接口使用双向端口 d A Avalon 总线模块捕获 data。data 端口是双向的,从外设和 Avalon 总线模块只能在特定 的时间驱动 data 信号线。 Avalon 三态接口引入了共享端口的概念。共享端口在将 Avalon 总线连接到外部设备时 能够减少所需的外部引脚数量。PTF 参数 Is_Shared 用于声明一个端口是共享的。一个特定 类型的 va 外外设。其他端口例如 设 将这些共享端口复用到相同的设备 I/O 引脚上。Avalon 三态从外设只能根据 chipselect 和 outputenable 的定义,在特定时间响应共享信号。 使用 Avalon 三态接口的外设必须使用 chipselect 端口。片外从外设只能在它的 chipselect 信号有效时接受传输。chipselect 不会是共享信号,每个片外外设都由独立的 chipselect 信号 驱动。 Avalon 三态接口为从端口读传输引入了 outputenable 信号类型。 ,片外从外设只能在 outputenable 有效时驱动它们的 da 具有延迟的片外存储器设备,例如 SSRAM 在发起读传 信号线。 4 地址对齐 Avalon 总线模块能够适应主 口可以访问 8 位的从端口,16 位 于所有微处理器系统都存在。 在讨论数据宽度不同 在较宽的主端 · 静态地址对齐(Native Address Alig on 总线模块返回一个 最 形。然而,控制主端口的软硬件设计必

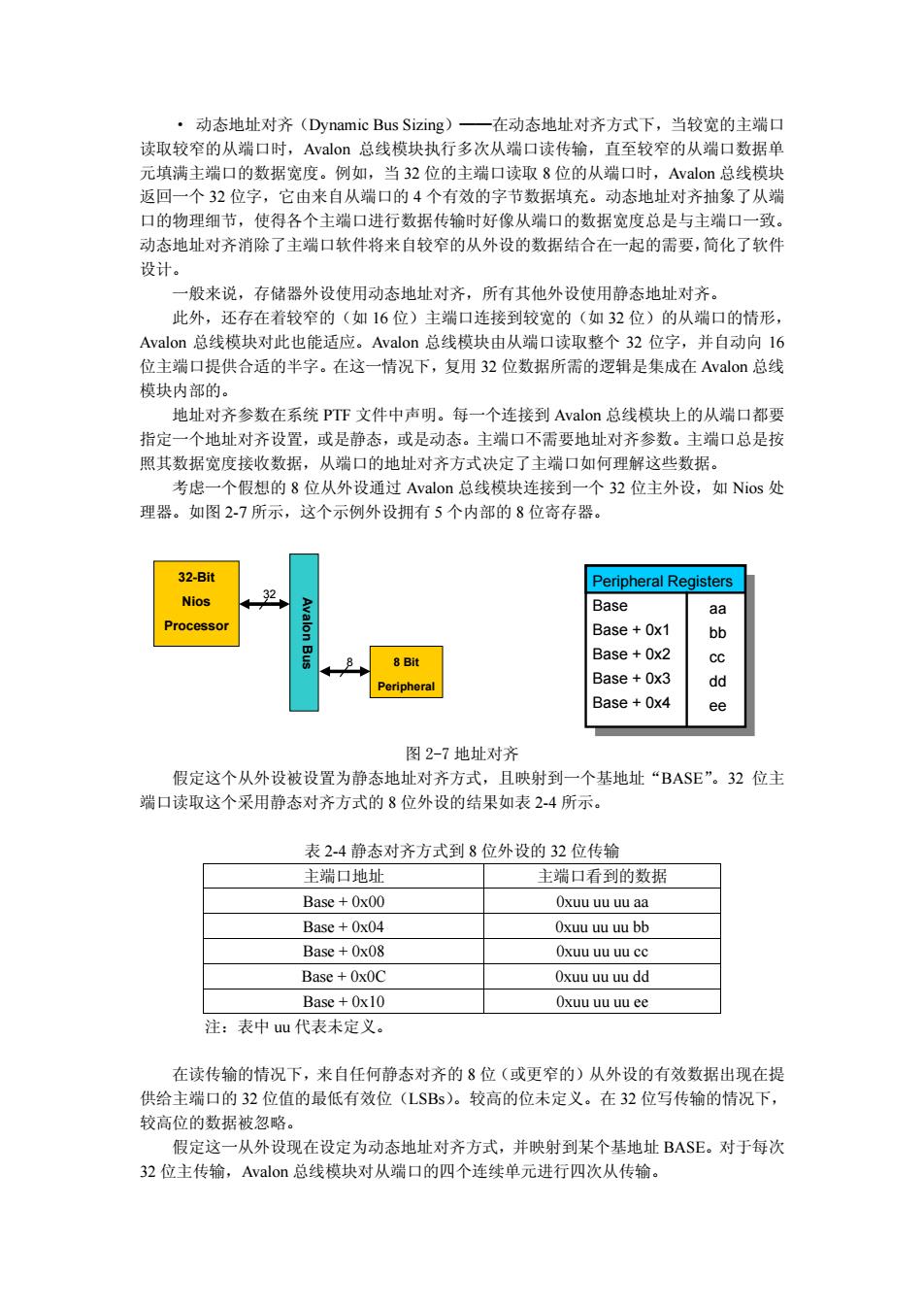

·动态地址对齐(Dynamic Bus Sizing)一在动态地址对齐方式下,当较宽的主端口 读取较窄的从端口时,Avalon总线模块执行多次从端口读传输,直至较窄的从端口数据单 元填满主端口的数据宽度。例如,当32位的主端口读取8位的从端口时,Avalon总线模块 返回一个32位字,它由来自从端口的4个有效的字节数据填充。动态地址对齐抽象了从端 口的物理细节,使得各个主端口进行数据传输时好像从端口的数据宽度总是与主端口一致。 动态地址对齐消除了主端口软件将来自较窄的从外设的数据结合在一起的需要,简化了软件 设计。 一般来说,存储器外设使用动态地址对齐,所有其他外设使用静态地址对齐。 此外,还存在着较窄的(如16位)主端口连接到较宽的(如32位)的从端口的情形, Avalon总线模块对此也能适应。Avalon总线模块由从端口读取整个32位字,并自动向l6 位主端口提供合适的半字。在这一情况下,复用32位数据所需的逻辑是集成在Avalon总线 模块内部的。 地址对齐参数在系统PTF文件中声明。每一个连接到Avalon总线模块上的从端口都要 指定一个地址对齐设置,或是静态,或是动态。主端口不需要地址对齐参数。主端口总是按 照其数据宽度接收数据,从端口的地址对齐方式决定了主端口如何理解这些数据。 考虑一个假想的8位从外设通过Avalon总线模块连接到一个32位主外设,如Nios处 理器。如图2-7所示,这个示例外设拥有5个内部的8位寄存器。 32-Bit Peripheral Registers Nios 32 Ava Base aa Processor Base +0x1 bb 8 Bit Base +0x2 cc Base +0x3 Peripheral dd Base +0x4 ee 图2-7地址对齐 假定这个从外设被设置为静态地址对齐方式,且映射到一个基地址“BASE”。32位主 端口读取这个采用静态对齐方式的8位外设的结果如表2-4所示。 表2-4静态对齐方式到8位外设的32位传输 主端口地址 主端口看到的数据 Base +0x00 Oxuu uu uu aa Base +0x04 Oxuu uuuu bb Base+0x08 Oxuu uu uu cc Base +0x0C Oxuu uuuu dd Base +0x10 Oxuu uuuu ee 注:表中uu代表未定义。 在读传输的情况下,来自任何静态对齐的8位(或更窄的)从外设的有效数据出现在提 供给主端口的32位值的最低有效位(LSBs)。较高的位未定义。在32位写传输的情况下, 较高位的数据被忽略。 假定这一从外设现在设定为动态地址对齐方式,并映射到某个基地址BASE。对于每次 32位主传输,Avalor总线模块对从端口的四个连续单元进行四次从传输

· 动态地址对齐(Dynamic Bus Sizing)——在动态地址对齐方式下,当较宽的主端口 读取较窄的从端口时,Avalon 总线模块执行多次从端口读传输,直至较窄的从端口数据单 元填满主端口的数据宽度。例如,当 32 位的主端口读取 8 位的从端口时,Avalon 总线模块 返回一个 32 位字,它由来自从端口的 4 个有效的字节数据填充。动态地址对齐抽象了从端 口的物理细节,使得各个主端口进行数据传输时好像从端口的数据宽度总是与主端口一致。 了主端口软件将来自较窄的从外设的数据结合在一起的需要,简化了软件 设计 (如 16 位)主端口连接到较宽的(如 32 位)的从端口的情形, Aval 对齐设置,或是静态,或是动态。主端口不需要地址对齐参数。主端口总是按 照其 所示,这个示例外设拥有 5 个内部的 8 位寄存器。 所示。 表 2-4 静态对齐方式到 8 位外设的 32 位传输 动态地址对齐消除 。 一般来说,存储器外设使用动态地址对齐,所有其他外设使用静态地址对齐。 此外,还存在着较窄的 on 总线模块对此也能适应。Avalon 总线模块由从端口读取整个 32 位字,并自动向 16 位主端口提供合适的半字。在这一情况下,复用 32 位数据所需的逻辑是集成在 Avalon 总线 模块内部的。 地址对齐参数在系统 PTF 文件中声明。每一个连接到 Avalon 总线模块上的从端口都要 指定一个地址 数据宽度接收数据,从端口的地址对齐方式决定了主端口如何理解这些数据。 考虑一个假想的 8 位从外设通过 Avalon 总线模块连接到一个 32 位主外设,如 Nios 处 理器。如图 2-7 32-Bit Nios Processor 8 Bit Peripheral Avalon Bus 32 8 Peripheral Registers Base Base + 0x1 Base + 0x2 aa bb cc Base + 0x3 dd Base + 0x4 ee 图 2-7 地址对齐 假定这个从外设被设置为静态地址对齐方式,且映射到一个基地址“BASE”。32 位主 端口读取这个采用静态对齐方式的 8 位外设的结果如表 2-4 主端口地址 主端口看到的数据 Base + 0x00 0xuu uu uu aa Base + 0x04 0xuu uu uu bb Base + 0x08 0xuu uu uu cc Base + 0x0C 0xuu uu uu dd Base + 0x10 0xuu uu uu ee 况下, 较高位的数据被忽略。 现在设定为动态地址对齐方式,并映射到某个基地址 BASE。对于每次 32 位 注:表中 uu 代表未定义。 在读传输的情况下,来自任何静态对齐的 8 位(或更窄的)从外设的有效数据出现在提 供给主端口的 32 位值的最低有效位(LSBs)。较高的位未定义。在 32 位写传输的情 假定这一从外设 主传输,Avalon 总线模块对从端口的四个连续单元进行四次从传输