2.根据分析结果,选择片外外设或片内P(知识产权核)。除此以外,还要对选择的 P和外设进行初步性能评估,以保证能够满足系统需求。 3. 确定P和系统参数。 4.确定系统互联逻辑,分配FPGA的引脚等。 5.结合Nos提供的软件开发包进行软件开发等。 完整的S0PC系统开发流程可如图1-6所示,其中的详细内容会在后续章节中进行介绍。 SOPC Builder GUI Processor Library Configure Processor Custom Instructions Peripheral Library Select Configure IP Modules Peripherals,IP Hardware Development Software Development Connect Blocks C Header files HDL Source Files ·Custom Library 。Testhench Generate Peripheral Drivers Hardware Executable Connguration Code Synthesis Fle用 Compller, Fitter Verification Linker,Debugger &Debug t ■User Design Serial,c时 Ethernet User Code ■Other IP Blocks On-chi Libraries Aitera Debug .RTOS Quartus ll PLD GNUPro Tools 图1-6SOP℃系统开发流程 1.3S0P℃系统开发环境 Altera QuartusⅡ3.0是一个综合设计环境,被称为SOPC(可编程芯片系统)的升级 环境,它承接了原来Max plusⅡ的全部设计功能和器件对象外还增加了许多新功能和新的 FPGA器件系列,包括一些适用于SOPC开发的大规模器件。 相对于其它EDA工具,QuartusⅡ含有许多更具特色和更强的实用功能。 (1)QuartusⅡ与SOPC Builder结合用于开发Nios嵌入式系统。 目前最为常用的嵌入式系统大多采用了含有AM的32位知识产权处理器核的器件。尽 管由这些器件构成的嵌入式系统有很强的功能,但为了使系统更为完备、功能更为强大、对 更多任务的完成具有更好的适应性,通常必须为此处理器配置许多接口器件,方能构成一个 完整的应用系统,如除配置常规的SRAM、DRAM、Flash外,还必须配置网络通信接口、串行 通信接口USB接口、VGA接口、PS/2接口等等。这样势必会增加整个系统的体积、功耗,降 低了系统的可靠性。但是如果将ARM或其它知识产权核以硬核方式植入FPGA中,利用FPGA 中的可编程逻辑资源和IP软核来构成该嵌入式系统处理器的接口功能模块,就能很好地解

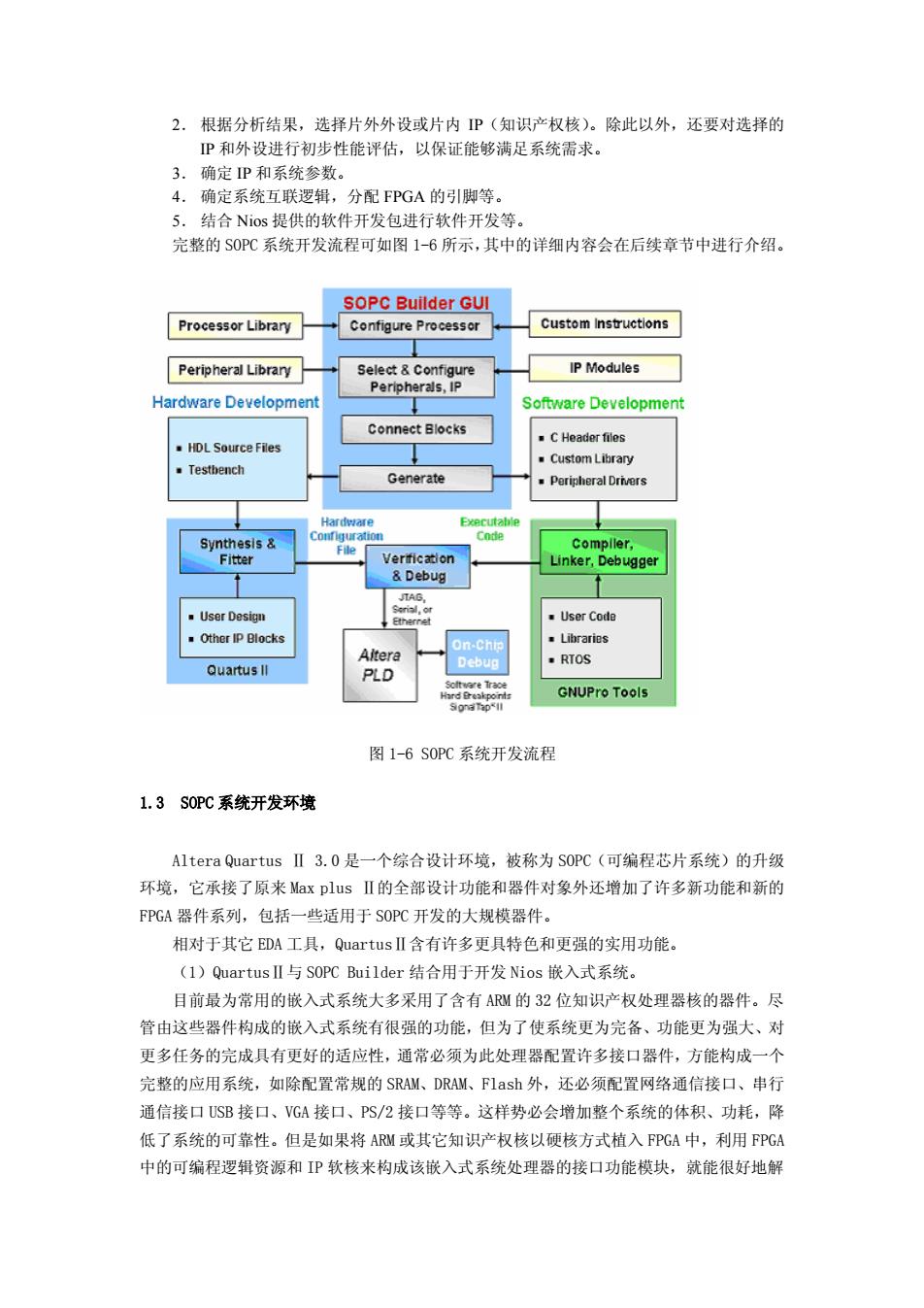

2. 根据分析结果,选择片外外设或片内 IP(知识产权核)。除此以外,还要对选择的 . 确定 和系统参数。 IP 和外设进行初步性能评估,以保证能够满足系统需求。 3 IP 4. 确定系统互联逻辑,分配 FPGA 的引脚等。 5. 结合 Nios 提供的软件开发包进行软件开发等。 完整的 SOPC 系统开发流程可如图 1-6 所示,其中的详细内容会在后续章节中进行介绍。 图 1-6 SOPC 系统开发流程 1.3 SOPC 系统开发环境 Altera Quartus Ⅱ 3.0 是一个综合设计环境,被称为 SOPC(可编程芯片系统)的升级 环境,它承接了原来 Max plus Ⅱ的全部设计功能和器件对象外还增加了许多新功能和新的 FPGA 器件系列,包括一些适用于 SOPC 开发的大规模器件。 相对于其它 EDA 工具,QuartusⅡ含有许多更具特色和更强的实用功能。 (1)QuartusⅡ与 SOPC Builder 结合用于开发 Nios 嵌入式系统。 目前最为常用的嵌入式系统大多采用了含有 ARM 的 32 位知识产权处理器核的器件。尽 管由这些器件构成的嵌入式系统有很强的功能,但为了使系统更为完备、功能更为强大、对 更多任务的完成具有更好的适应性,通常必须为此处理器配置许多接口器件,方能构成一个 完整的应用系统,如除配置常规的 SRAM、DRAM、Flash 外,还必须配置网络通信接口、串行 通信接口 USB 接口、VGA 接口、PS/2 接口等等。这样势必会增加整个系统的体积、功耗,降 低了系统的可靠性。但是如果将 ARM 或其它知识产权核以硬核方式植入 FPGA 中,利用 FPGA 中的可编程逻辑资源和 IP 软核来构成该嵌入式系统处理器的接口功能模块,就能很好地解

决这些问题。对此,Altera和Xilinx公司都相继推出了这方面的器件。例如,Altera的 Excalibur系列FPGA中就植入了ARM922T嵌入式系统处理器:Xilinx的Virtex-ⅡPro系列 中植入了IBM PowerPC4O5处理器。这样就能使得FPGA的强大的软件功能有机地相结合,高 效地实现S0C系统。 但是,这种将IP硬核植入FPGA的解决方案存在5种不够完美之处: ·由于此类硬核多来自第三方公司,PGA厂商通常无法直接控制其知识产权费用,从 而导致FPGA器件价格相对较高: ·由于硬核是预先植入的,设计者无法根据实际需要改变处理器的结构,如总线规模、 接口方式,乃至指令形式,更不可能将FPGA逻辑资源构成的硬件模块以指令的形式形成内 置嵌入式系统的硬件加速模块(如DSP模块),以适应更多的电路功能要求: ·无法根据实际设计需求在同一FPGA中使用指定数量的处理器核: ·无法裁减处理器硬件资源以降低FPGA成本: ·只能在特定的FPGA中使用硬核嵌入式系统,如只能使用Excalibur系列FPGA中的 ARM核,Virtex-IⅡPro系列中的PowerPC核。 但是如果利用软核嵌入式系统处理器就能有效地解决上述不利因素。它们分别是 Altera的Nios核与Xilinx的Micro Blaze.。特别是前者,使上述5方面的问题得到全面的 解决。 A1tera的Nios核是用户可随意配置和构建的32位/16位总线(用户可选的)指令集和 数据通道的嵌入式系统微处理器IP核,采用Avalon总线结构通信接口,带有增强的内存、 调试和软件功能(C或汇偏程序程序优化开发功能);含由First Silicon Solutions(FS2) 开发的基于JTAG的片内设备(OCI)内核(这为开发者提供了强大的软硬件调试实时代码, OCI调试功能可根据FPGA JTAG端口上接受的指令,直接监视和控制片内处理器的工作情 况)。此外,基于QuartusⅡ平台的用户可编辑的Nios核含有许多可配置的接口模块核, 包括:可配置高速缓存(包括由片内ESB或外部SRAM或SDRAM,1OOM以上单周期访问速度) 模块,可配置RS232通信口、SDRAM控制器、标准以太网协议接口、DMA、定时器、协处理 器等等。在植入(配置进)FPGA前,用户可根据设计要求,利用QuartusⅡ和SOPC Builder, 对Ni0s及其外围系统进行构建,使该嵌入式系统在硬件结构、功能特点、资源占有等方面 全面满足用户系统设计的要求。Nios核在同一FPGA中被植入的数量没有限制,只要FPGA 的资源允许,此外Nios可植入的Altera FPGA的系列几乎没有限制,在这方面,Nios显然 优于Xilinx的Micro Blaze.。另外,在开发工具的完备性方面、对常用的嵌入式操作系统 支持方面,Nios都优于Micro Blaze。就成本而言,由于Nios是由Altera直接推出而非第 三方产品,故用户通常无需支付知识产权费用,NiOs的使用费仅仅是其占用的FPGA的逻辑 资源费。因此,选用的FPGA越便宜,则Nios的使用费就越便宜。 (2)QuartusⅡ含有实时调试工具、嵌入式逻辑分析仪Signal TapⅡ。 随着逻辑设计复杂性的不断增加,在计算机上以软件方式的仿真测试变得更加耗费时 间,而不断需要重复进行的硬件系统的测试同样变得更为困难。为了解决这些问题,设计者 可以将一种高效的硬件实时测试手段和传统的系统测试方法相结合来完成。这就是嵌入式逻 辑分析仪Signal TapⅡ的使用。它可以随设计文件一并下载于目标芯片中,用以捕捉目标

决这些问题。对此,Altera 和 Xilinx 公司都相继推出了这方面的器件。例如,Altera 的 Excalibur 系列 FPGA 中就植入了 ARM922T 嵌入式系统处理器;Xilinx 的 Virtex-ⅡPro 系列 中植入了 IBM PowerPC405 处理器。这样就能使得 FPGA 的强大的软件功能有机地相结合,高 效地实现 SOC 系统。 但是,这种将 IP 硬核植入 FPGA 的解决方案存在 5 种不够完美之处: ·由于此类硬核多来自第三方公司,FPGA 厂商通常无法直接控制其知识产权费用,从 而导致 FPGA 器件价格相对较高; ·由于硬核是预先植入的,设计者无法根据实际需要改变处理器的结构,如总线规模、 接口方式,乃至指令形式,更不可能将 FPGA 逻辑资源构成的硬件模块以指令的形式形成内 置嵌入式系统的硬件加速模块(如 DSP 模块),以适应更多的电路功能要求; ·无法根据实际设计需求在同一 FPGA 中使用指定数量的处理器核; ·无法裁减处理器硬件资源以降低 FPGA 成本; ·只能在特定的 FPGA 中使用硬核嵌入式系统,如只能使用 Excalibur 系列 FPGA 中的 ARM 核,Virtex-ⅡPro 系列中的 PowerPC 核。 但是如果利用软核嵌入式系统处理器就能有效地解决上述不利因素。它们分别是 Altera 的 Nios 核与 Xilinx 的 Micro Blaze。特别是前者,使上述 5 方面的问题得到全面的 解决。 Altera 的 Nios 核是用户可随意配置和构建的 32 位/16 位总线(用户可选的)指令集和 数据 功能);含由 First Silicon Solutions(FS2) 开发 ) 通道的嵌入式系统微处理器 IP 核,采用 Avalon 总线结构通信接口,带有增强的内存、 调试和软件功能(C 或汇偏程序程序优化开发 的基于 JTAG 的片内设备(OCI)内核(这为开发者提供了强大的软硬件调试实时代码, OCI 调试功能可根据 FPGA JTAG 端口上接受的指令,直接监视和控制片内处理器的工作情 况)。此外,基于 QuartusⅡ平台的用户可编辑的 Nios 核含有许多可配置的接口模块核, 包括:可配置高速缓存(包括由片内 ESB 或外部 SRAM 或 SDRAM,100M 以上单周期访问速度 模块,可配置 RS232 通信口、SDRAM 控制器、标准以太网协议接口、DMA、定时器、协处理 器等等。在植入(配置进)FPGA 前,用户可根据设计要求,利用 QuartusⅡ和 SOPC Builder, 对 Nios 及其外围系统进行构建,使该嵌入式系统在硬件结构、功能特点、资源占有等方面 全面满足用户系统设计的要求。Nios 核在同一 FPGA 中被植入的数量没有限制,只要 FPGA 的资源允许,此外 Nios 可植入的 Altera FPGA 的系列几乎没有限制,在这方面,Nios 显然 优于 Xilinx 的 Micro Blaze。另外,在开发工具的完备性方面、对常用的嵌入式操作系统 支持方面,Nios 都优于 Micro Blaze。就成本而言,由于 Nios 是由 Altera 直接推出而非第 三方产品,故用户通常无需支付知识产权费用,Nios 的使用费仅仅是其占用的 FPGA 的逻辑 资源费。因此,选用的 FPGA 越便宜,则 Nios 的使用费就越便宜。 (2) QuartusⅡ含有实时调试工具、嵌入式逻辑分析仪 Signal TapⅡ。 随着逻辑设计复杂性的不断增加,在计算机上以软件方式的仿真测试变得更加耗费时 间,而不断需要重复进行的硬件系统的测试同样变得更为困难。为了解决这些问题,设计者 可以将一种高效的硬件实时测试手段和传统的系统测试方法相结合来完成。这就是嵌入式逻 辑分析仪 Signal TapⅡ的使用。它可以随设计文件一并下载于目标芯片中,用以捕捉目标

芯片内设计者感兴趣的信号节点处的信号,而又不影响原硬件系统的正常工作。可以通过两 种方式来使用Signal TapⅡ,一种是直接使用Quartus IⅡ3.0中的Signal TapⅡ;另一种 方式是通过MATLAB的Simulink和DSP Builder来使用Signal TapⅡ。DSP Builder中包含 有Signal TapⅡ模块,设计者可以使用此模块设置用于信号探察的事件触发器,配置存储 器,并能显示波形。这可以使用Node模块来选择有待监测的信号。使用Signal TapⅡ后, 当触发器运行后,通常要占用部分内部RAM,因为在实际监测中,将测得的样本信号暂存于 目标器件中的嵌入式RAM(如ESB)中,然后通过器件的JTAG端口和Byte Blaster IⅡ下载 线将采得的信息传出,送于P℃机进行分析。P℃机中送达的数据是以文本文件的方式存储的, 并可在Simulink图上显示波形: (3)QuartusⅡ含有一种十分有效的逻辑设计优化技术,即设计模块在FPGA中指定区 域内的逻辑锁定功能,Logic Lock技术。 有FPGA开发经验的人都会有这样的体会,原来在硬件测试上十分成功的FPGA设计,结 果在源代码并没有任何改变的情况下,仅仅是增加了一点与原程序毫不相干的电路描述,或 甚至只改变了某个端口信号的引脚锁定位置,结果在综合适配后,原设计的硬件性能大为下 降,如速度降低了,有时甚至无法正常工作。这时,如果比较改变设计前后的Floorplan 图,会发现芯片内部资源的使用情况发生了巨大的变化。这表明,即使对原设计作极小的改 变(更不用说对适配约束条件的改变),都会使适配器对原设计的布线(routing)和布局 (placing)策略作大幅改变和调整。同时,当设计规模比较大时,人为很难直接介入布线/ 布局的优化。对于由许多基本电路模块构建成的顶层系统的FPGA开发,类似的问题将更加 突出。例如,原来某一基本模块的PGA硬件测试十分成功,包括工作性能、速度以及资源 利用率等,但当将这些基本模块连接到一个顶层设计后,即使在同一FPGA中进行测试,也 常发现各模块以及总系统的性能有所下降,甚至无法工作的情况。事实上,如果能在设计基 本模块时,就固定其布线/布局的原方案,即使在顶层文件的总体适配时,也不改变原来基 本模块的布线/布局及其原来的优化方案,就能很好地解决上述棘手的问题。对此,Quartus Ⅱ提供了这一优秀的设计技术,可以将设计好的布线/布局方案。这样一来,对于一项较大 设计中的某一底层模块,不但在顶层的软件描述上是一个子模块,而且在FPGA芯片中总体 适配中,此模块在硬件便类似于ASIC设计中的一个标准模块,始终能保特自己原来的布线/ 布局方案,从而在任何大系统中都能保持原有的电路性能,就像一个被调用的独立的元件一 样,不会由于顶层系统布线/布局的改变而改变基本模块的布线/布局结构了。有了逻辑锁定 技术,面对大系统的设计,工程师们就可以将构成大系统的各模块进行分别设计,分别优化 它们的布线/布局,及适配约束,逐个地使它们分别获得最佳的工作性能,逐个优化交锁定 它们的布线/布局方案,最后把它们连在一起形成性能优良的顶层系统。显然,逻辑设计锁 定技术是SOPC单片系统优化设计及IP核成功拼装应用的有力保证。 (4)QuartusⅡ含有将FPGA设计向ASIC设计我缝转移的高效的ASIC设计技术,即 Hard Copy技术。HardCopy就是利用原有的FPGA开发工具,将成功实现于FPGA器件上的系 统通过特定的技术直接向ASIC转化,从而克服传统ASIC设计中普遍存在的问题。 与HardCopy技术相比,对于系统级的大规模ASIC开发,有不少难于克服的问题,其中 包括开发周期长、产品上市慢、一次性成功率低、有最少的投片量要求、设计软件工具繁多

芯片内设计者感兴趣的信号节点处的信号,而又不影响原硬件系统的正常工作。可以通过两 种方式来使用 Signal TapⅡ, 一种是直接使用 Quartus Ⅱ3.0 中的 Signal TapⅡ;另一种 方式是通过 MATLAB 的 Simulink 和 DSP Builder 来使用 Signal TapⅡ。DSP Builder 中包含 有 Signal TapⅡ模块,设计者可以使用此模块设置用于信号探察的事件触发器,配置存储 器, 下载 线将 (routing)和布局 (pl 线/ 个被调用的独立的元件一 ,不会由于顶层系统布线/布局的改变而改变基本模块的布线/布局结构了。有了逻辑锁定 工程师们就可以将构成大系统的各模块进行分别设计,分别优化 们的布线/布局,及适配约束,逐个地使它们分别获得最佳的工作性能,逐个优化交锁定 它们的布线/布局方案,最后把它们连在一起形成性能优良的顶层系统。显然,逻辑设计锁 定技术是 的高效的 ASIC 设计技术,即 Hard Cop 具,将成功实现于 FPGA 器件上的系 统通过特 在的问题。 与 H 有不少难于克服的问题,其中 包括 并能显示波形。这可以使用 Node 模块来选择有待监测的信号。使用 Signal TapⅡ后, 当触发器运行后,通常要占用部分内部 RAM,因为在实际监测中,将测得的样本信号暂存于 目标器件中的嵌入式 RAM(如 ESB)中,然后通过器件的 JTAG 端口和 Byte BlasterⅡ 采得的信息传出,送于 PC 机进行分析。PC 机中送达的数据是以文本文件的方式存储的, 并可在 Simulink 图上显示波形; (3) QuartusⅡ含有一种十分有效的逻辑设计优化技术,即设计模块在 FPGA 中指定区 域内的逻辑锁定功能,Logic Lock 技术。 有 FPGA 开发经验的人都会有这样的体会,原来在硬件测试上十分成功的 FPGA 设计,结 果在源代码并没有任何改变的情况下,仅仅是增加了一点与原程序毫不相干的电路描述,或 甚至只改变了某个端口信号的引脚锁定位置,结果在综合适配后,原设计的硬件性能大为下 降,如速度降低了,有时甚至无法正常工作。这时,如果比较改变设计前后的 Floorplan 图,会发现芯片内部资源的使用情况发生了巨大的变化。这表明,即使对原设计作极小的改 变(更不用说对适配约束条件的改变),都会使适配器对原设计的布线 acing)策略作大幅改变和调整。同时,当设计规模比较大时,人为很难直接介入布 布局的优化。对于由许多基本电路模块构建成的顶层系统的 FPGA 开发,类似的问题将更加 突出。例如,原来某一基本模块的 FPGA 硬件测试十分成功,包括工作性能、速度以及资源 利用率等,但当将这些基本模块连接到一个顶层设计后,即使在同一 FPGA 中进行测试,也 常发现各模块以及总系统的性能有所下降,甚至无法工作的情况。事实上,如果能在设计基 本模块时,就固定其布线/布局的原方案,即使在顶层文件的总体适配时,也不改变原来基 本模块的布线/布局及其原来的优化方案,就能很好地解决上述棘手的问题。对此,Quartus Ⅱ提供了这一优秀的设计技术,可以将设计好的布线/布局方案。这样一来,对于一项较大 设计中的某一底层模块,不但在顶层的软件描述上是一个子模块,而且在 FPGA 芯片中总体 适配中,此模块在硬件便类似于 ASIC 设计中的一个标准模块,始终能保持自己原来的布线/ 布局方案,从而在任何大系统中都能保持原有的电路性能,就像一 样 技术,面对大系统的设计, 它 SOPC 单片系统优化设计及 IP 核成功拼装应用的有力保证。 (4) QuartusⅡ含有将 FPGA 设计向 ASIC 设计我缝转移 y 技术。HardCopy 就是利用原有的 FPGA 开发工 定的技术直接向 ASIC 转化,从而克服传统 ASIC 设计中普遍存 ardCopy 技术相比,对于系统级的大规模 ASIC 开发, 开发周期长、产品上市慢、一次性成功率低、有最少的投片量要求、设计软件工具繁多

且昂贵、开发流程复杂等。例如,此类ASIC开发,首先要求可观的技术人员队伍、高达数 十万美元的开发软件费用,和高昂的掩模费用,有整个设计周期可能长达一年。ASIC设计 的高成本和一次性低成功率很大部分是由于需要设计和掩模的层数太多(多达十几层)。然 而如果利用HardCopy技术设计ASIC,开发软件费用仅2000美元(QuartusⅡ),S0C级规 模的设计周期不超过20周,转化的ASIC与用户设计习惯的掩模层只有两层,且一次性投片 的成功率近乎1OO%,即所谓的FPGA向ASIC的无缝转化。而且用ASIC实现后的系统性能将 比以前在HardCopy FPGA上验证的模型提高近50%,而功耗则降低40%。一次性成功率的大 幅度提高即意味着设计成本的大幅降低和产品上市速度的大幅提高。 HardCopy技术是一种全新的ASIC设计解决方案,即将专用的硅片设计和FPGA至 HardCopy自动迁移过程结合在一起的技术,即首先利用QuartusⅡ将系统模型成功实现于 HardCopy FPGA上,然后帮助设计得把可编程解决方案无缝地迁移到低成本的ASIC上的实 现方案。这样,HardCopy器件就把大容量FPGA的灵活性和ASIC的市场优势结合起来,实 现对于有大批量要求并对成本敏感的电子系统产品上。从而避开了直接设计ASIC的困难, 而从原型设计提升至产品制造,通过FPGA的设计十分容易地移植到HardCopy器件上,达到 降低成本,又加快面市周期的目的。HardCopy器件(如HardCopy Stratix系列、Excalibur 系列FPGA)避免了ASIC的风险,它采用FPGA的专用迁移技术。其HardCopy ASIC是直接 在Altera PLD体系之上构建的,采用有效利用面积“逻辑单元海”内核。本质上HardCopy 器件是FPGA的精确复制,剔除了可编程性、专用配置和采用金属互连使用的走线。这样器 件的硅片面积就更小,成本就更低,而且还改善了时序特性。 1.4本书中的系统配置 (1)运行Windows NT/2000/XP操作系统的PC (2)Nios嵌入式处理器软件(版本3.02)和S0 PC Builder软件(版本2.82或更高) (3)QuartusⅡ软件(版本2.2SP1或更高) (4)连接到PC的Nios开发板,同时提供三个开发包: Nios Development Kit,Stratix Edition Nios Development Kit,Stratix Professional Edition Nios Development Kit,Cyclone Edition 本部分内容中假定用户的工作目录在C:盘,Nios嵌入式处理器软件安装时创建的目录 结构缺省情况下位于\altera\kits\nios之下。 表1一2目录结构 目录 名 描 述 bin 包含了开发Nios硬件和软件设计的工具,包括GNW工具链。 components 包含了所有SOPC Builder的外设模块,每一个模块都有一个子 目录,其中都包括了一个描述该模块的class.ptf文件。 documents 包含了Nios嵌入式处理器软件、Nios开发板和GNUPro工具包的 文档资料。 examples 包含了Nios例子设计的子目录,包括standard_32工程, nios_system_,module设计基于此工程

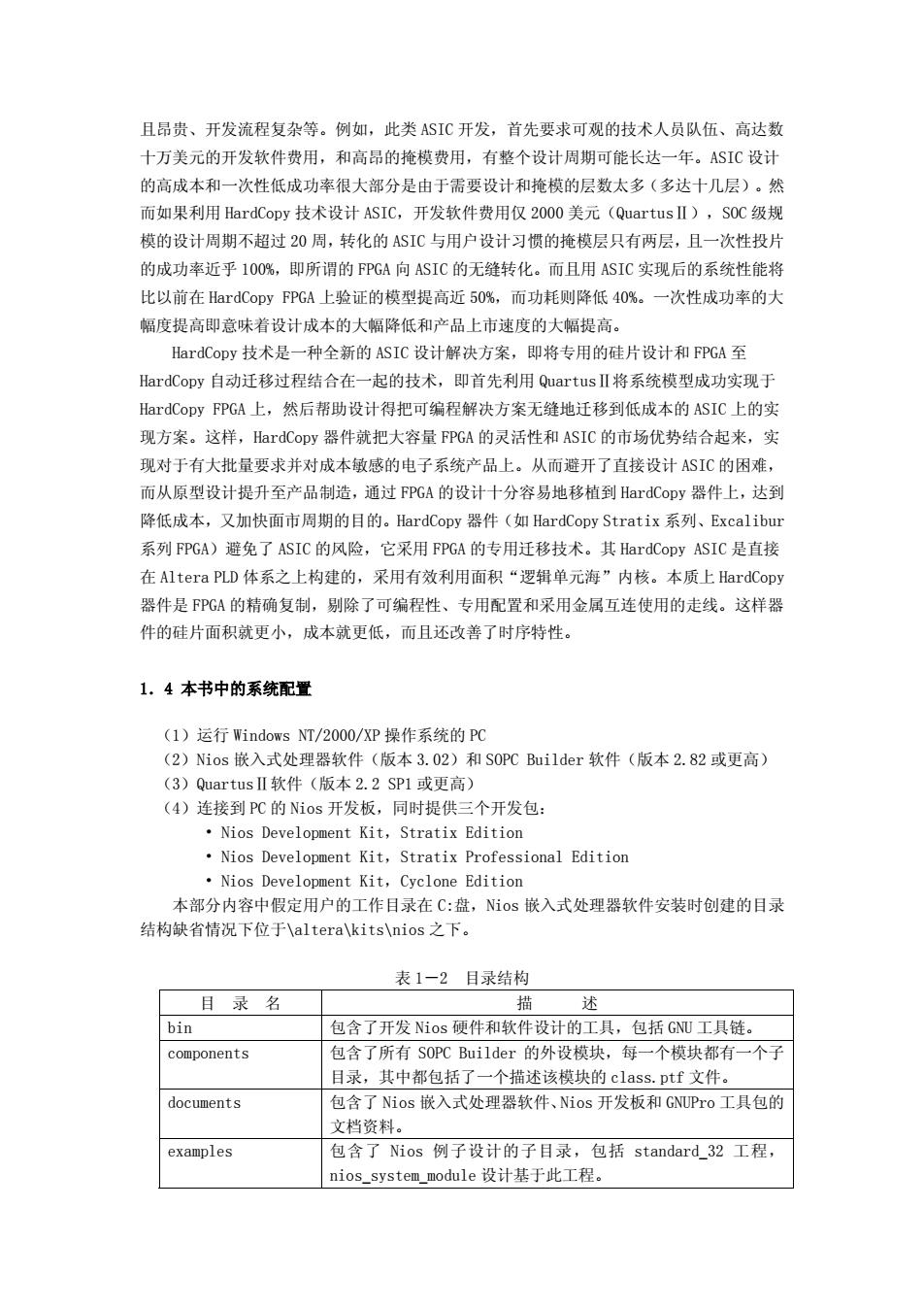

且昂贵、开发流程复杂等。例如,此类 ASIC 开发,首先要求可观的技术人员队伍、高达数 十万美元的开发软件费用,和高昂的掩模费用,有整个设计周期可能长达一年。ASIC 设计 的高成本和一次性低成功率很大部分是由于需要设计和掩模的层数太多(多达十几层)。然 而如果利用 技术设计 开发软件费用仅 模的设计周期不超过 20 周 投片 的成 0%,即所谓 比以前在 HardCopy FPGA 上验证的模型提高近 50%,而功耗则降低 40%。一次性成功率的大 幅度 着设计成本 HardCopy 技术是一种全 片设计和 FPGA 至 HardCopy HardCopy FPGA 上,然后帮助设计得把可编程解决方案无缝地迁移到低成本的 ASIC 上的实 现方案。这样,HardCopy 器件 优势结合起来,实 现对于有大批量要求并对成本敏感的电子系统产品上。从而避开了直接设计 ASIC 的困难, 而从原型设计提升至产品制造,通过 FPGA 的设计十分容易地移植到 HardCopy 器件上,达到 降低成本,又加快面市周期的目的。HardCopy 器件(如 HardCopy Stratix 系列、Excalibur 系列 FPGA)避免了 ASIC 的风险,它采用 FPGA 的专用迁移技术。其 HardCopy ASIC 是直接 在 Altera PLD 体系之上构建的,采用有效利用面积“逻辑单元海”内核。本质上 HardCopy 器件是 FPGA 的精确复制,剔除了可编程性、专用配置和采用金属互连使用的走线。这样器 件的硅片面积就更小,成本就更低,而且还改善了时序特性。 1.4 本书中的系统配置 (1)运行 Windows NT/2000/XP 操作系统的 PC (2)Nios 嵌入式处理器软件(版本 3.02)和 SOPC Builder 软件(版本 2.82 或更高) (3)QuartusⅡ软件(版本 2.2 SP1 或更高) (4)连接到 PC 的 Nios 开发板,同时提供三个开发包: • Nios Development Kit,Stratix Edition • Nios Development Kit,Stratix Professional Edition • Nios Development Kit,Cyclone Edition 本部分内容中假定用户的工作目录在 C:盘,Nios 嵌入式处理器软件安装时创建的目录 结构缺省情况下位于\altera\kits\nios 之下。 表 1-2 目录结构 目 录 名 描 述 HardCopy ASIC, 2000 美元(QuartusⅡ),SOC 级规 ,转化的 ASIC 与用户设计习惯的掩模层只有两层,且一次性 功率近乎 10 的 FPGA 向 ASIC 的无缝转化。而且用 ASIC 实现后的系统性能将 提高即意味 的大幅降低和产品上市速度的大幅提高。 新的 ASIC 设计解决方案,即将专用的硅 自动迁移过程结合在一起的技术,即首先利用 QuartusⅡ将系统模型成功实现于 就把大容量 FPGA 的灵活性和 ASIC 的市场 bin 包含了开发 Nios 硬件和软件设计的工具,包括 GNU 工具链。 components 包含了所有 SOPC Builder 的外设模块,每一个模块都有一个子 目录,其中都包括了一个描述该模块的 class.ptf 文件。 documents 包含了 Nios 嵌入式处理器软件、Nios 开发板和 GNUPro 工具包的 文档资料。 examples 包含了 Nios 例子设计的子目录,包括 standard_32 工程, nios_system_module 设计基于此工程

tutorials 包含了Nios嵌入式处理器和SOPC Builder的指南以及相关的文 件。该指南的目录可以在下面每一个开发包规范的目录下找到: (1)Nios_HW_Tutorial_Stratix_1S10 (2)Nios_HW_Tutorial_Cyclone_1C20 (3)Nios_HW_Tutorial_Stratix_1S40

tutorials 包含了 PC Builder 的指南以及相关的文 件。该指南的目录可以在下面每一个开发包规范的目录下找到: (1)Nios_HW_Tutorial_Stratix_1S10 (2)Nios_HW_Tutorial_Cyclone_1C20 Nios 嵌入式处理器和 SO (3)Nios_HW_Tutorial_Stratix_1S40