模块如图2所示,系统的输入信号有:计分复位端RST,加分按钮端ADD,减 分按钮端SUB,组别号输入端CHOS[3.0]。系统的输出信号有:A组分数输出端 AA23.0、AA1[3.0、AA0[3.0,B组分数输出端BB23.0、BB13.0、BB03.0, C组分数输出端CC2[3.01、CC1[3.01、CC0[3.0],D组分数输出端DD2[3.0小 DD1[3.0小、DD03.0]. JFQ 23 D01[3 DD3.1 图2 VHDL实现方法如下所示: (1)当按下RST键时,使分数复位,每位的初始分数为100分。 IF RST-I THEN POINTS_A2:="0001,POINTS_A1=0000" POINTS B2:="0001";POINTS B1:="0000" POINTS C2:="0001":POINTS C1:="0000": POINTS_D2:="0001";POINTS_D1:="0000" (2)当按下加分按钮端ADD时,以给A组加分为例。 IF POINTS_A1="1001"THEN POINTS_A1:="0000"; IF POINTS A2=1001"THEN POINTS_A2="0000: ELSE POINTS_A2:=POINTS_A2+"0001" END IF;

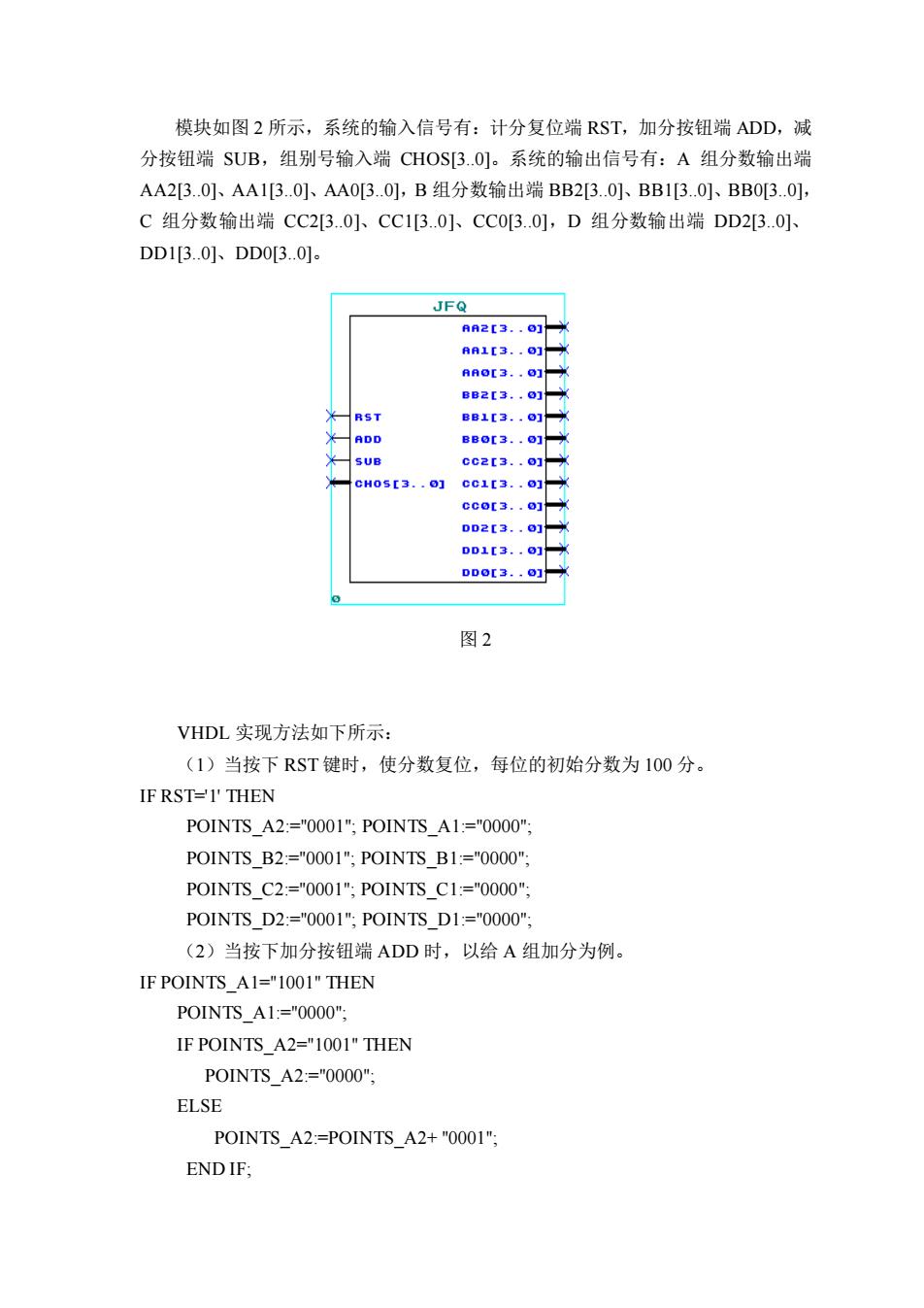

模块如图 2 所示,系统的输入信号有:计分复位端 RST,加分按钮端 ADD,减 分按钮端 SUB,组别号输入端 CHOS[3.0]。系统的输出信号有:A 组分数输出端 AA2[3.0]、AA1[3.0]、AA0[3.0],B 组分数输出端 BB2[3.0]、BB1[3.0]、BB0[3.0], C 组分数输出端 CC2[3.0]、CC1[3.0]、CC0[3.0],D 组分数输出端 DD2[3.0]、 DD1[3.0]、DD0[3.0]。 图 2 VHDL 实现方法如下所示: (1)当按下 RST 键时,使分数复位,每位的初始分数为 100 分。 IF RST='1' THEN POINTS_A2:="0001"; POINTS_A1:="0000"; POINTS_B2:="0001"; POINTS_B1:="0000"; POINTS_C2:="0001"; POINTS_C1:="0000"; POINTS_D2:="0001"; POINTS_D1:="0000"; (2)当按下加分按钮端 ADD 时,以给 A 组加分为例。 IF POINTS_A1="1001" THEN POINTS_A1:="0000"; IF POINTS_A2="1001" THEN POINTS_A2:="0000"; ELSE POINTS_A2:=POINTS_A2+ "0001"; END IF;

ELSE POINTS A1:=POINTS A1+"0001" ENDIF; (3)当按下减分按钮端SUB时,以给A组减分为例。 IF POINTS_A1="0000"THEN POINTS_A1:="1001" If POINTS A2=0000"THEN POINTS A2="1001": ELSE POINTS_A2:=POINTS_A2+"1111"; END IF: ELSE POINTS A1:=POINTS_A1+"1111": END IF: 在设计中减法的实现是以加法运算来实现的。以A为例,由于每次减分都是减 去10分,即每次为POINTS_.A1减一,所以可以用POINTS._A1+"III"来实现。如: 0111-0001=0110,用加法实现:0111+1111=10110。由于P0NTS_A1: STD LOGIC_VECTOR(3 DOWNTO 0),所以POINTS A1=O110。 计时器的设计与实现 本系统中的计时器电路既有计时初始值的预置功能,又有倒计数功能,功能比 较齐全。 模块如图3所示,系统输入信号有:系统清零信号CLR,计时预置控制端LDN, 计时使能端EN,系统时钟信号CLK,计时预置数据调整按钮TA、TB。系统输出 信号有:倒计时输出端QA3.0小、QB3.0]。 GLR 图3

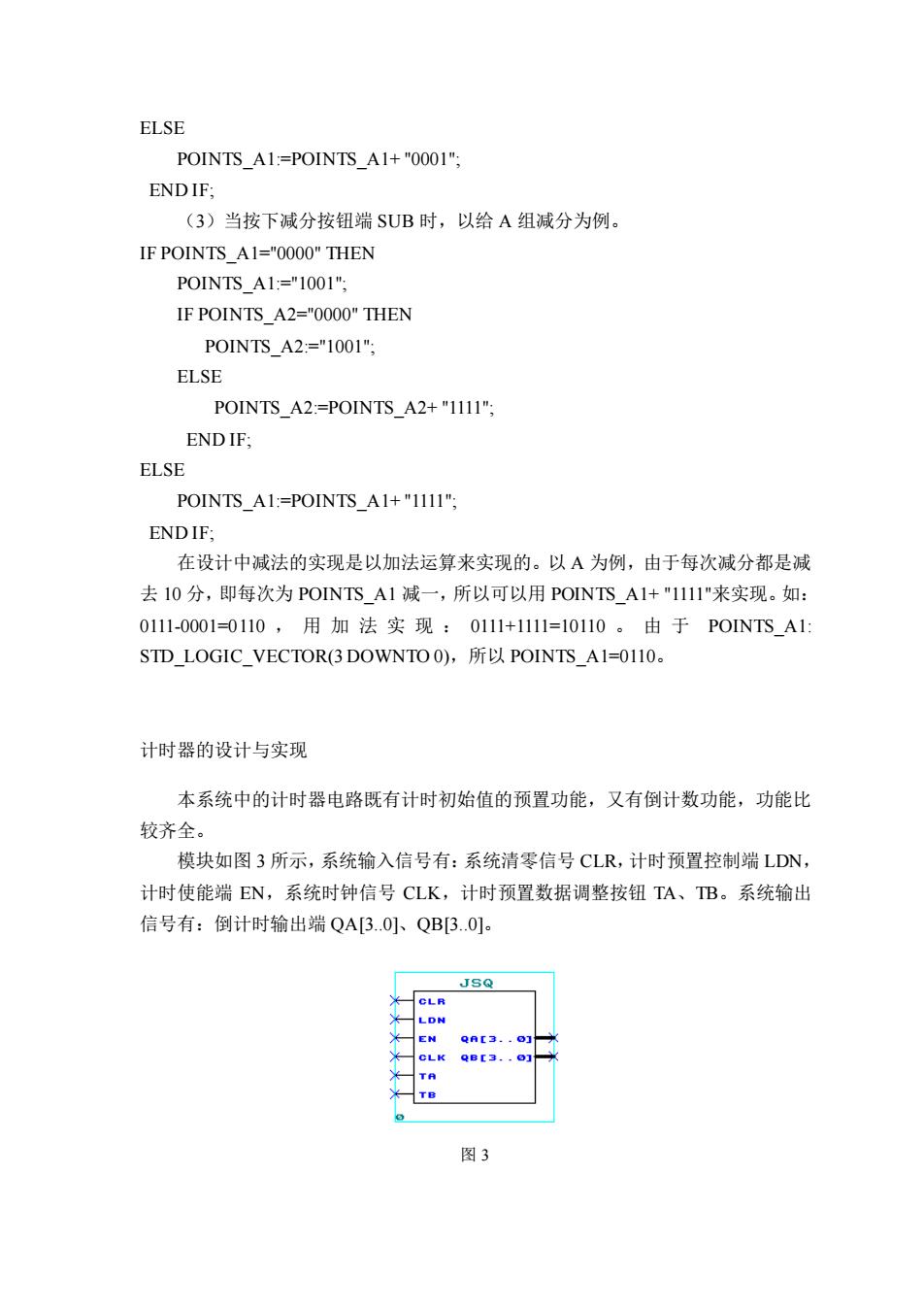

ELSE POINTS_A1:=POINTS_A1+ "0001"; END IF; (3)当按下减分按钮端 SUB 时,以给 A 组减分为例。 IF POINTS_A1="0000" THEN POINTS_A1:="1001"; IF POINTS_A2="0000" THEN POINTS_A2:="1001"; ELSE POINTS_A2:=POINTS_A2+ "1111"; END IF; ELSE POINTS_A1:=POINTS_A1+ "1111"; END IF; 在设计中减法的实现是以加法运算来实现的。以 A 为例,由于每次减分都是减 去 10 分,即每次为 POINTS_A1 减一,所以可以用 POINTS_A1+ "1111"来实现。如: 0111-0001=0110 ,用加法实现: 0111+1111=10110 。由于 POINTS_A1: STD_LOGIC_VECTOR(3 DOWNTO 0),所以 POINTS_A1=0110。 计时器的设计与实现 本系统中的计时器电路既有计时初始值的预置功能,又有倒计数功能,功能比 较齐全。 模块如图 3 所示,系统输入信号有:系统清零信号 CLR,计时预置控制端 LDN, 计时使能端 EN,系统时钟信号 CLK,计时预置数据调整按钮 TA、TB。系统输出 信号有:倒计时输出端 QA[3.0]、QB[3.0]。 图 3