Preemptive Scheduling I o CPU scheduling decisions may take place when a process: Switches from new to ready state Switches from running to ready state Switches from waiting to ready state Switches from running to waiting state ⑤Terminates For 4 &5,must schedule; For 1 &2 3,schedule?VS.not schedule? new (1)admit (2)interrupt (5)exit terminated ready running scheduler dispatch (3)1/O or event (4)1/O or event completion waiting wait 陈话兰xlanchen@ustc.edu:cn http:/staff.u0117401.Operating System操作系统原理 March27.201913/68

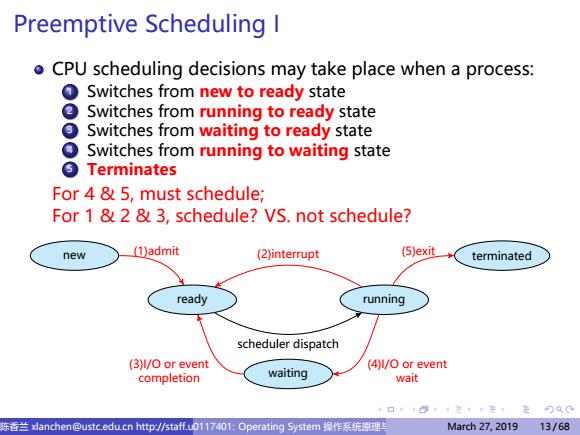

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Preemptive Scheduling I CPU scheduling decisions may take place when a process: 1 Switches from new to ready state 2 Switches from running to ready state 3 Switches from waiting to ready state 4 Switches from running to waiting state 5 Terminates For 4 & 5, must schedule; For 1 & 2 & 3, schedule? VS. not schedule? ready running scheduler dispatch (2)interrupt waiting (4)I/O or event wait (3)I/O or event completion new (1)admit terminated (5)exit 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 March 27, 2019 13 / 68

Preemptive Scheduling ll Two scheduling scheme: ●nonpreemptive(非抢占式):only4&5 Windows 3.x before Mac OS X otherwise preemptive(抢占式) Windows 95 &.. Mac OSX usually needs a hardware timer,synchronization overhead Two processes sharing data o If one process is preempted while it is updating the data, data is in an inconsistent(不-致)state 口1⊙注,1,2月00 陈话兰xlanchen@ustc.edu:cn http:/staff.u0117401.Operating System操作系统原理 March27.201914/68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Preemptive Scheduling II Two scheduling scheme: 1 nonpreemptive(非抢占式): only 4 & 5 ▶ Windows 3.x ▶ before Mac OS X 2 otherwise preemptive(抢占式) ▶ Windows 95 & ... ▶ Mac OS X ▶ usually needs a hardware timer, synchronization overhead Two processes sharing data If one process is preempted while it is updating the data, data is in an inconsistent(不一致) state 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 March 27, 2019 14 / 68

Preemptive Scheduling lll COST for preemption O needs special HW,for example,a timer. synchronization overhead with shared data. 东香兰xanchen@ustc.edu.cn http:/staff..u011740i:Operating System操作系统原理斐 March27.201915/68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Preemptive Scheduling III COST for preemption 1 needs special HW, for example, a timer. 2 synchronization overhead with shared data. 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 March 27, 2019 15 / 68

Preemption of the OS kernel o What happens if the process is preempted in the middle of some activities that changes important kernel data? o preemptive kernel VS.nonpreemptive kernel? o Interrupt affected code VS normal kernel code? o new mechnisms are needed,such as disable interrupt some synchronization mechnisms 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 March27.201916/68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Preemption of the OS kernel What happens if the process is preempted in the middle of some activities that changes important kernel data? preemptive kernel VS. nonpreemptive kernel? Interrupt affected code VS normal kernel code? new mechnisms are needed, such as ▶ disable interrupt ▶ some synchronization mechnisms 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 March 27, 2019 16 / 68

Outline Basic Concepts 0 CPU-1/O Burst Cycle o CPU Scheduler 0 Preemptive Scheduling ●Dispatcher 口1⊙生年12月00 陈话兰xlanchen@ustc.edu:cn http/staff.u0117401 Operating System操作系统原理斐 March27,201917/68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Outline 1 Basic Concepts CPU-I/O Burst Cycle CPU Scheduler Preemptive Scheduling Dispatcher 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 March 27, 2019 17 / 68