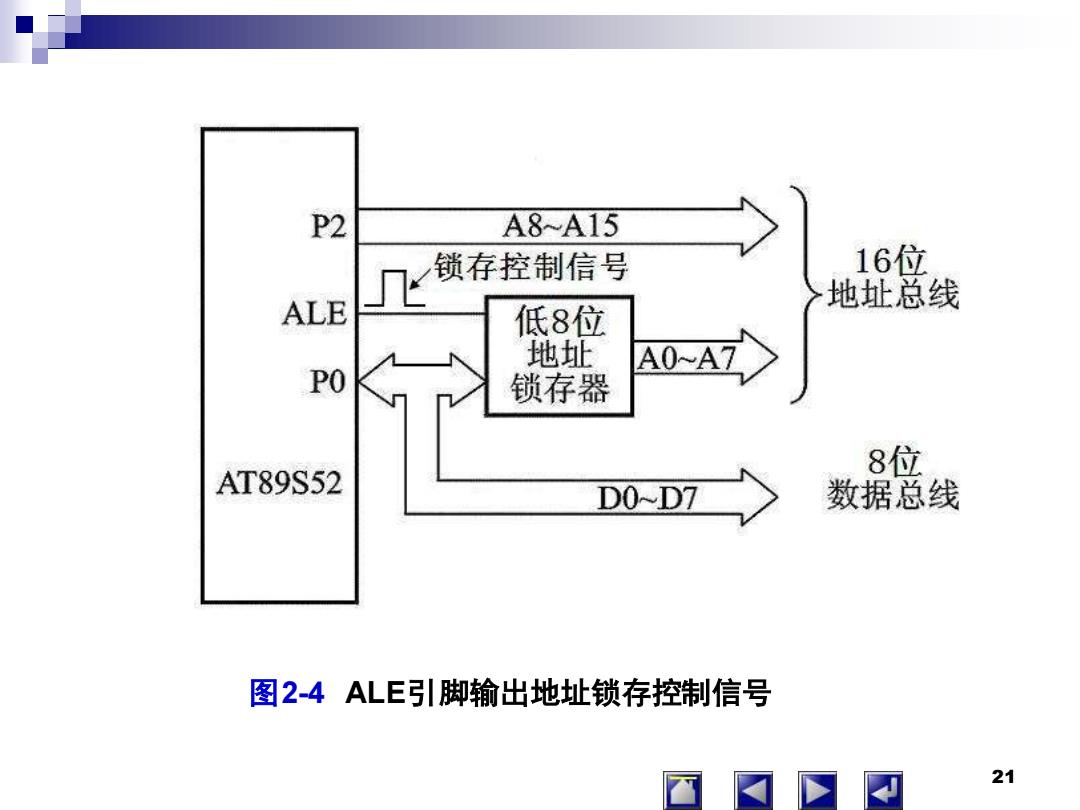

P2 A8~A15 锁存控制信号 16位 ALE 地址总线 低8位 地址 PO A0~A7 锁存器 8位 AT89S52 DO~D7 数据总线 图2-4ALE引脚输出地址锁存控制信号 21

21 图2-4 ALE引脚输出地址锁存控制信号

此外,单片机正常运行时,ALE端一直有正脉冲信号输出,此 频率为时钟频率f。的1/6。可用作外部定时或触发信号。 注意,每当AT89S52访问外部RAM时(执行MOVX类指令),要丢 失一个ALE脉冲。 如不需要ALE端输出脉冲信号,可将特殊功能寄存器AUXR(地 址为8EH,将在后面介绍)的第0位 (ALE禁止位)置1,来禁 止ALE操作,但执行访问外部程序存储器或外部数据存储器 指令“MOVC”或“MOVX”时,ALE仍然有效。即ALE禁止位不 影响对外部存储器的访问。 PR0G*:引脚第二功能,对片内Flash编程,为编程脉冲输入 脚。 22

22 此外,单片机正常运行时,ALE端一直有正脉冲信号输出,此 频率为时钟频率fosc的1/6。可用作外部定时或触发信号。 注意,每当AT89S52访问外部RAM时(执行MOVX类指令),要丢 失一个ALE脉冲。 如不需要ALE端输出脉冲信号,可将特殊功能寄存器AUXR(地 址为8EH,将在后面介绍)的第0位(ALE禁止位)置1,来禁 止ALE操作,但执行访问外部程序存储器或外部数据存储器 指令“MOVC”或“MOVX”时,ALE仍然有效。即ALE禁止位不 影响对外部存储器的访问。 PROG*:引脚第二功能,对片内Flash编程,为编程脉冲输入 脚。 22

(4)PSEN*(Program S Strobe ENable,29脚) 片外程序存储器读选通信号,低电平有效。 2.2.3 并行1/0▣引脚 (1)P0▣:P0.7~P0.0引脚 为漏极开路的8位并行双向/O口。作为输出口时,每个引脚 可驱动8个LS型TTL负载。当AT89S52扩展外部存储器及I/O接 口芯片时,P0口为分时复用的低8位地址/数据总线。在向P0口写 入“1”后就成为高阻态的输入口。 当P0口作为通用/O口使用时,需外加上拉电阻,这时为准双 向口。 在对Fash程序存储器编程时,P0口接收字节代码,程序校 验时P0口输出字节代码,程序校验期间应外接上拉电阻。 23

23 (4)PSEN*(Program Strobe ENable,29脚) 片外程序存储器读选通信号,低电平有效。 2.2.3 并行I/O口引脚 (1)P0口:P0.7~P0.0引脚 为漏极开路的8位并行双向I/O口。作为输出口时,每个引脚 可驱动8个LS型TTL负载。当AT89S52扩展外部存储器及I/O接 口芯片时,P0口为分时复用的低8位地址/数据总线。在向P0口写 入“1”后就成为高阻态的输入口。 当P0口作为通用I/O口使用时,需外加上拉电阻,这时为准双 向口。 在对Flash程序存储器编程时,P0口接收字节代码,程序校 验时P0口输出字节代码,程序校验期间应外接上拉电阻。 23

(2)P1口:P1.7≈P1.0引脚 准双向/O口,具有内部上拉电阻,可驱动4个LS型TTL负载。 在对片内Flash编程和校验时定义为低8位地址线。 P1口某些引脚的第二功能如下。 ● P1.0/T2:T2脚为定时器T2的外部计数信号输入端T2。 ●P1.1/T2EX:T2EX为T2的捕捉/重新装载触发及方向控制 T2EX。 P1.5/MOSI:MOSI用于对片内las存储器串行编程和校验。 ●P1.6MISO:MISO用于对片内Flash存储器串行编程和校验。 ● P1.7/SCK:SCK用于对片内F1ash存储器的串行编程和校验的 移位脉冲输入引脚。 24

24 (2)P1口:P1.7~P1.0引脚 准双向I/O口,具有内部上拉电阻,可驱动4个LS型TTL负载。 在对片内Flash编程和校验时定义为低8位地址线。 P1口某些引脚的第二功能如下。 P1.0/T2:T2脚为定时器T2的外部计数信号输入端T2。 P1.1/T2EX:T2EX为T2的捕捉/重新装载触发及方向控制 T2EX。 P1.5/MOSI:MOSI用于对片内Flash存储器串行编程和校验。 P1.6/MISO:MISO用于对片内Flash存储器串行编程和校验。 P1.7/SCK:SCK用于对片内Flash存储器的串行编程和校验的 移位脉冲输入引脚

注意:AT89S51与AT89S52引脚的差别仅仅是在1脚(P1.0)与2 脚(P1.1)上,AT89S52的1脚(P1.0)与2脚(P1.1)分别增加 了定时器/计数器T2的两个外部引脚T2和T2EX的复用功能。当 AT89S52单片机不使用片内的T2的两个引脚T2(P1.0)和T2EX (P1.1)的复用功能时,AT89S51以及各种8051兼容机与 AT8S52的脚功能则完全相同,它们的外围硬件接口电路是完 全相互通用的。 但是如果使用定时器T2的外部计数输入T2(P1.0)和“捕 捉”输入T2EX(P1.1)的功能时,则AT89S52的P1.0脚和P1.1 脚就不能作为通用I/O使用,这是AT89S52与AT89S51(或 AT89C51)在外围接口电路设计上的微小差别。 25

25 注意:AT89S51与AT89S52引脚的差别仅仅是在1脚(P1.0)与2 脚(P1.1)上,AT89S52的1脚(P1.0)与2脚(P1.1)分别增加 了定时器/计数器T2的两个外部引脚T2和T2EX的复用功能。当 AT89S52单片机不使用片内的T2的两个引脚T2(P1.0)和T2EX ( P1.1) 的复用功能时 , AT89S51以及各种 8051兼容机与 AT89S52的引脚功能则完全相同,它们的外围硬件接口电路是完 全相互通用的。 但是如果使用定时器T2的外部计数输入T2(P1.0)和“捕 捉”输入T2EX (P1.1)的功能时,则AT89S52的P1.0脚和P1.1 脚 就不能 作为 通用 I/O使 用, 这是 AT89S52与AT89S51(或 AT89C51)在外围接口电路设计上的微小差别