4.2程序存储器扩展 2.存储器的组成 2)地址译码电路 由地址信号选中某一存储单元,需经过地址译码电路。 3).片选和读写控制 地址线选通了片内某个存储单元,但只有当片选信号有效时, 才能对该存储单元进行读写操作。 4)数据输入输出电路 数据输入输出电路中有带三态门的输入缓冲器和输出缓冲器, 在片选和读/写信号控制下,实现数据的双向传送

2)地址译码电路 由地址信号选中某一存储单元,需经过地址译码电路。 3)片选和读/写控制 地址线选通了片内某个存储单元,但只有当片选信号有效时, 才能对该存储单元进行读/写操作。 4)数据输入/输出电路 数据输入/输出电路中有带三态门的输入缓冲器和输出缓冲器, 在片选和读/写信号控制下,实现数据的双向传送。 2.存储器的组成 4.2 程序存储器扩展

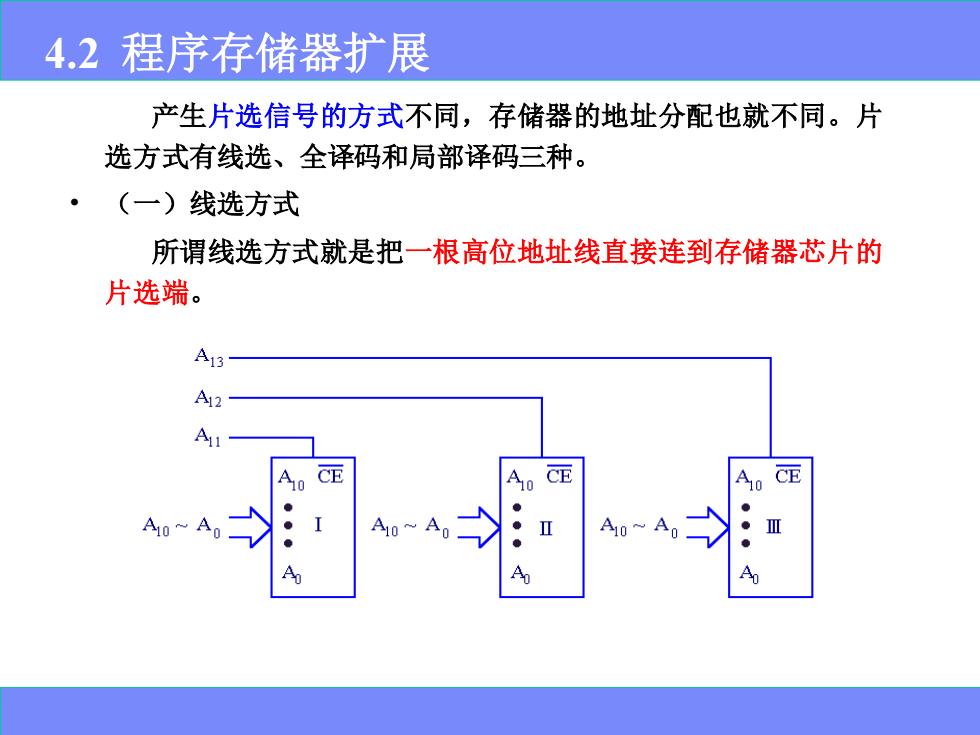

4.2程序存储器扩展 产生片选信号的方式不同,存储器的地址分配也就不同。片 选方式有线选、全译码和局部译码三种。 (一)线选方式 所谓线选方式就是把一根高位地址线直接连到存储器芯片的 片选端。 A13 A2 CE CE A10 A10

产生片选信号的方式不同,存储器的地址分配也就不同。片 选方式有线选、全译码和局部译码三种。 • (一)线选方式 所谓线选方式就是把一根高位地址线直接连到存储器芯片的 片选端。 4.2 程序存储器扩展

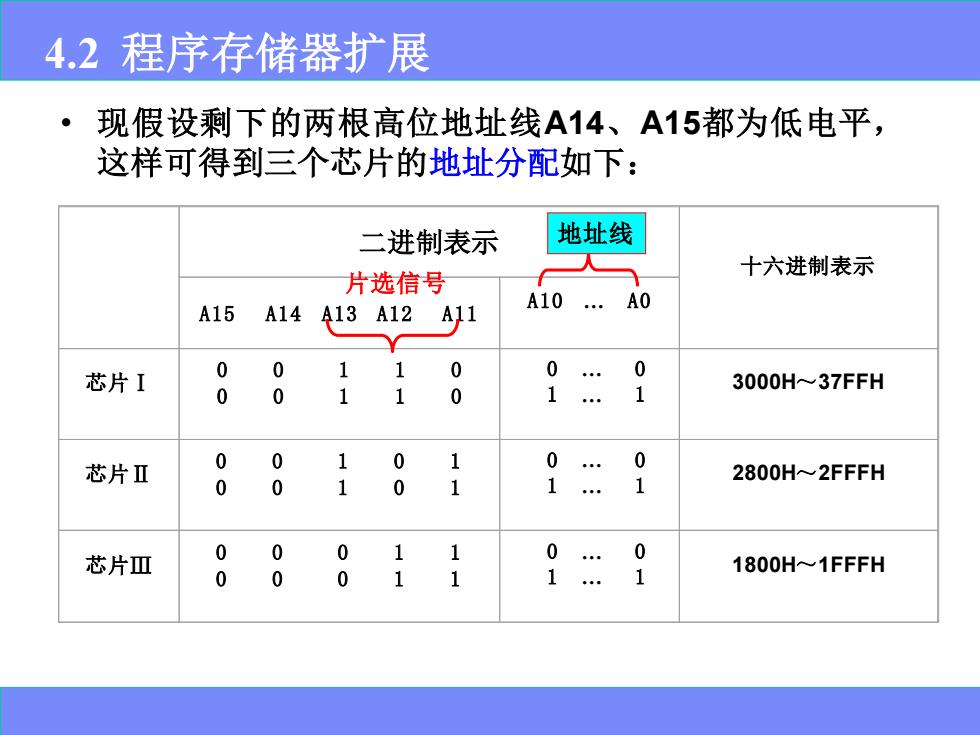

4.2程序存储器扩展 。 现假设剩下的两根高位地址线A14、A15都为低电平, 这样可得到三个芯片的地址分配如下: 二进制表示 地址线 十六进制表示 片选信号 A10.A0 A15 A14 A13A12 A11 芯片I 0 0 1 1 0 0 0 3000H~37FFH 0 0 1 1 0 1. 1 芯片Ⅱ 0 0 1 0 1 0 . 0 0 0 1 0 1 2800H~2FFFH 1 芯片Ⅲ 0 0 1 0 0 0 0 0 11 1. 1 1800H~1FFFH

• 现假设剩下的两根高位地址线A14、A15都为低电平, 这样可得到三个芯片的地址分配如下: 二进制表示 十六进制表示 A15 A14 A13 A12 A11 A10 . A0 芯片Ⅰ 0 0 1 1 0 0 0 1 1 0 0 . 0 1 . 1 3000H~37FFH 芯片Ⅱ 0 0 1 0 1 0 0 1 0 1 0 . 0 1 . 1 2800H~2FFFH 芯片Ⅲ 0 0 0 1 1 0 0 0 1 1 0 . 0 1 . 1 1800H~1FFFH 4.2 程序存储器扩展 片选信号 地址线

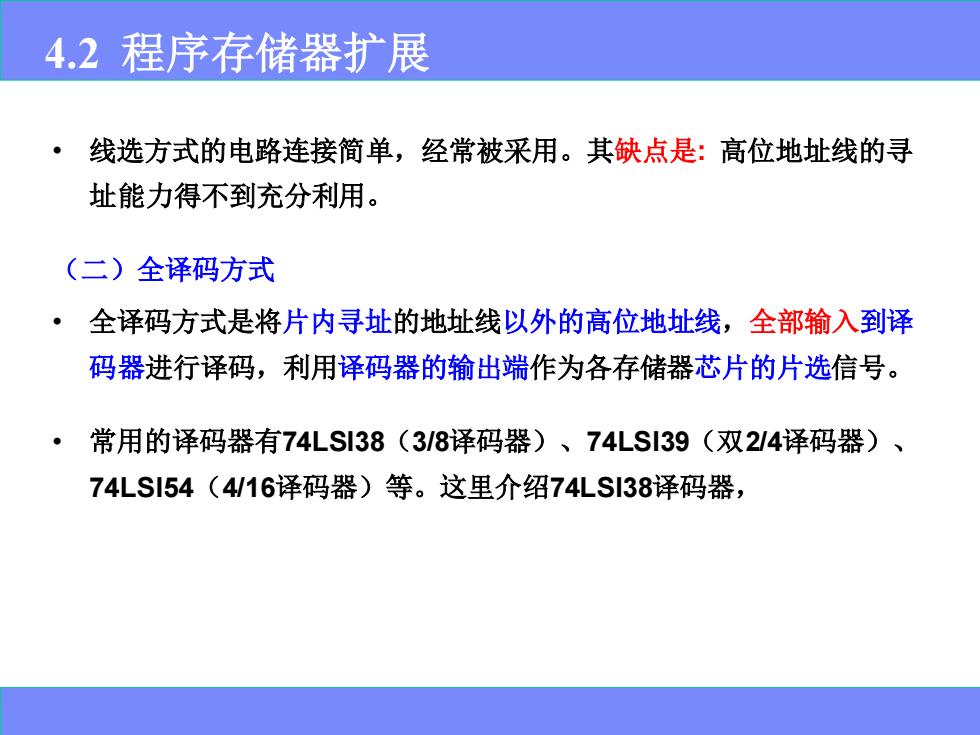

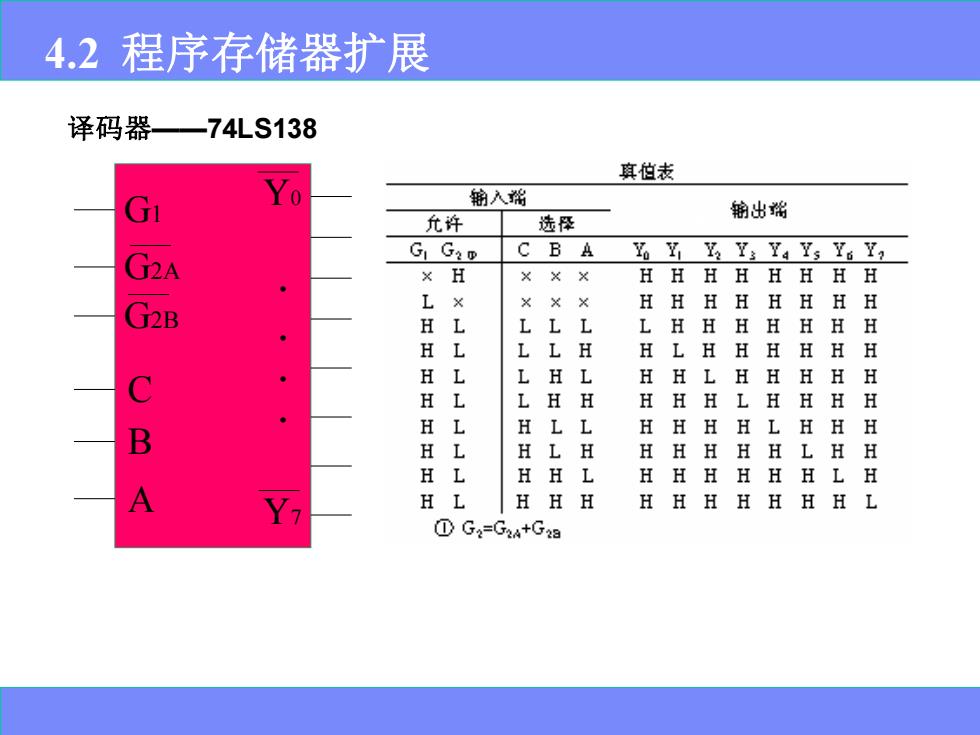

4.2程序存储器扩展 线选方式的电路连接简单,经常被采用。其缺点是:高位地址线的寻 址能力得不到充分利用。 (二)全译码方式 ·全译码方式是将片内寻址的地址线以外的高位地址线,全部输入到译 码器进行译码,利用译码器的输出端作为各存储器芯片的片选信号。 ·常用的译码器有74LS138(3/8译码器)、74LS139(双24译码器)、 74LS54(4W16译码器)等。这里介绍74LSI38译码器

• 线选方式的电路连接简单,经常被采用。其缺点是: 高位地址线的寻 址能力得不到充分利用。 (二)全译码方式 • 全译码方式是将片内寻址的地址线以外的高位地址线,全部输入到译 码器进行译码,利用译码器的输出端作为各存储器芯片的片选信号。 • 常用的译码器有74LSl38(3/8译码器)、74LSl39(双2/4译码器)、 74LSl54(4/16译码器)等。这里介绍74LSl38译码器, 4.2 程序存储器扩展

4.2程序存储器扩展 译码器 74LS138 真位表 G Yo 锦入粥 输出粥 允许 选径 GI G2D C BA G2A aY1Y2Y3Y4Y,Y。Y, H ×× HHHH HH HH G2B L × HH HHH H HH HL LLL HH H H H LH HH C H L L H L H H LH H 女 H H HH H HH LH H H H B H L H 日 H H L HH LHE L 日 H H H HHHH HH L ①G2=G2A+G2a

G1 G2A G2B C B A Y0 Y7 • • • • 译码器——74LS138 4.2 程序存储器扩展