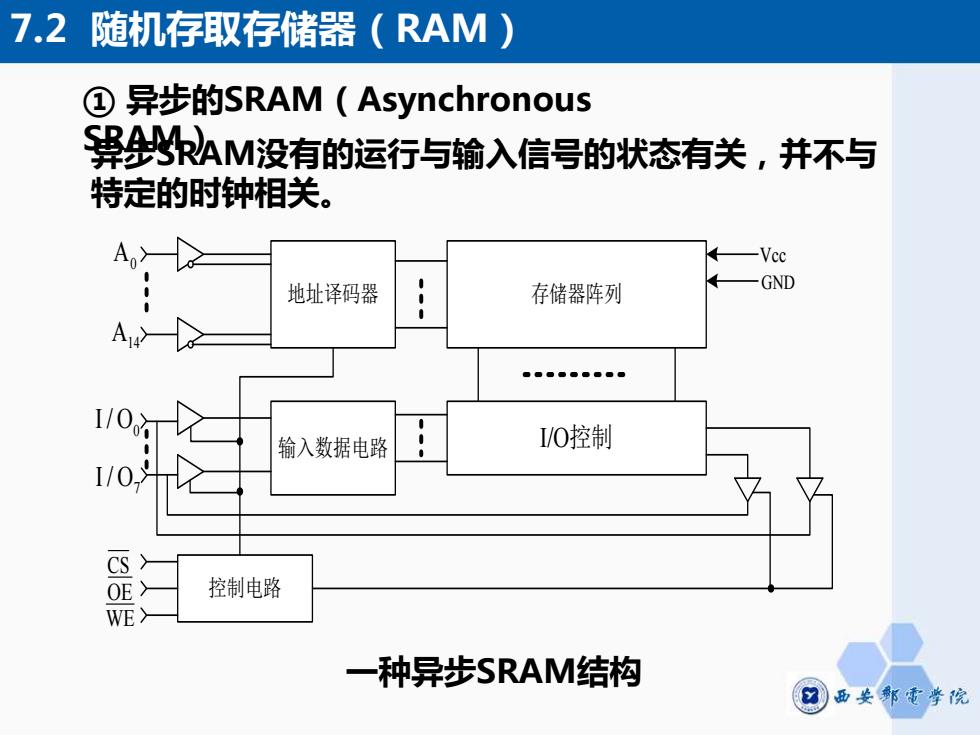

7.2 随机存取存储器(RAM) ①异步的SRAM(Asynchronous 参AM没有的运行与输入信号的状态有关,并不与 特定的时钟相关。 Vcc 地址译码器 存储器阵列 GND ●。●●。● 输入数据电路 I/O控制 /0 CS OE> 控制电路 WE> 一种异步SRAM结构

7.2 随机存取存储器(RAM) ① 异步的SRAM(Asynchronous SRAM 异步SRAM ) 没有的运行与输入信号的状态有关,并不与 特定的时钟相关。 一种异步SRAM结构 地址译码器 存储器阵列 输入数据电路 I/O控制 控制电路 A0 A140 I / O7 I / OCSOE WE Vcc GND

7.2 随机存取存储器( RAM 2 SSRAM (synchronous SRAM) 同步的SRAM有与微处理器同步的读、写周期,具有更 快的访问速度。因此,同步SRAM可以应用于个人计算 机和工作站上。 Clock >>数据寄存器 地址寄存器 A Q ←→Data Address RAM阵列 WE寄存器 WE 写脉冲产生器 一种SSRAM结构 ⊙画娄郭重学院

7.2 随机存取存储器(RAM) ② SSRAM(synchronous SRAM) 同步的SRAM有与微处理器同步的读、写周期,具有更 快的访问速度。因此,同步SRAM可以应用于个人计算 机和工作站上。 一种SSRAM结构 地址寄存器 寄存器 RAM阵列 写脉冲产生器 数据寄存器 Address Clock A Q Data DW WE WE

7.2 随机存取存储器(RAM) 突发方式(Burst Mode) 突发是指不需要修改地址,可以连续地对SSRAM内的 一片地址进行读/写。 SYNCHRONOUS MODE CLOCK 第一个数据的地址放在了 地址总线上,而其它三个 Address 数据块的地址则用内置的 Output 计数器改变,这样数据访 问的速率与微处理器的时 钟一致。 BURST MODE Address Output SSRAM的时序示意图

7.2 随机存取存储器(RAM) 突发方式(Burst Mode) 突发是指不需要修改地址,可以连续地对SSRAM内的 一片地址进行读/写。 SSRAM的时序示意图 第一个数据的地址放在了 地址总线上,而其它三个 数据块的地址则用内置的 计数器改变,这样数据访 问的速率与微处理器的时 钟一致

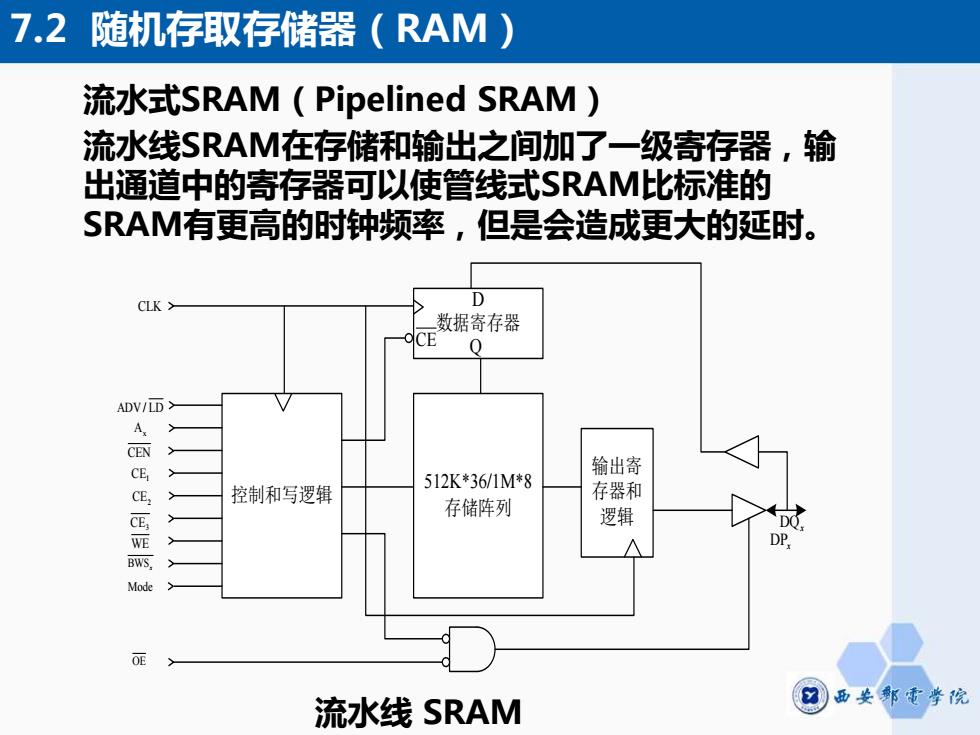

7.2 随机存取存储器(RAM) 流水式SRAM(Pipelined SRAM) 流水线SRAM在存储和输出之间加了一级寄存器,输 出通道中的寄存器可以使管线式SRAM比标准的 SRAM有更高的时钟频率,但是会造成更大的延时。 CLK 数据寄存器 0 ADV/LD A CEN CE 输出寄 CE, 控制和写逻辑 512K*36/1M*8 存器和 存储阵列 逻辑 8 BWS. Mode OE 流水线SRAM ⊙西重院

7.2 随机存取存储器(RAM) 流水式SRAM(Pipelined SRAM) 流水线SRAM在存储和输出之间加了一级寄存器,输 出通道中的寄存器可以使管线式SRAM比标准的 SRAM有更高的时钟频率,但是会造成更大的延时。 流水线 SRAM 控制和写逻辑 512K*36/1M*8 存储阵列 输出寄 存器和 逻辑 数据寄存器 Ax ADV / LD CEN CE1 CE2 CE3 WE BWSx Mode OECLK D CE Q DQx DP x