)西烤笔件技士 (2)在出现的对话框中选择Finish: Xilinx-ISE-L:\study\SATGEO\SatGEO_system_xilinx_tol2C_ov7\SatGEO_system_xilinx.ise-[PD_Lpf.vhd] File Edit View Project Source Process Window Help D目自名自哈X均 iMPACT Welcome to iMPACT 白回X G③,1二二雪皇A%% Please select an action from the list below Sources Configure devices using Boundary-Scan (TAG) Sources for:Implementation 包Sat50 ystom_11 Automatically connect to a cable and identify Boundary-Scan chain 日xc5vsx95t-2ff1136 ○Prepare a PROM File 日品SatGE0_system-system (SatG0_syste Prepare a Systam ACE File Inst_clkwork_signal_gen clk work 田间Inst_rs232_top-rg232_top-Behavic Prepare a Boundary-Scan File 甲同Inst_SatGE0 FnSeqGen-SatGEO_PnSeq Sw▣ SourcesPilesSnapshotsLi ○Configure devices using Slave Serial node Processes Processes for:SatGEO_system-system 中Cd>mnthes1ze-s1 中C2⑦Inplement Desi知 Generate Progranming File Configure Target Device Generate Target PROM/ACE File Manage Configuration Project (iMlPACT) Update Bitstream with Processor Data u Analyre Desig Using Chipscope 默Process5as INFO:1MPACT:2219 Status regist INF0:1 MPACT-0011111101011110 INFO:iMPACT:579-1':Completed 〈Back Finish Cancel Match cycle NoWait. Match cycle:NoWait 18 gong@xidian.edu.cn

fkgong@xidian.edu.cn 18 下载测试过程 (2)在出现的对话框中选择Finish;

(3)可在此处选择*.bit文件,或在后面再进行选择,此处以后一种为例,选择cancel 键,若有好几个片子,均如此选择; Xilinx-ISE-L\study\SATGEO\SatGEO_system_xilinx_tol2C_ov7\SatGEO_system_xilinx.ise-[Boundary Scan] File Edit View Project Source Process Operations Output Debug Window Help D3目自|6喧X购回®P式X回习名日四口P?0滴2 ④今4→三二三2A%光%心邀带蒸H田|#目静辟0初? Sources Boundary Scan oSlaveSerial a的SelectMAP Desktop Configuration Assign New Configuration File ?× Direet SPI Conficuration 目SystemACE Look in:白/stuy/SATGE0/SatG0.system_xi1ix-toI2c_ow7/▣←包心国鐘 目PR File Formatter 回satge0-system.bit _ngo SatGE0_system_xilinx_xdb work Sources Files SnapshoLibrari,Config xlnx_auto_0_xdb xst Processes Available Operations are: File name: Open Fi1etpg:A11 Design Fi1esk,bit米,rbt米.nly*,ise米.bsd) Cancel Cancel All Bypass 见Processes Configuration Operations None Enable Programming of SPI Flash Device Attached to this FPGA INFO:iMPACT:2219-Status register vai INF0:MPACT-0011111101011110000 Enable Programming of BPI Flash Device Attached to this FPGA TNFn·iMPACT.57a-I1I·Cnmn1=t=d doun1 19 gong@xidian.edu.cn

fkgong@xidian.edu.cn 19 下载测试过程 (3)可在此处选择*.bit文件,或在后面再进行选择,此处以后一种为例,选择cancel 键,若有好几个片子,均如此选择;

面烤笔件技老 (4)点击OK; Xilinx-ISE-L\study\SATGEO\SatGEOsystem_xilinx_tol2C_ov7\SatGEO_system_xilinxise-[Boundary Scan) File Edit View Project Source Process Operations Outout Debua Window Help 口3目自母角园X吟 Device Programming Properties.Device 1 Programming Properties X ④③4,1=三云24% Category Sources Device I FPGA¥v5t 命88 Boundary Sean Property Bane Value Verify SelectMAP FPGA Device Specific Progranning Froperties 的Desktop Configuration Fulse FROG Assert Cable INIT during programning 目PROM Fi1 Fornatter SourcesPi1es的Snapsho0Lhi站 Available Operations are: Frocesses Conficuration Operations X INFO:iMPACT:2219 -Status reg INF0:MPACT-001111110101 INFO:IMPACT:579-1:Comple Match cycle NoWait. Match cycle:NoWait TrE0:1PACT-1·:C的ec1nG '1':Programmed successfully PROGRESS END End Operation F1 angen t1ma三 m☐caea1☐kp1yap 20 gong@xidian.edu.cn

fkgong@xidian.edu.cn 20 下载测试过程 (4)点击OK;

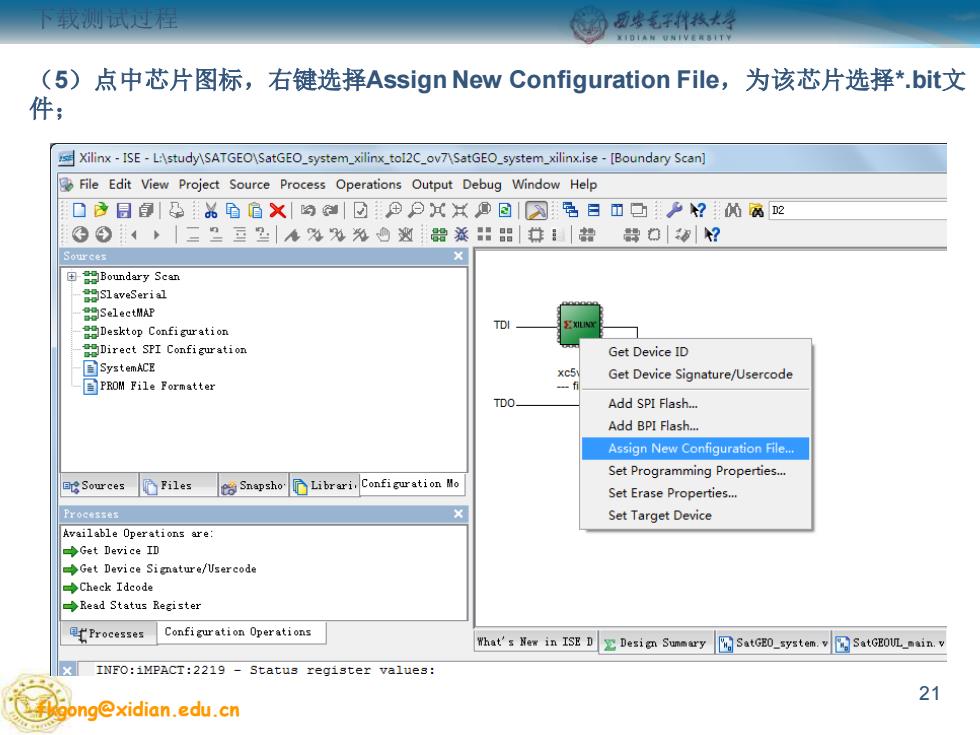

(5)点中芯片图标,右键选择Assign New Configuration File,为该芯片选择*.bit文 件: Xilinx-ISE-L:\study\SATGEO\SatGEO_system_xilinx_tol2C_ov7\SatGEO_system_xilinx.ise-[Boundary Scan] File Edit View Project Source Process Operations Output Debug Window Help D目自引马6鱼自X购回®户其H0回网马日m口严?价函2 ④今菲4,|二口运24%%%●邀器海出阳引#:”器口切? Sources 田Boundary Scan OSlaveSerial SelectMAP Desktop Configuration TDI Direct SPI Configuration Get Device ID 目SystemACE xc5 Get Device Signature/Usercode 目PROM File Formatter fi TDO. Add SPI Flash.. Add BPI Flash... Assign New Configuration File... Set Programming Properties.. SourcesFiles SnapshoLibrari,Configuration Mo Set Erase Properties... y0c台8e5 Set Target Device Available Operations are: ◆Get Device ID Get Device Signature/Usercode ◆Check Idcode →Read Status Register 式Processes Configuration Operations What's New in ISE_system.SatGBOUL sain.v INFO:iMPACT:2219 Status register values: 21 gong@xidian.edu.cn

fkgong@xidian.edu.cn 21 下载测试过程 (5)点中芯片图标,右键选择Assign New Configuration File,为该芯片选择*.bit文 件;