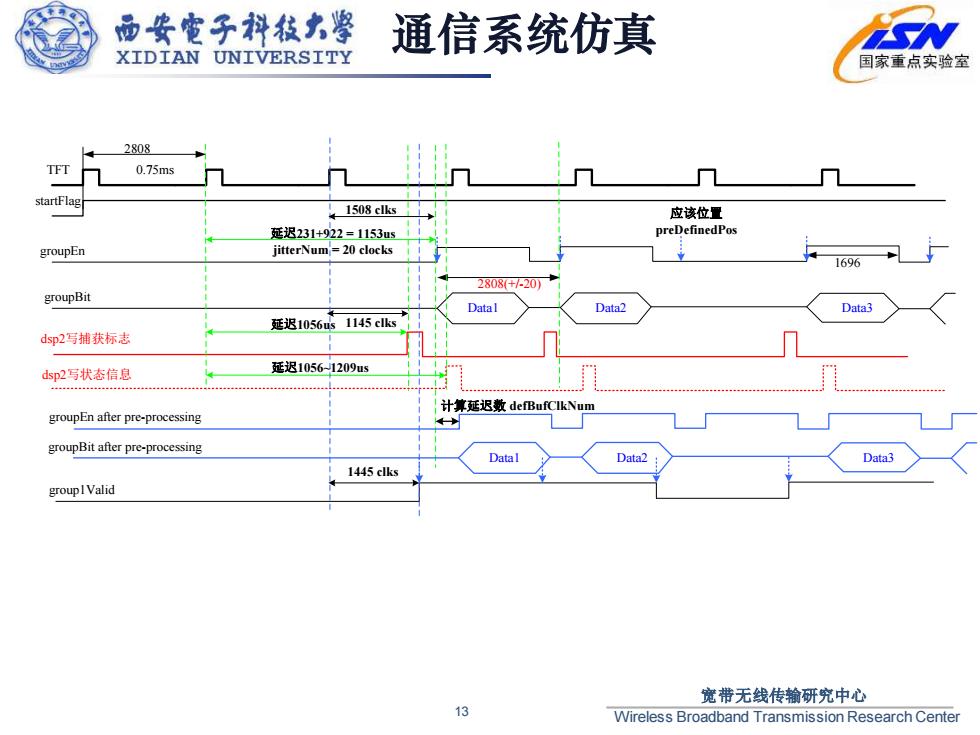

西安電子抖枝出粤 通信系统仿真 N XIDIAN UNIVERSITY 国家重点实验室 2808 TFT 0.75ms startFlag 1508 clks 应该位置 延迟231+922=1153us preDefinedPos groupEn jitterNum=20 clocks 1696 2808(+1-20) groupBit Datal Data2 Data3 延迟1056us1145cks dsp2写捕获标志 dsp2写状态信息 延迟1056-1209us 计算延迟数defBufClkNum groupEn after pre-processing groupBit after pre-processing Datal Data2 Data3 1445 clks groupI Valid 宽带无线传输研究中心 13 Wireless Broadband Transmission Research Center

宽带无线传输研究中心 Wireless Broadband Transmission Research Center 13 通信系统仿真 TFT 0.75ms groupEn groupBit 1696 2808 2808(+/-20) Data1 Data2 Data3 startFlag dsp2写捕获标志 延迟231+922 = 1153us jitterNum = 20 clocks 延迟1056us 延迟1056~1209us dsp2写状态信息 应该位置 preDefinedPos 计算延迟数 defBufClkNum groupEn after pre-processing Data1 Data2 Data3 groupBit after pre-processing 1445 clks group1Valid 1508 clks 1145 clks

西安電子科报大粤 自AUDC接口 自ATM接口 内部复位 点实验 复位 复位 108.5441时钟 比特数据 ATM到AUDC 头标志 Chipscope 测试数据 接口转换 108.544M 目前采用加电复位! 测试核 175.104M 除了起到控制作用,如产生 数字分频 读写地址等,还将模块返回 119.808M 比特 的串行数据组成(替换)连续 544/16MHz 108.544MHz 的比特帧。 3.744MHz时钟 Group1使舵 需要采用ILA+CON的模式, Groupl数据 否则可能存在综合问题。可以 108.5441时钟 美 放置到其他层次。 组锁 出特敦海 提供组帧模块载波捕获信 主要考虑多种情况: 控制 息,目前地址为80、81 1.开机时没有* 2.运行过程中 四部分类似,通过一个FFO和一个乒 27gCg 3.要保证同步 乓RAM组合实现,其中读写控制由总 该子模块输出 控制单元和内部控制单元共同完成。 及锁定信息提取 14.9761 能 数据 424组帧 FPGA6 使鲍 去模拟上下频 执0C巷口 原来在DSP2处理,因为存 为了弥补其在译码FPGA 延迟 在一定难度,放置到 72M 的延迟 FPGA6处理 75 时标 超帆时标顿时标计戴 标注: 去DSP接口 去WRMT接口 宽韩镜研究而 Vireless☐ 2dba单线输missio心当s单4

宽带无线传输研究中心 Wireless Broadband Transmission Research Center 并串转换 108.544M 119.808M 自FPGA5 译码信息接口 自FPGA5 帧时标接口 自DSP2接口 去ATM接口 去AUDC接口 DCM核 数字分频 108.544MHz 108.544/16MHz 14.976MHz 3.744MHz 1.872MHz 3.744MHz时钟 Group1使能 Group1数据 帧再生 组帧 总控制 单元 帧再生 帧再生 帧再生 特殊字节ROM 15bits 15bits 14bits 并串转换 载波锁定标志 47+3bits FIFO 控 制 RAM 乒 RAM 乓 FIFO FIFO FIFO Chipscope 测试核 424组帧 去模拟上下频单机AUDC 去 载波锁定信息提取 无线 资源 管理 WRMT 接口 喂狗 单元 CE AWE AWA AED 1.872MHz 14.976MHz ATM到AUDC 接口转换 FPGA6到AUDC 接口转换 108.544M时钟 比特数据 头标志 14.976M 数据 使能 去AUDC接口 AUDC到检测 设备接口转换 175.104M时钟 比特数据 去WRMT接口 超帧时标 帧时标计数 0.75ms帧时标 去检测接口 0.75ms 帧时标 1.872M GPIO 去DSP接口 Watch Dog 延迟RAM 自AUDC接口 自ATM接口 控 制 控 制 控制 RAM 乒 RAM 乓 RAM 乒 RAM 乓 32bits 108.544M时钟 比特数据 头标志 突发 超帧 1.872MHz 1.872MHz 复位 复位 内部复位 3.744MHz 108.544/16MHz 108.544MHz 测试数据 标注: 差分输入 BUS输入 差分输出 BUS输出 单线输入 单线输出 主要考虑多种情况: 1. 开机时没有数据和使能信号; 2. 运行过程中使能可能没有; 3. 要保证同步、抖动 该子模块输出保证了连续规则的使 能 四部分类似,通过一个FIFO和一个乒 乓RAM组合实现,其中读写控制由总 控制单元和内部控制单元共同完成。 除了起到控制作用,如产生 读写地址等,还将模块返回 的串行数据组成(替换)连续 的比特帧。 需要采用ILA+ICON的模式, 否则可能存在综合问题。可以 放置到其他层次。 原来在DSP2处理,因为存 在一定难度,放置到 FPGA6处理 提供组帧模块载波捕获信 息,目前地址为80、81 为了弥补其在译码FPGA 的延迟 目前采用加电复位!

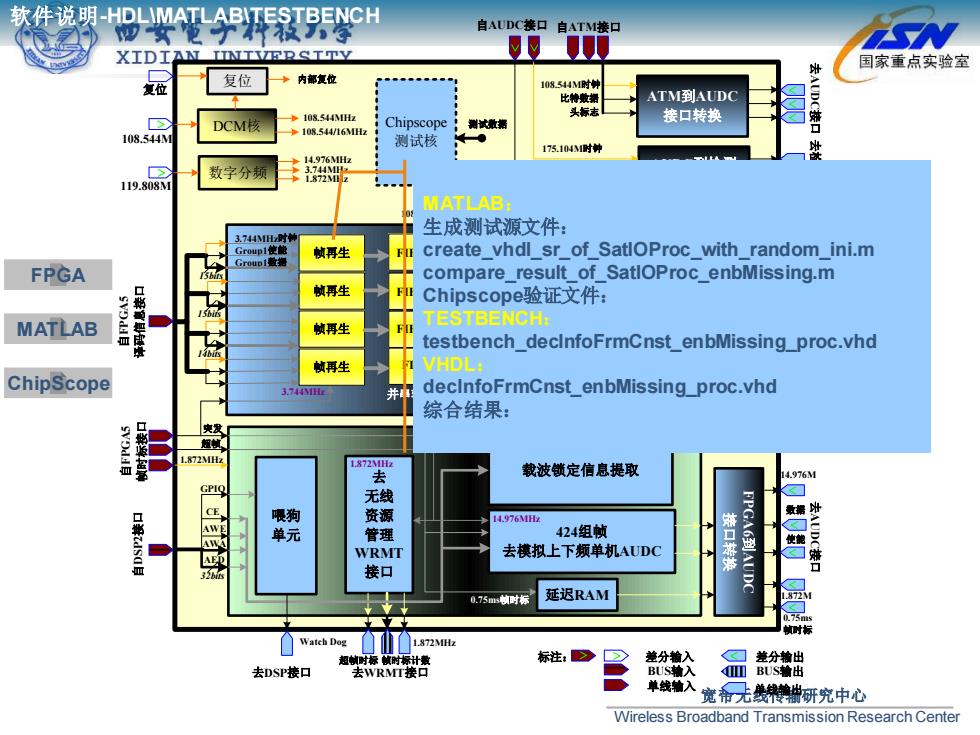

软件说明-HDLIMATLABITESTBENCH 自AUDC接口自ATM接口 XIDIAN IINIVERSITY 国家重点实验室 复位 →内部复位 108.544M时钟 ATM到AUDC 头标去 接口转换 DCM核 108.544MH 108.544/16MH Chipscope 测试据 108.544 测试核 175.104M时钟 14.9761Hz 数字分频 119.808M MATLAB: 生成测试源文件: 帧再生 create_vhdl_sr_of_SatlOProc_with_random_ini.m FPGA compare result of SatlOProc enbMissing.m 口 帧再生 Chipscope验证文件: MATLAB TESTBENCH: 帧再生 testbench_declnfoFrmCnst_enbMissing_proc.vhd 帧再生 VHDL: ChipScope 3.7441H declnfoFrmCnst_enbMissing_proc.vhd 综合结果: 夹发 名 872MH2 载波锁定信息提取 1.9761 无线 喂狗 资源 14.976MH 单元 管理 424组帧 WRMT 去模拟上下频单机AUDC 口 接口 0.15m 时标 延迟RAM Watch Dog 1.872MH 超制时时标计 标注: 差分输入 差分输出 去DSP接口 去WRMT接口 BUS轴入 ⅢBUS输出 单线输入 宽希无畿牌轴研究中心 Wireless Broadband Transmission Research Center

宽带无线传输研究中心 Wireless Broadband Transmission Research Center 软件说明-HDL\MATLAB\TESTBENCH 并串转换 108.544M 119.808M 自FPGA5 译码信息接口 自FPGA5 帧时标接口 自DSP2接口 去ATM接口 去AUDC接口 DCM核 数字分频 108.544MHz 108.544/16MHz 14.976MHz 3.744MHz 1.872MHz 3.744MHz时钟 Group1使能 Group1数据 帧再生 组帧 总控制 单元 帧再生 帧再生 帧再生 特殊字节ROM 15bits 15bits 14bits 并串转换 载波锁定标志 47+3bits FIFO 控 制 RAM 乒 RAM 乓 FIFO FIFO FIFO Chipscope 测试核 424组帧 去模拟上下频单机AUDC 去 载波锁定信息提取 无线 资源 管理 WRMT 接口 喂狗 单元 CE AWE AWA AED 1.872MHz 14.976MHz ATM到AUDC 接口转换 FPGA6到AUDC 接口转换 108.544M时钟 比特数据 头标志 14.976M 数据 使能 去AUDC接口 AUDC到检测 设备接口转换 175.104M时钟 比特数据 去WRMT接口 超帧时标 帧时标计数 0.75ms帧时标 去检测接口 0.75ms 帧时标 1.872M GPIO 去DSP接口 Watch Dog 延迟RAM 自AUDC接口 自ATM接口 控 制 控 制 控制 RAM 乒 RAM 乓 RAM 乒 RAM 乓 32bits 108.544M时钟 比特数据 头标志 突发 超帧 1.872MHz 1.872MHz 复位 复位 内部复位 3.744MHz 108.544/16MHz 108.544MHz 测试数据 标注: 差分输入 BUS输入 差分输出 BUS输出 单线输入 单线输出 MATLAB: 生成测试源文件: create_vhdl_sr_of_SatIOProc_with_random_ini.m compare_result_of_SatIOProc_enbMissing.m Chipscope验证文件: TESTBENCH: testbench_decInfoFrmCnst_enbMissing_proc.vhd VHDL: decInfoFrmCnst_enbMissing_proc.vhd 综合结果: FPGA MATLAB ChipScope

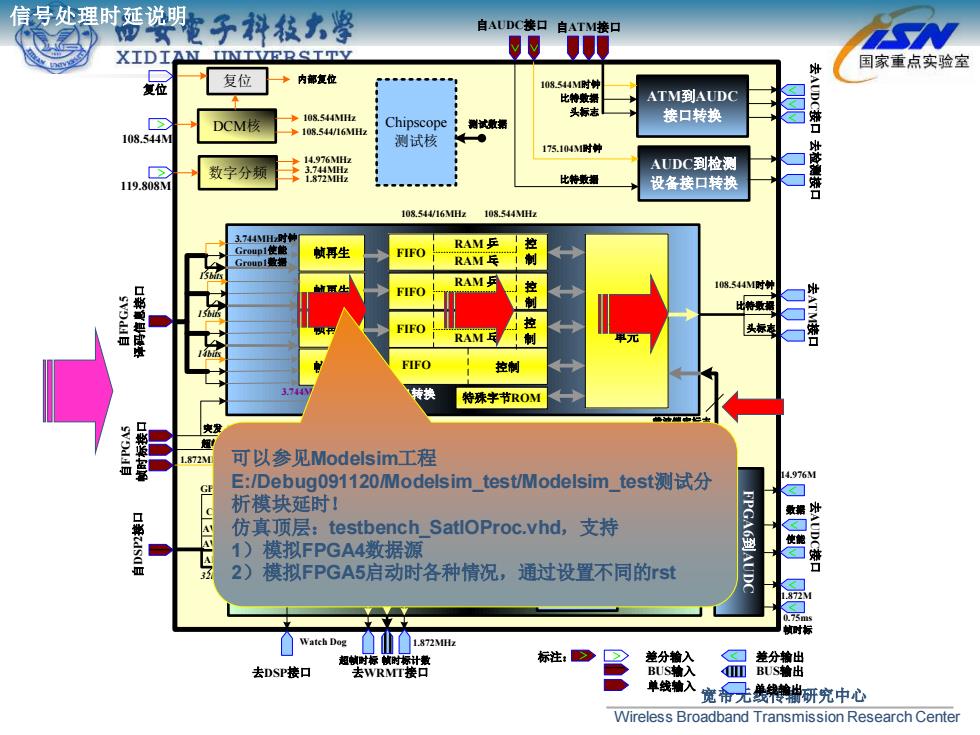

自AUDC接口 自ATM接口 XIDIAN IINIVERSTTY 国家重点实验室 复位 →内部复位 085441时 比特烟 ATM到AUDC 头标志 108.544Hz 接口转换 DCM核 Chipscope 测试微语 东V咖C接口 108.544 10s.544/16MHE 测试核 175.104M时钟 数字分频 AUDC到检测 119.808M 比转数凝 设备接口转换 108.544/16MHz 108.544M 44MH时钟 使能 RAM乒 顿再生 FIFO RAM乓 RAM月 108.54HM时钟 IFO 头标店 RAME 控制 特半节ROM 口 1.872 可以参见Modelsim工程 E:Debug091120 Modelsim_test/Modelsim_test测试分 4.976 析模块延时1 仿真顶层:testbench_SatlOProc.vhd,支持 1)模拟FPGA4数据源 五 2) 模拟FPGA5启动时各种情况,通过设置不同的rst 时 Watch Dog 去装皆 标注: 去DSP接口 > 品款出 单线轴入 宽无特鸛研究中心 Wireless Broadband Transmission Research Center

宽带无线传输研究中心 Wireless Broadband Transmission Research Center 信号处理时延说明 并串转换 108.544M 119.808M 自FPGA5 译码信息接口 自FPGA5 帧时标接口 自DSP2接口 去ATM接口 去AUDC接口 DCM核 数字分频 108.544MHz 108.544/16MHz 14.976MHz 3.744MHz 1.872MHz 3.744MHz时钟 Group1使能 Group1数据 帧再生 组帧 总控制 单元 帧再生 帧再生 帧再生 特殊字节ROM 15bits 15bits 14bits 并串转换 载波锁定标志 47+3bits FIFO 控 制 RAM 乒 RAM 乓 FIFO FIFO FIFO Chipscope 测试核 424组帧 去模拟上下频单机AUDC 去 载波锁定信息提取 无线 资源 管理 WRMT 接口 喂狗 单元 CE AWE AWA AED 1.872MHz 14.976MHz ATM到AUDC 接口转换 FPGA6到AUDC 接口转换 108.544M时钟 比特数据 头标志 14.976M 数据 使能 去AUDC接口 AUDC到检测 设备接口转换 175.104M时钟 比特数据 去WRMT接口 超帧时标 帧时标计数 0.75ms帧时标 去检测接口 0.75ms 帧时标 1.872M GPIO 去DSP接口 Watch Dog 延迟RAM 自AUDC接口 自ATM接口 控 制 控 制 控制 RAM 乒 RAM 乓 RAM 乒 RAM 乓 32bits 108.544M时钟 比特数据 头标志 突发 超帧 1.872MHz 1.872MHz 复位 复位 内部复位 3.744MHz 108.544/16MHz 108.544MHz 测试数据 标注: 差分输入 BUS输入 差分输出 BUS输出 单线输入 单线输出 可以参见Modelsim工程 E:/Debug091120/Modelsim_test/Modelsim_test测试分 析模块延时! 仿真顶层:testbench_SatIOProc.vhd,支持 1)模拟FPGA4数据源 2)模拟FPGA5启动时各种情况,通过设置不同的rst

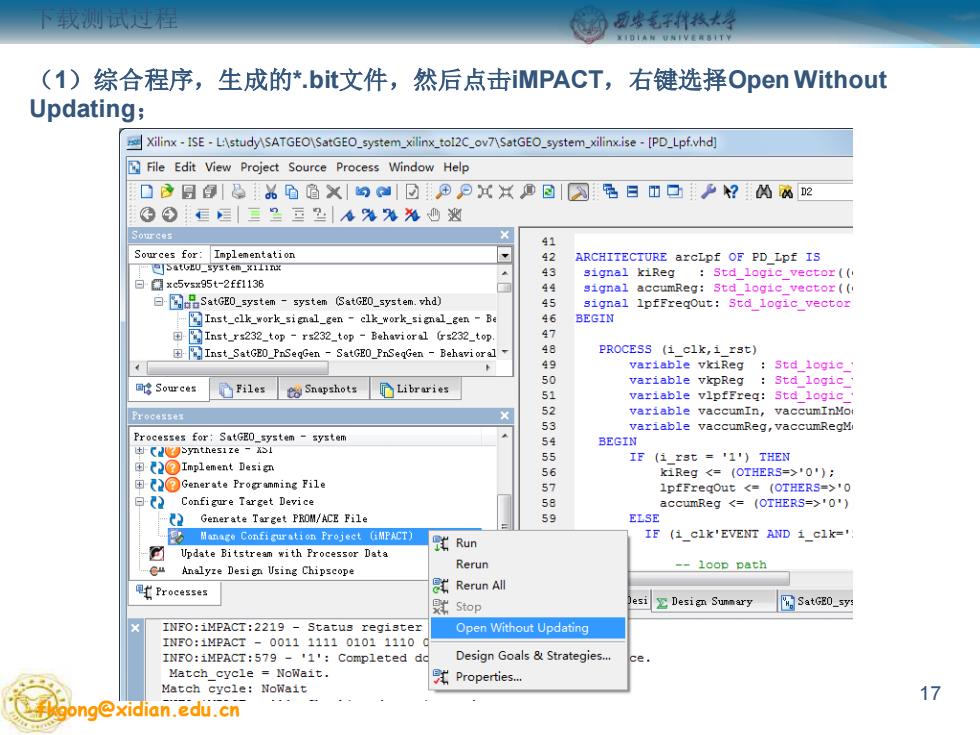

零多子州技大 (1)综合程序,生成的*.bit文件,然后点击iMPACT,右键选择Open Without Updating; Xilinx-ISE-L\studySATGEO\SatGEO_system_xilinx_tol2C_ov7\SatGEO_system_xilinx.ise-[PD_Lpf.vhd] File Edit View Project Source Process Window Help D心日自16哈自X|。回®P其X月回习路日田口严?的%2 G③层|三2三2|4%%%●巡 Sources 9 Sources for:Implementation 4 ARCHITECTURE arcLpf OF PD Lpf Is SatGHU-system_xilIn 43 signal kiReg Std logic vector(( 白黑xc5wsx95t-2ff1136 signal accumReg:Std_logic_vector(( 白品SatGE(0 system-system(SatG0_system..vhd) signal lpfFreqout:Std logic vector Inst_clk_work_signal_gen-clk_work_signal_gen -Be 46 BEGIN Inst_rs232_top rs232_top Behavioral (rs232_top. 47 Inst_SatGEO_PnSeqGen -SatGEO_PnSeqGen Behavioral PROCESS (i clk,i rst) 49 variable vkiReg Std logic SourcesFiles f SnapshotsLibraries variable vkpReg Std logic 51 variable vlpfFreq:Std_logic_ 52 variable vaccumIn,vaccumInMo 53 variable vaccumReg,vaccumRegM Processes for:SatGEO_system-system 54 BEGI Synthesize IF (i rst =1')THEN 甲C2⑦Implement Design 56 kiReg <(OTHERS=>'0'); Generate Programming File 5 1pfFreqout <(OTHERS=>'0 Configure Target Device accumReg <(OTHERS=>'0') Generate Target PROM/ACE File 59 ELSE Manage Configuration Project (iMPACT) Run IF (i clk'EVENT AND i_clk=' Update Bitstream with Processor Data Cu Analyze Design Using Chipscope Rerun --loop path Processes 默Rerun All Stop lesi Design Sunmary w SatGEO_sys + INFO:iMPACT:2219-Status register Open Without Updating IF0:1 MPACT-0011111101011110 INFO:iMPACT:579 -'1':Completed dc Design Goals Strategies.. Match cycle NoWait. Properties... Match cycle:NoWait 17 gong@xidian.edu.cn

fkgong@xidian.edu.cn 17 下载测试过程 (1)综合程序,生成的*.bit文件,然后点击iMPACT,右键选择Open Without Updating;