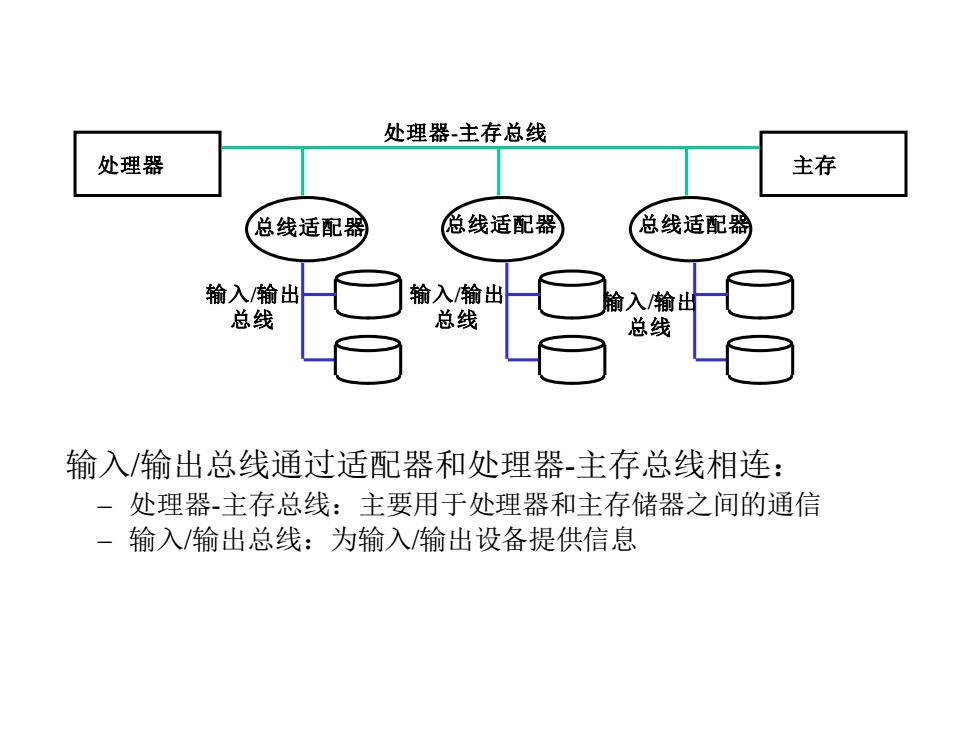

处理器主存总线 处理器 主存 总线适配器 总线适配器 总线适配器 输入输出 输入输出 输入输出 总线 总线 总线 输入/输出总线通过适配器和处理器-主存总线相连: 一处理器主存总线:主要用于处理器和主存储器之间的通信 -输入/输出总线:为输入输出设备提供信息

输入/输出总线通过适配器和处理器-主存总线相连: – 处理器-主存总线:主要用于处理器和主存储器之间的通信 – 输入/输出总线:为输入/输出设备提供信息 处理器 主存 处理器-主存总线 总线适配器 输入/输出 总线 总线适配器 总线适配器 输入/输出 总线 输入/输出 总线

3、三总线结构 三总线结构是在双总线系统的基础上增加/O总线形成的。 在DMA方式中,外设与存储器间直接交换数据而不经过CPU, 从而减轻了CPU对数据输入输出的控制,而“通道”方式进一步提 高了CPU的效率。通道实际上是一台具有特殊功能的处理器,又称 为IOP(/O处理器),它分担了一部分CPU的功能,以实现对外设的统 一管理及外设与主存之间的数据传送。显然,由于增加了IOP,使 整个系统的效率大大提高。然而这是以增加更多的硬件代价换来的 系统总线 cpu二内存 内有总线 三总线结构是在双总线 71/0总线 结构的基础上增加1/0 总线形成的 图6.3三总线结构 0接口

三总线结构是在双总线系统的基础上增加I/O总线形成的。 在DMA方式中,外设与存储器间直接交换数据而不经过CPU, 从而减轻了CPU对数据输入输出的控制,而“通道”方式进一步提 高了CPU的效率。通道实际上是一台具有特殊功能的处理器,又称 为IOP(I/O处理器),它分担了一部分CPU的功能,以实现对外设的统 一管理及外设与主存之间的数据传送。显然,由于增加了IOP,使 整个系统的效率大大提高。然而这是以增加更多的硬件代价换来的 。 3、三总线结构

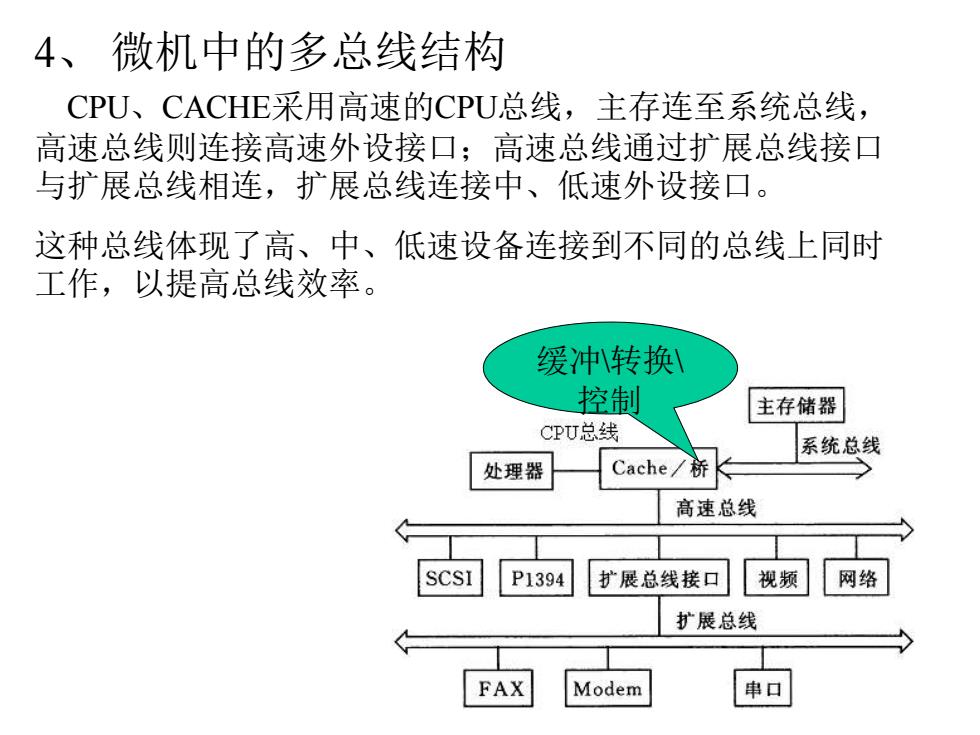

4、微机中的多总线结构 CPU、CACHE采用高速的CPU总线,主存连至系统总线, 高速总线则连接高速外设接口;高速总线通过扩展总线接口 与扩展总线相连,扩展总线连接中、低速外设接口。 这种总线体现了高、中、低速设备连接到不同的总线上同时 工作,以提高总线效率。 缓冲转换 控制 主存储器 CPU总线 系统总线 处理器 Cache/桥 高速总线 SCSI P1394 扩展总线接口 视频 网络 扩展总线 FAX Modem 串口

4、 微机中的多总线结构 CPU、CACHE采用高速的CPU总线,主存连至系统总线, 高速总线则连接高速外设接口;高速总线通过扩展总线接口 与扩展总线相连,扩展总线连接中、低速外设接口。 这种总线体现了高、中、低速设备连接到不同的总线上同时 工作,以提高总线效率。 缓冲\转换\ 控制

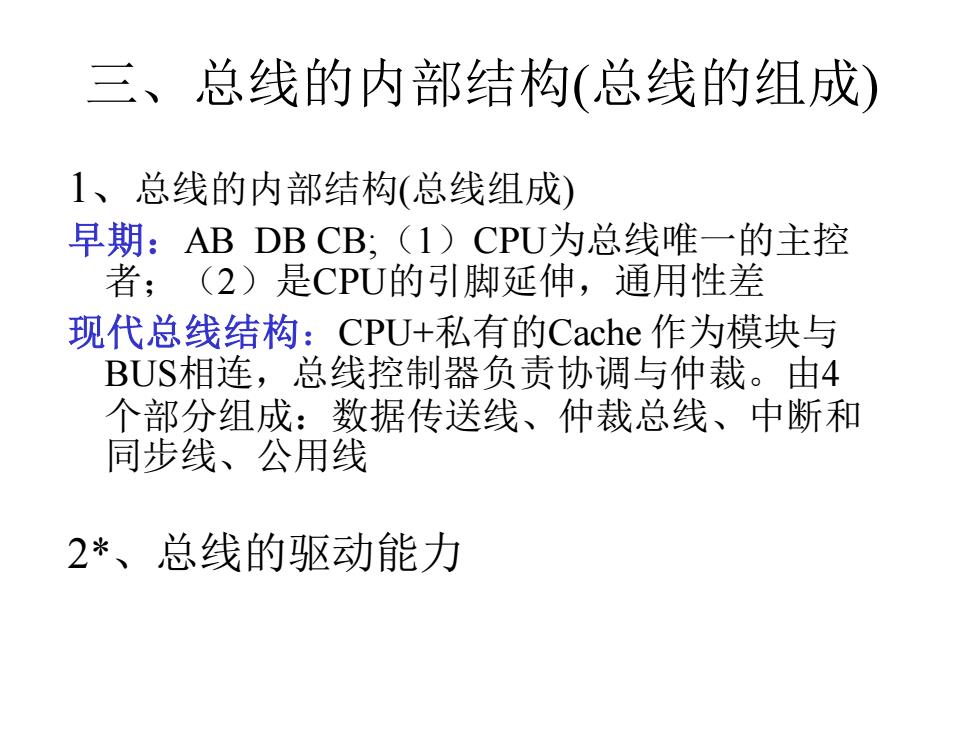

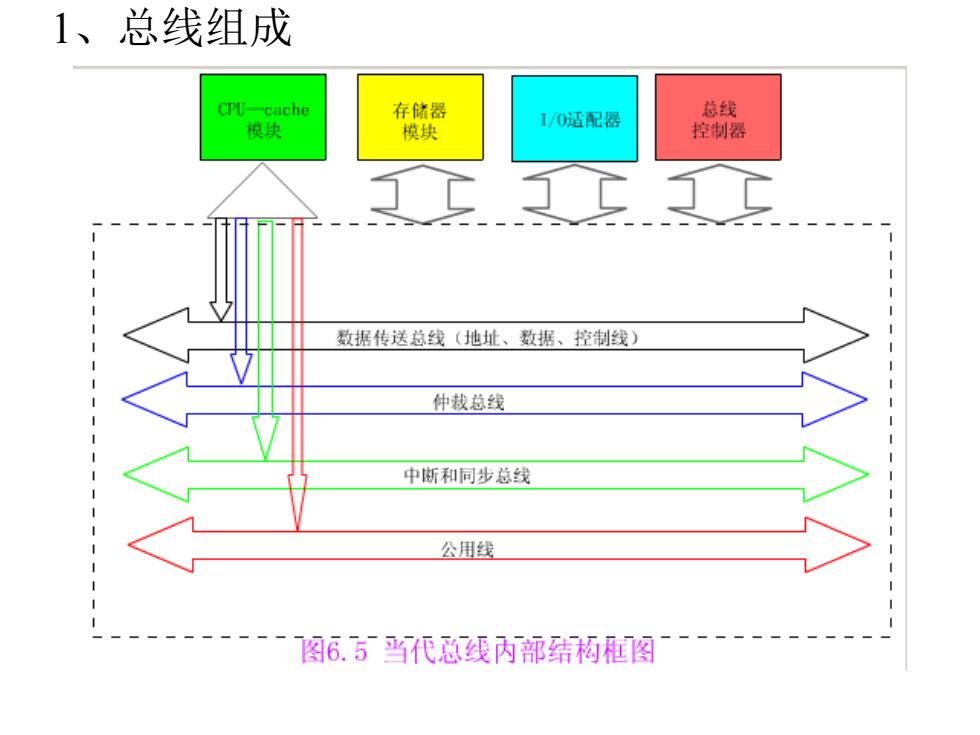

三、总线的内部结构(总线的组成) 1、总线的内部结构(总线组成) 早期:AB DB CB;(1)CPU为总线唯一的主控 者;(2)是CPU的引脚延伸,通用性差 现代总线结构:CPU+私有的Cache作为模块与 BUS相连,总线控制器负责协调与仲裁。由4 个部分组成:数据传送线、仲裁总线、中断和 同步线、公用线 2*、总线的驱动能力

三、总线的内部结构(总线的组成) 1、总线的内部结构(总线组成) 早期:AB DB CB;(1)CPU为总线唯一的主控 者;(2)是CPU的引脚延伸,通用性差 现代总线结构:CPU+私有的Cache 作为模块与 BUS相连,总线控制器负责协调与仲裁。由4 个部分组成:数据传送线、仲裁总线、中断和 同步线、公用线 2*、总线的驱动能力

1、总线组成 CPU-cache 存储器 总线 模块 模块 I/O适配器 控制器 数据传送总线(地址、数据、控制线) 仲裁总线 中断和同步总线 公用线 图6.5当代总线内部结构框图

1、总线组成