第一章 DE2开发组件 DE2开发组件包含全部组件用于DE2开发板与在Windows.上运行的软件。 1.1组件目录 图1.1是DE2开发包的照片 AUERA DE2 图1.1DE2开发包 DE2开发包中包含以下组件: ●DE2开发板, ●用于FPGA配置和调试的USB连接线, ●一张CD光盘包括DE2说明文件和相关材料,用户手册、控制面板的作用、参考设计和 范例、设备数据表、指南、一套试验练习题, ● CD里面有Altera's QuartusⅡ网络版,NiosⅡ嵌入式设计评估版软件, ●六个硅胶支撑柱,一些O口的插针, 。开发板的塑料包装, ●9V直流电源。 1.2DE2开发板的套件 按照下面的步骤来安装: 1、如图1.2,在DE2开发板的六个铜脚上套上硅胶套; 2、塑料的封面为DE2开发板提供了特别的保护,这层塑料是用螺丝安装在板的表面的

第一章 DE2 开发组件 DE2 开发组件包含全部组件用于DE2 开发板与在Windows上运行的软件。 1.1 组件目录 图1.1 是DE2开发包的照片 图1.1 DE2开发包 DE2开发包中包含以下组件: z DE2开发板, z 用于FPGA配置和调试的USB 连接线, z 一张CD光盘包括DE2 说明文件和相关材料,用户手册、控制面板的作用、参考设计和 范例、设备数据表、指南、一套试验练习题, z CD里面有Altera’s Quartus II网络版,Nios II嵌入式设计评估版软件, z 六个硅胶支撑柱,一些I\O口的插针, z 开发板的塑料包装, z 9V直流电源。 1.2 DE2开发板的套件 按照下面的步骤来安装: 1、 如图1.2,在DE2开发板的六个铜脚上套上硅胶套; 2、 塑料的封面为DE2开发板提供了特别的保护,这层塑料是用螺丝安装在板的表面的

图1.2DE2开发板的支撑脚 1.3帮助 如果你遇到问题可以从下面的地址中获得帮助: ·Altera Corporation 101 Innovation Drive San Jose,California,95134 USA E-mail:university@altera.com .Terasic Technologies No.356,Sec.1,Fusing E.Rd. Jhubei City,HsinChu County,Taiwan,302 E-mail:support@terasic.com Web:DE2.terasic.com ·Arches Computing Unit 708-222 Spadina Ave Toronto,Ontario,Canada M5T3A2 E-mail:DE2support@archescomputing.com Web:DE2.archescomputing.com 你也可以从一个专门为DE2开发板建立的BBS上面获得帮助,BBS是一个DE2板的知识库, 这里有使用者提的问题,分享设计例子等资源。 BBS地址:http:www.terasic.com/english/discuss.htm 第二章 Altera DE2开发板 这一章将展示DE2开发板的细部特写,介绍它的设计特点

图1.2 DE2开发板的支撑脚 1.3帮助 如果你遇到问题可以从下面的地址中获得帮助: • Altera Corporation 101 Innovation Drive San Jose, California, 95134 USA E-mail: university@altera.com • Terasic Technologies No. 356, Sec. 1, Fusing E. Rd. Jhubei City, HsinChu County, Taiwan, 302 E-mail: support@terasic.com Web: DE2.terasic.com • Arches Computing Unit 708-222 Spadina Ave Toronto, Ontario, Canada M5T3A2 E-mail: DE2support@archescomputing.com Web: DE2.archescomputing.com 你也可以从一个专门为DE2开发板建立的BBS上面获得帮助,BBS是一个DE2板的知识库, 这里有使用者提的问题,分享设计例子等资源。 BBS地址:http://www.terasic.com/english/discuss.htm 第二章 Altera DE2 开发板 这一章将展示DE2开发板的细部特写,介绍它的设计特点

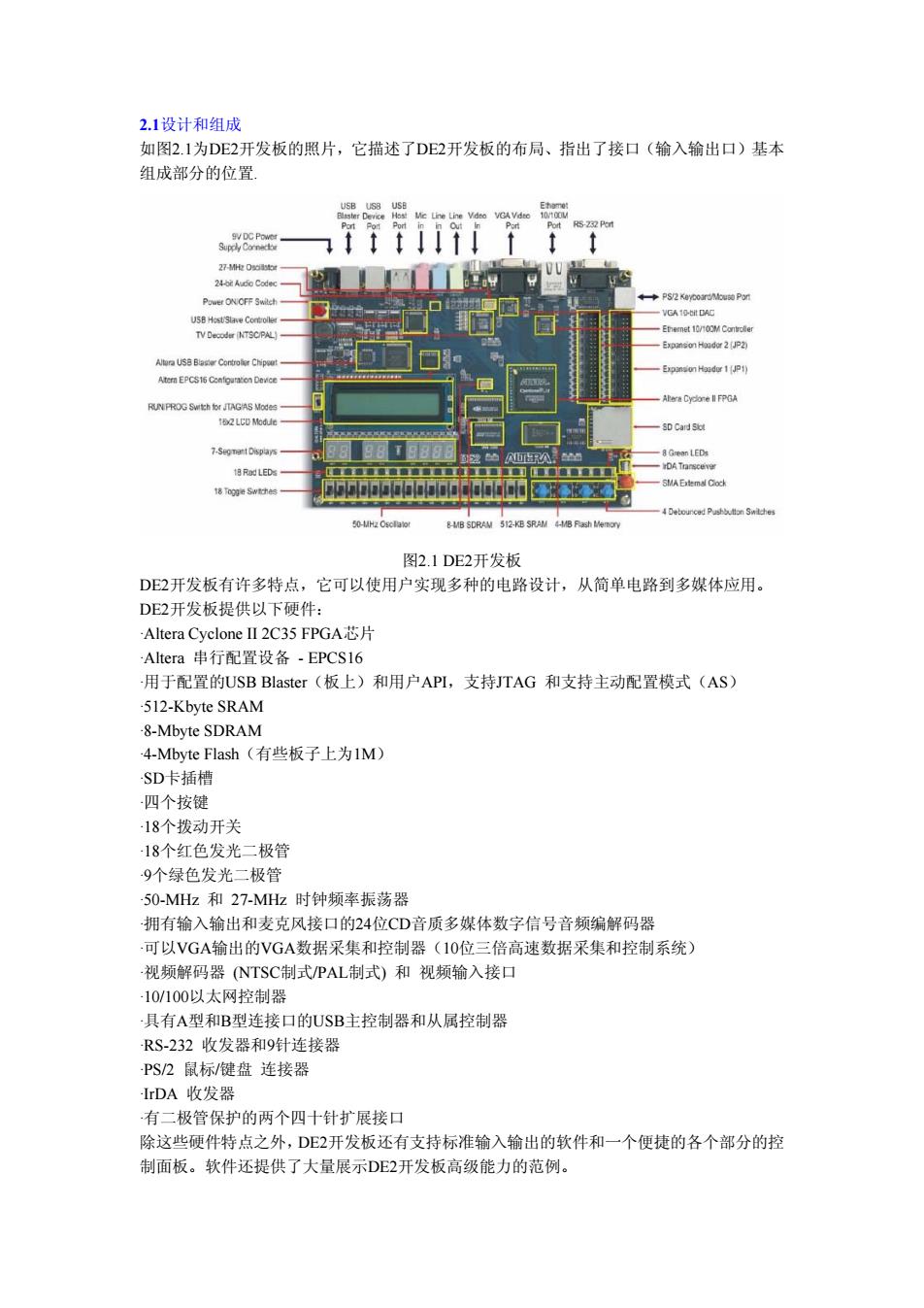

2.1设计和组成 如图2.1为DE2开发板的照片,它描述了DE2开发板的布局、指出了接口(输入输出口)基本 组成部分的位置 USB US8 甲/DC Pow Supoly Comnedo 27MHe0型 24b Audio Codec- Power ONOFF Switch ◆PS2K0yo0 r/Mous P3r USB HostSlave Controller -VC队10-bit DAC TV Decoder iNTSC/PAL) -Emeret 10/103M Contoler Expansion Hoador 2 (JP2) -Alera Cydlore ll FPGA 162LCD Module SD Card Siot 7-Segmant Displays -8 Grean LEDs tBRa时LEDg 18 Togge Swtches 50-MHz Osclaor 8-MB SDRAM 512-KB SRAM 4-MB Fash Memory 图2.1DE2开发板 DE2开发板有许多特点,它可以使用户实现多种的电路设计,从简单电路到多媒体应用。 DE2开发板提供以下硬件: Altera CycloneⅡ2C35FPGA芯片 Altera串行配置设备-EPCS16 用于配置的USB Blaster(板上)和用户API,支持TAG和支持主动配置模式(AS) 512-Kbyte SRAM 8-Mbyte SDRAM 4-Mbyte Flash(有些板子上为1M) SD卡插槽 四个按键 18个拨动开关 18个红色发光二极管 9个绿色发光二极管 50-MHz和27-MHz时钟频率振荡器 拥有输入输出和麦克风接口的24位CD音质多媒体数字信号音频编解码器 可以VGA输出的VGA数据采集和控制器(10位三倍高速数据采集和控制系统) 视频解码器NTSC制式PAL制式)和视频输入接口 -10/100以太网控制器 ·具有A型和B型连接口的USB主控制器和从属控制器 RS-232收发器和9针连接器 PS/2鼠标/键盘连接器 IrDA收发器 有二极管保护的两个四十针扩展接口 除这些硬件特点之外,DE2开发板还有支持标准输入输出的软件和一个便捷的各个部分的控 制面板。软件还提供了大量展示DE2开发板高级能力的范例

2.1设计和组成 如图2.1为DE2开发板的照片,它描述了DE2开发板的布局、指出了接口(输入输出口)基本 组成部分的位置. 图2.1 DE2开发板 DE2开发板有许多特点,它可以使用户实现多种的电路设计,从简单电路到多媒体应用。 DE2开发板提供以下硬件: ·Altera Cyclone II 2C35 FPGA芯片 ·Altera 串行配置设备 - EPCS16 ·用于配置的USB Blaster(板上)和用户API,支持JTAG 和支持主动配置模式(AS) ·512-Kbyte SRAM ·8-Mbyte SDRAM ·4-Mbyte Flash(有些板子上为1M) ·SD卡插槽 ·四个按键 ·18个拨动开关 ·18个红色发光二极管 ·9个绿色发光二极管 ·50-MHz 和 27-MHz 时钟频率振荡器 ·拥有输入输出和麦克风接口的24位CD音质多媒体数字信号音频编解码器 ·可以VGA输出的VGA数据采集和控制器(10位三倍高速数据采集和控制系统) ·视频解码器 (NTSC制式/PAL制式) 和 视频输入接口 ·10/100以太网控制器 ·具有A型和B型连接口的USB主控制器和从属控制器 ·RS-232 收发器和9针连接器 ·PS/2 鼠标/键盘 连接器 ·IrDA 收发器 ·有二极管保护的两个四十针扩展接口 除这些硬件特点之外,DE2开发板还有支持标准输入输出的软件和一个便捷的各个部分的控 制面板。软件还提供了大量展示DE2开发板高级能力的范例

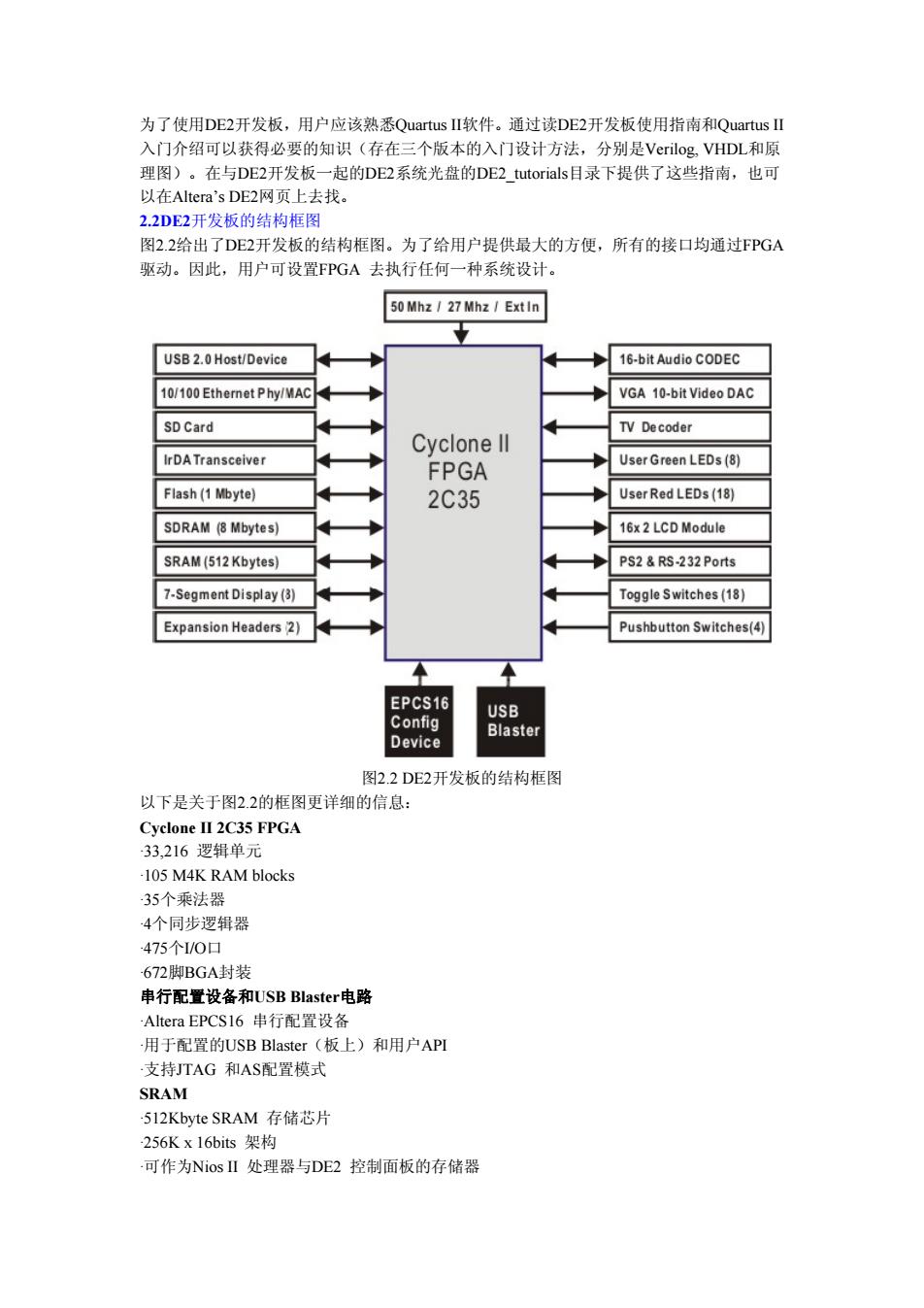

为了使用DE2开发板,用户应该熟悉Quartus IⅡ软件。通过读DE2开发板使用指南和QuartusⅡ 入门介绍可以获得必要的知识(存在三个版本的入门设计方法,分别是Verilog,VHDL和原 理图)。在与DE2开发板一起的DE2系统光盘的DE2 tutorials目录下提供了这些指南,也可 以在Altera'sDE2网页上去找。 2.2DE2开发板的结构框图 图2.2给出了DE2开发板的结构框图。为了给用户提供最大的方便,所有的接口均通过FPGA 驱动。因此,用户可设置FPGA去执行任何一种系统设计。 50 Mhz 27 Mhz Ext In USB 2.0 Host/Device 16-bit Audio CODEC 10/100 Ethernet Phy/MAC VGA 10-bit Video DAC SDCard TV Decoder Cyclone ll IrDA Transceiver FPGA User Green LEDs(⑧) Flash(1 Mbyte) 2C35 User Red LEDs(18) SDRAM (8 Mbytes) 16x 2 LCD Module SRAM(512 Kbytes) PS2 RS-232 Ports 7-Segment Display(3) Toggle Switches(18) Expansion Headers 2) Pushbutton Switches(4) EPCS16 USB Config Device Blaster 图2.2DE2开发板的结构框图 以下是关于图22的框图更详细的信息: CycloneⅡ2C35FPGA 33,216逻辑单元 -105 M4K RAM blocks 35个乘法器 4个同步逻辑器 475个I/0▣ 672脚BGA封装 串行配置设备和USB Blaster电路 Altera EPCS16串行配置设备 用于配置的JSB Blaster(板上)和用户API 支持TAG和AS配置模式 SRAM ·512 Kbyte SRAM存储芯片 256Kx16bits架构 可作为NiosⅡ处理器与DE2控制面板的存储器

为了使用DE2开发板,用户应该熟悉Quartus II软件。通过读DE2开发板使用指南和Quartus II 入门介绍可以获得必要的知识(存在三个版本的入门设计方法,分别是Verilog, VHDL和原 理图)。在与DE2开发板一起的DE2系统光盘的DE2_tutorials目录下提供了这些指南,也可 以在Altera’s DE2网页上去找。 2.2DE2开发板的结构框图 图2.2给出了DE2开发板的结构框图。为了给用户提供最大的方便,所有的接口均通过FPGA 驱动。因此,用户可设置FPGA 去执行任何一种系统设计。 图2.2 DE2开发板的结构框图 以下是关于图2.2的框图更详细的信息: Cyclone II 2C35 FPGA ·33,216 逻辑单元 ·105 M4K RAM blocks ·35个乘法器 ·4个同步逻辑器 ·475个I/O口 ·672脚BGA封装 串行配置设备和USB Blaster电路 ·Altera EPCS16 串行配置设备 ·用于配置的USB Blaster(板上)和用户API ·支持JTAG 和AS配置模式 SRAM ·512Kbyte SRAM 存储芯片 ·256K x 16bits 架构 ·可作为Nios II 处理器与DE2 控制面板的存储器

SDRAM 8-Mbyte单数据传输率同步动态随机存储芯片 1Mx16 bits x4 banks构架 可作为NiosⅡ处理器与DE2控制面板的存储器 Flash memory 4-Mbyte或非门闪存(有些板为1 Mbyte) 8位数据总线 可作为NiosⅡ处理器与DE2控制面板的存储器 SD卡插槽(SD card socket) 提供SPI模式对SD卡的访问 可作为NiosⅡ处理器与DE2控制面板的存储器 按钮开关(Pushbutton switches) 4个按钮开关 施密特触发电路反跳 通常高电平,按下时产生低电平脉冲 拨动开关(Toggle switch) 18个拨动开关作为用户输入 由按下转为弹起时产生逻辑0:由弹起转为按下时产生逻辑1 晶振输入(Clock inputs) 50-MHz晶体振荡器 27-MHz晶体振荡器 SMS外部时钟输入 音频编码转换器(Audio CODEC) Wolfson WM8731224位音频编码转换器 串行输入,串行输出,麦克风输入插孔 采样频率:8-96KHz 适用于MP3播放器、录音机、个人数字助理(PDA)、智能电话(smart phone)等 视频输出(VGA output) ~采用ADV7123240MHz三10位高速视频数/模转换器(video DAC) 带有15脚高密度D形接口 支持100Hz刷新率时的高达1600x1200分辨率 可与CycloneⅡFPGA联合使用实现高性能TV编码器 NTFC/PAL TV解码电路NTFC/PAL TV decoder circuit) 采用ADV7181B多格式SDTV视频解码器 支持NTFC-M,J,4.43),PAL-(B/D/G/H/IMWN),SECAM制式 集成三个54MHz9位模/数转换器(ADC) 27MHz晶体振荡器输入作为时钟源 支持复合视频(CVBS)RCA接口输入 支持数字信号输出格式(8位16位):ITU-RBT。956 YCrCb4:2:2 output+HS,VS,和FIELD 适用:DVD录像机(DVD recorders),液晶电视(LCD TV),机顶盒(Set-top-boxes),数字电视 (Digital TV),带接口的数字设备 10/IO0Mb/s以太网控制器(Ethernet controller) 集成带有一个总处理器接口的MAC和PHY 支持100Base-T和10Base-T

SDRAM ·8-Mbyte 单数据传输率同步动态随机存储芯片 ·1M x 16bits x 4banks 构架 ·可作为Nios II 处理器与DE2 控制面板的存储器 Flash memory ·4-Mbyte 或非门闪存(有些板为1 Mbyte) ·8 位数据总线 ·可作为Nios II 处理器与DE2 控制面板的存储器 SD 卡插槽(SD card socket) ·提供SPI 模式对SD卡的访问 ·可作为Nios II 处理器与DE2 控制面板的存储器 按钮开关(Pushbutton switches) ·4 个按钮开关 ·施密特触发电路反跳 ·通常高电平;按下时产生低电平脉冲 拨动开关(Toggle switch) ·18 个拨动开关作为用户输入 ·由按下转为弹起时产生逻辑0;由弹起转为按下时产生逻辑1 晶振输入(Clock inputs) ·50-MHz 晶体振荡器 ·27-MHz 晶体振荡器 ·SMS 外部时钟输入 音频编码转换器(Audio CODEC) ·Wolfson WM87312 24 位音频编码转换器 ·串行输入,串行输出,麦克风输入插孔 ·采样频率:8-96KHz ·适用于MP3 播放器、录音机、个人数字助理(PDA)、智能电话(smart phone)等 视频输出(VGA output) ·采用ADV7123 240MHz 三10 位高速视频数/模转换器(video DAC) ·带有15 脚高密度D 形接口 ·支持100Hz 刷新率时的高达1600 x 1200 分辨率 ·可与Cyclone II FPGA 联合使用实现高性能TV 编码器 NTFC/PAL TV 解码电路(NTFC/PAL TV decoder circuit) ·采用ADV7181B 多格式SDTV 视频解码器 ·支持NTFC-(M,J,4.43),PAL-(B/D/G/H/I/M/N),SECAM制式 ·集成三个54MHz 9 位模/数转换器(ADC) ·27MHz 晶体振荡器输入作为时钟源 ·支持复合视频(CVBS)RCA 接口输入 ·支持数字信号输出格式(8 位/16 位):ITU-R BT。956YCrCb 4:2:2 output+HS,VS,和FIELD ·适用:DVD 录像机(DVD recorders),液晶电视(LCD TV),机顶盒(Set-top-boxes),数字电视 (Digital TV),带接口的数字设备 10/100Mb/s 以太网控制器(Ethernet controller) ·集成带有一个总处理器接口的MAC 和PHY ·支持100Base-T 和10Base-T