5.42附加全局约束 254 543册加能口的卖 544 附加分组约束和时序约束 257 5.4.5 附加专用约束. .261 5.5引脚与区域约束编辑器 -PACE 262 5.5.1PACE的用户界面 26 55)册加区约 26 附加V0引脚约来 267 约束文 2 5.6.1 约束文件的概念 .268 562UCF、NCF文件的基本语法规则 269 57小结 271 5.8问题与思考 271 第6章辅助设计工具 273 6.1 时序分析器 Timing Analyzer 273 6.1.1时序分析器的用户界面」 .274 612时序分折器的作用及设计流程 275 6.13基本时序路径 276 14时序分析器的使用方法 62 布局规划器 6.2.1 布局规划器的用户界面 286 622布局规划器的特点及作用. 288 62.3布局规划设计流程 289 624设计示例 292 63 FPGA底层 -FPGA Edito 297 6.3.1 FPGA底层编辑器的用户接 297 632FPGA底层编辑器的作用 298 633FPGA底层编辑器给入输出文件 300 6.3.4FPGA底层编辑器的工作流程 30 635 使用FPGA底层编样器的预备知识 3 6.3. 计示例 30 6.4小结 0 6.5问题与思考 308 第7章XPower、iMPACT和ChipScope Pro. 309 7 300 述 7.12 XPower的用户界面 398 7.1.3用XPower分析功花.. .313

4 5.4.2 附加全局约束............................................................................................................254 5.4.3 附加端口约束............................................................................................................256 5.4.4 附加分组约束和时序约束........................................................................................257 5.4.5 附加专用约束............................................................................................................261 5.5 引脚与区域约束编辑器──PACE..................................................................................262 5.5.1 PACE 的用户界面.....................................................................................................263 5.5.2 附加区域约束............................................................................................................266 5.5.3 附加 I/O 引脚约束 ....................................................................................................267 5.6 约束文件 ...........................................................................................................................268 5.6.1 约束文件的概念........................................................................................................268 5.6.2 UCF、NCF 文件的基本语法规则 ...........................................................................269 5.7 小结 ...................................................................................................................................271 5.8 问题与思考........................................................................................................................271 第 6 章 辅助设计工具.........................................................................................................273 6.1 时序分析器──Timing Analyzer.....................................................................................273 6.1.1 时序分析器的用户界面............................................................................................274 6.1.2 时序分析器的作用及设计流程................................................................................275 6.1.3 基本时序路径............................................................................................................276 6.1.4 时序分析器的使用方法............................................................................................282 6.2 布局规划器──Floorplanner...........................................................................................286 6.2.1 布局规划器的用户界面............................................................................................286 6.2.2 布局规划器的特点及作用........................................................................................288 6.2.3 布局规划设计流程....................................................................................................289 6.2.4 设计示例....................................................................................................................292 6.3 FPGA 底层编辑器──FPGA Editor................................................................................297 6.3.1 FPGA 底层编辑器的用户接口.................................................................................297 6.3.2 FPGA 底层编辑器的作用 ........................................................................................298 6.3.3 FPGA 底层编辑器输入输出文件.............................................................................300 6.3.4 FPGA 底层编辑器的工作流程.................................................................................301 6.3.5 使用 FPGA 底层编辑器的预备知识........................................................................301 6.3.6 设计示例....................................................................................................................303 6.4 小结 ...................................................................................................................................308 6.5 问题与思考........................................................................................................................308 第7 章 XPower、iMPACT 和ChipScope Pro................................................................309 7.1 XPower ..............................................................................................................................309 7.1.1 XPower 综述 .............................................................................................................309 7.1.2 XPower 的用户界面..................................................................................................310 7.1.3 用 XPower 分析功耗.................................................................................................313

7.2 iMPACT. 316 7.2 iMPACT综述 36 7.22 iMPACT的用户界面 3 7.2.3用MPACT下载配置文件 7.3 ChipScope Pro.. 328 7.31 ChipScopePro综遂 328 7.32 ChipScope Pro Core Inserte 7.33 ChipScope Pro Analyzer. 358 74小 341 7.5问题与思考 .341 第8章模块化与增量式设计方法 343 8.1模块化设计方法的基本概念」 82模块化设计方法的设计流程 821 M dular Design的设计输入与综合步我 8.22 Modular Design的实现步骤. 346 83模块化设计方法的注意事项 350 8.3.1 Modular Design的应用场合 350 832 Modular design的设计放能 35 833 Modular Des1gn的目录管理 8.3.4 Modular Design的常用约来 32 8.3.5 Modular Design的报告查看」 353 836使用X下1OW白动海行模块化设计 353 8.4模块化设计方法的设计实例 355 85 增量式设计方法的本概念 8.6 增量设计方法的设计流程 36 8.6.1 增量综合….. 367 8.62 增量实现 369 8.7增量设计方法的设计实例 372 88小结 379 8.9问题与思考 381 第9章 融会贯通 “运动计时表”设计 .383 9.1示例背景 .384 92多元混合设计输入方法 385 9.2.1新建工程“watch sc 385 9.2.2使用ECS绘制“cnt60”和“outs3”模块原理图 923 使用Core Genera r生成“tenths"TP 9.2.4 使用StateCAD设计“stmachv” 班 状态材 9.2.5 使用Architecture Wizard生成时钟管理模块“dcml” 403

5 7.2 iMPACT.............................................................................................................................316 7.2.1 iMPACT 综述............................................................................................................316 7.2.2 iMPACT 的用户界面................................................................................................317 7.2.3 用 iMPACT 下载配置文件.......................................................................................320 7.3 ChipScope Pro ...................................................................................................................328 7.3.1 ChipScope Pro 综述...................................................................................................328 7.3.2 ChipScope Pro Core Inserter......................................................................................330 7.3.3 ChipScope Pro Analyzer............................................................................................336 7.4 小结 ...................................................................................................................................341 7.5 问题与思考........................................................................................................................341 第 8 章 模块化与增量式设计方法 ..................................................................................343 8.1 模块化设计方法的基本概念............................................................................................343 8.2 模块化设计方法的设计流程............................................................................................344 8.2.1 Modular Design 的设计输入与综合步骤.................................................................345 8.2.2 Modular Design 的实现步骤.....................................................................................346 8.3 模块化设计方法的注意事项............................................................................................350 8.3.1 Modular Design 的应用场合.....................................................................................350 8.3.2 Modular Design 的设计效能.....................................................................................351 8.3.3 Modular Design 的目录管理.....................................................................................352 8.3.4 Modular Design 的常用约束.....................................................................................352 8.3.5 Modular Design 的报告查看.....................................................................................353 8.3.6 使用 XFLOW 自动进行模块化设计........................................................................353 8.4 模块化设计方法的设计实例............................................................................................355 8.5 增量式设计方法的基本概念............................................................................................364 8.6 增量设计方法的设计流程................................................................................................366 8.6.1 增量综合....................................................................................................................367 8.6.2 增量实现....................................................................................................................369 8.7 增量设计方法的设计实例................................................................................................372 8.8 小结 ...................................................................................................................................379 8.9 问题与思考........................................................................................................................381 第 9 章 融会贯通──“运动计时表”设计................................................................383 9.1 示例背景 ...........................................................................................................................384 9.2 多元混合设计输入方法....................................................................................................385 9.2.1 新建工程“watch_sc” ...............................................................................................385 9.2.2 使用 ECS 绘制“cnt60”和“outs3”模块原理图.................................................386 9.2.3 使用 Core Generator 生成“tenths”IP 核.................................................................392 9.2.4 使用 StateCAD 设计“stmach_v”状态机..............................................................395 9.2.5 使用 Architecture Wizard 生成时钟管理模块“dcm1”...........................................403

9.2.6使用语言模板设计“hex2led”和“decode”的HDL源代码. .405 9.2.7使用ECS设计顶层原理图 93 测试激励与行为级功能仿真 9.3.1使用HDL Bencher生成测试激励 .-..410 9.32调用ModelSim进行行为级功能仿真. 412 9.4 Synplit6Pro和XST综合方法. 413 9.41使用XST综合整个设计 413 943 使用 Synplify P0的特色工具分析、凭化设计 95设计用户约束文件与实现结果的分析 9.5.1使用Constraints Editor设计UCF文件. .422 952使用PACE设计UCF .425 9.53实现步骤与实现结果分析 427 9.6使用ModelSim进行布线后仿其 432 使用iMPACT配置FPGA/CPLI 433 9.8小结 .438 9.9问题与思考 438 第10章1SE实战 -℃接口设计 439 101gFY.9p200 实哈开发系统简介 420 10.2℃总线简介 102.1 ℃总线上的数据传输 44 10.2.2 ℃总钱寻址. .443 1023时钟同步与仲裁 .445 10242℃协议的扩展 446 1032C总线应用实 AT24C系列EEPROM. 446 0.31 AT24C02概述 10.32 写操竹 448 10.3.3读操作 448 10.3.4AT24C在1C卡中的应用简介 449 10.4C总线控制器设计详解 A50 10.4.1P℃总线控制器总体描述 10.4.2 C 口设计 452 10.4.3℃接口设计 .4 10.4.4混合仿真验证 469 10.4.5上板调试 478 105小结 .478 10.6问题与思考 478

6 9.2.6 使用语言模板设计“hex2led”和“decode”的 HDL 源代码..............................405 9.2.7 使用 ECS 设计顶层原理图 ......................................................................................408 9.3 测试激励与行为级功能仿真............................................................................................409 9.3.1 使用 HDL Bencher 生成测试激励 ...........................................................................410 9.3.2 调用 ModelSim 进行行为级功能仿真.....................................................................412 9.4 Synplify Pro 和 XST 综合方法.........................................................................................413 9.4.1 使用 XST 综合整个设计..........................................................................................413 9.4.2 使用 Synplify Pro 的特色工具分析、优化设计......................................................415 9.5 设计用户约束文件与实现结果的分析............................................................................421 9.5.1 使用 Constraints Editor 设计 UCF 文件...................................................................422 9.5.2 使用 PACE 设计 UCF...............................................................................................425 9.5.3 实现步骤与实现结果分析........................................................................................427 9.6 使用 ModelSim 进行布线后仿真.....................................................................................432 9.7 使用 iMPACT 配置 FPGA/CPLD.....................................................................................433 9.8 小结 ...................................................................................................................................438 9.9 问题与思考........................................................................................................................438 第 10 章 ISE 实战──I 2 C 接口设计................................................................................439 10.1 EFX-SP200──实验开发系统简介 ..............................................................................439 10.2 I2 C 总线简介...................................................................................................................440 10.2.1 I2 C 总线上的数据传输 ............................................................................................441 10.2.2 I2 C 总线寻址 ............................................................................................................443 10.2.3 时钟同步与仲裁.......................................................................................................445 10.2.4 I2 C 协议的扩展 ........................................................................................................446 10.3 I2 C 总线应用实例──AT24C 系列 EEPROM..............................................................446 10.3.1 AT24C02 概述..........................................................................................................447 10.3.2 写操作 ......................................................................................................................448 10.3.3 读操作 ......................................................................................................................448 10.3.4 AT24C 在 IC 卡中的应用简介................................................................................449 10.4 I2 C 总线控制器设计详解 ...............................................................................................450 10.4.1 I2 C 总线控制器总体描述 ........................................................................................451 10.4.2 µC 接口设计.............................................................................................................452 10.4.3 I2 C 接口设计 ............................................................................................................458 10.4.4 混合仿真验证...........................................................................................................469 10.4.5 上板调试...................................................................................................................478 10.5 小结 .................................................................................................................................478 10.6 问题与思考 .....................................................................................................................478

第1章ISE系统简介 本章在介绍FPGA/CPLD基本理论的基础上,引入FPGA/CPLD的完整设计流程,重点 介绍Xilinx的ISE集成开发环境的特点与ISE所集成的工具包的基本功能。 本章主要内容如下: ·FPGAACPLD简个 ISE系列 ·ISE6x支持的器件: 。1SE的4个软件系列: ·ISE的系统配置与安装: ·SE中集成的工具及其基本功能: 常用专有名词解释 1.1FPGA/CPLD简介 在数字化、信息化的时代,数字集成电路应用得非常广泛。随着微电子技术与工艺的发 展,数字集成电路从电子 、品体管、中小规模集成电路、超大规模集成电路(VLS1℃)逐 步发展到今天的专用集成电路(ASIC)。ASIC的出现降低了产品的生产成本,提高了系统 的可靠性,减少了产品的物理尺寸,推动了社会的数字化进程。但是ASIC因其设计周期 长,改版投资大,灵活性差等缺陷制约若它的应用范围。硬件工程师希望有一种更灵活的设 计方法,根据需要,在实验室就能设计、更改大规模数字逻辑,研制自己的ASIC并马上投 入使用。这就是可编程逻辑器件提 出的基本思想 可编程逻辑器件随着微电子制造工艺的发展取得了长足的进步。从早期的只能存储少 数据,完成简单逻辑功能的可编程只读存储器(PROM)、紫外线可擦除只读存储器 (EPROM)和电可擦除只读存储器(EEPROM),发展到能完成中大规模的数字逻辑功能的 可编程阵列逻辑(PAL)和通用阵列逻辑(GAL),今天己经发展成为可以完成超大规模的 复杂组合逻辑与时序逻辑的现场可编程逻辑器件(FPGA)和复杂可编程逻辑器件 (CPLD)。随着工艺技术的发展与市场需求 超大规模、高速、低功耗的新型 FPGA/CPLD 不断推陈出新。新一代的FPGA甚至集成了中央处理器(CPU)或数字处理器(DSP)内 核,在一片FPGA上进行软硬件协同设计,为实现片上可编程系统(SOPC:System On Programmable Chip)提供了强大的硬件支持

第1章 ISE 系统简介 本章在介绍 FPGA/CPLD 基本理论的基础上,引入 FPGA/CPLD 的完整设计流程,重点 介绍 Xilinx 的 ISE 集成开发环境的特点与 ISE 所集成的工具包的基本功能。 本章主要内容如下: • FPGA/CPLD 简介; • FPGA/CPLD 的设计流程; • ISE 系列产品的新特点; • ISE 6.x 支持的器件; • ISE 的 4 个软件系列; • ISE 的系统配置与安装; • ISE 中集成的工具及其基本功能; • 常用专有名词解释。 1.1 FPGA/CPLD 简介 在数字化、信息化的时代,数字集成电路应用得非常广泛。随着微电子技术与工艺的发 展,数字集成电路从电子管、晶体管、中小规模集成电路、超大规模集成电路(VLSIC)逐 步发展到今天的专用集成电路(ASIC)。ASIC 的出现降低了产品的生产成本,提高了系统 的可靠性,减少了产品的物理尺寸,推动了社会的数字化进程。但是 ASIC 因其设计周期 长,改版投资大,灵活性差等缺陷制约着它的应用范围。硬件工程师希望有一种更灵活的设 计方法,根据需要,在实验室就能设计、更改大规模数字逻辑,研制自己的 ASIC 并马上投 入使用。这就是可编程逻辑器件提出的基本思想。 可编程逻辑器件随着微电子制造工艺的发展取得了长足的进步。从早期的只能存储少量 数据,完成简单逻辑功能的可编程只读存储器(PROM)、紫外线可擦除只读存储器 (EPROM)和电可擦除只读存储器(EEPROM),发展到能完成中大规模的数字逻辑功能的 可编程阵列逻辑(PAL)和通用阵列逻辑(GAL),今天已经发展成为可以完成超大规模的 复 杂 组 合 逻 辑 与 时 序 逻 辑 的 现 场 可 编 程 逻 辑 器 件 (FPGA) 和 复 杂 可 编 程 逻 辑 器 件 (CPLD)。随着工艺技术的发展与市场需求,超大规模、高速、低功耗的新型 FPGA/CPLD 不断推陈出新。新一代的 FPGA 甚至集成了中央处理器(CPU)或数字处理器(DSP)内 核,在一片 FPGA 上进行软硬件协同设计,为实现片上可编程系统(SOPC:System On Programmable Chip)提供了强大的硬件支持

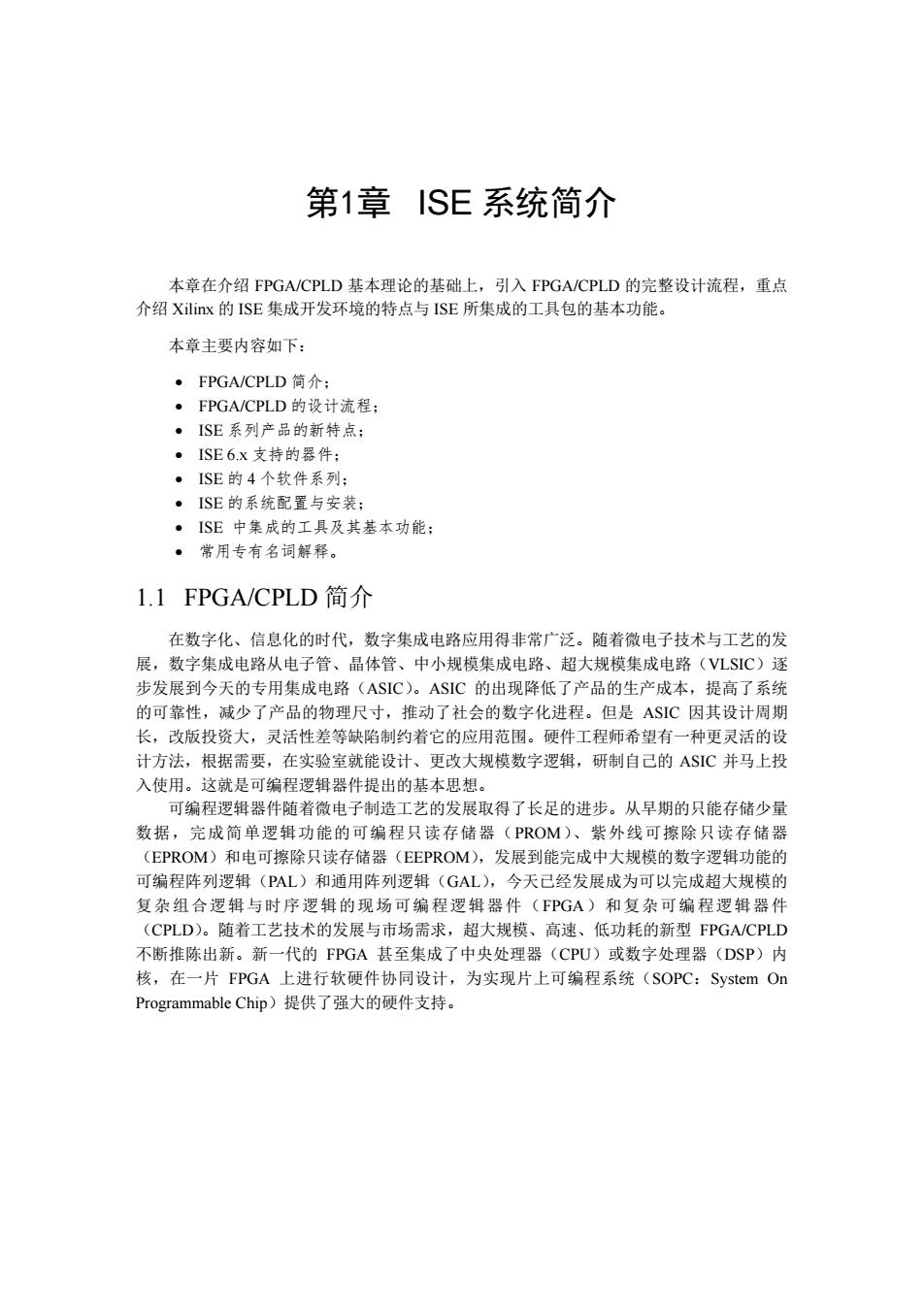

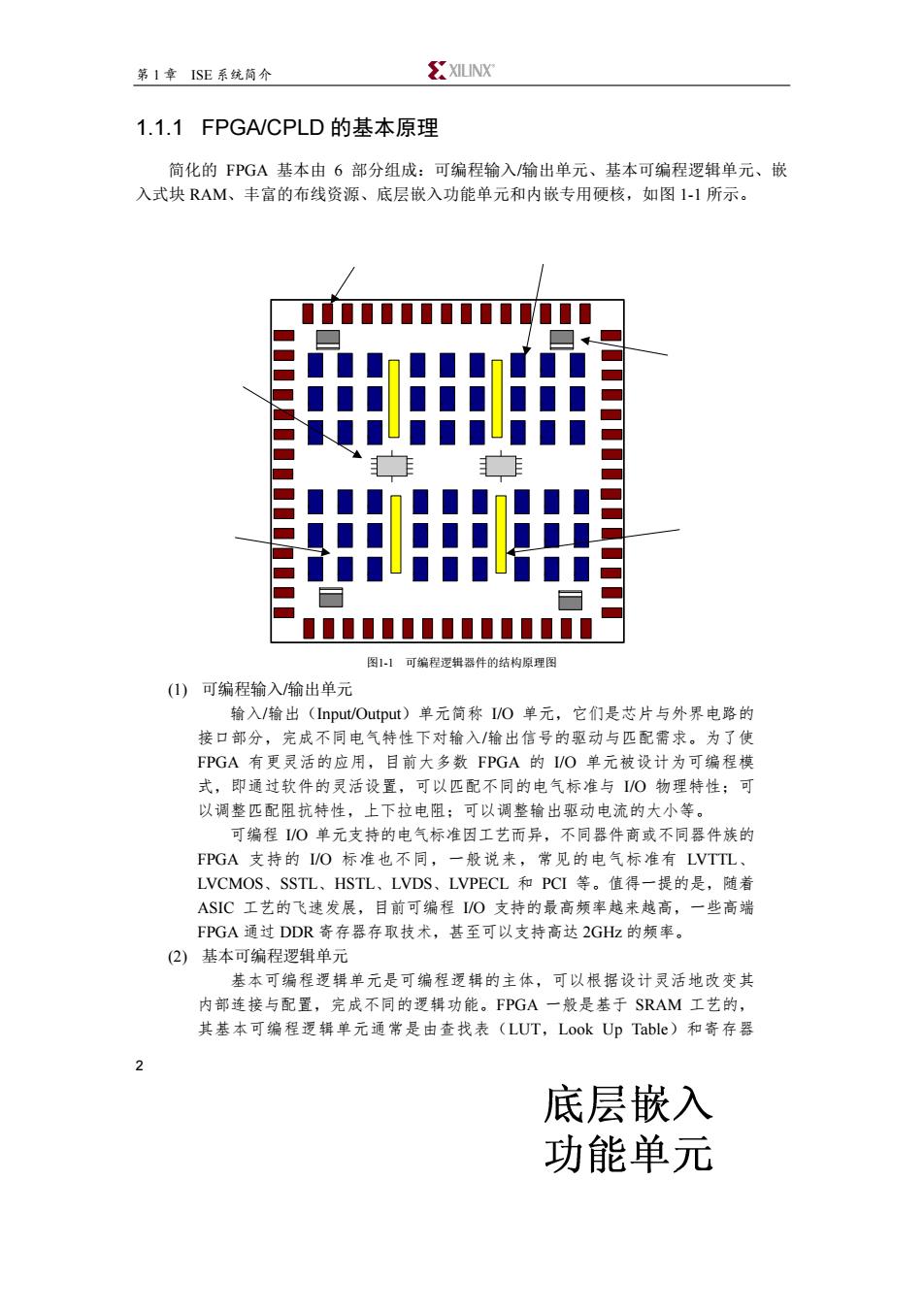

第1拿1SE系统简介 XILINX 1.1.1 FPGA/CPLD的基本原理 简化的FPGA基本由6部分组成:可编程输入输出单元、基本可编程逻辑单元、嵌 入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核,如图1-1所示。 ommm 图1】可编程证辑器作的结构图 ()可编程输入输出单元 输入/输出(nDut/Output)单元简称I/O单元,它们是芯片与外界电路的 接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配需求。为了使 FPGA有更灵活的应用,目前大多数FPGA的VO单元被设计为可编程模 即通过软件的灵活设置,可以匹配不同的电气标准与10物理特性:可 以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。 可编程/0单元支持的电气标准因工艺而异,不同器件商或不同器件族的 FPGA支持的IVO标准也不同,一般说来,常见的电气标准有LVTTL LVCMOS.SSTL.HSTL LVDS.LVPECL和PCI等。值得一提的是.随者 ASIC工艺的飞速发展,目前可编程V )支持的最高频率越来越高, 些高端 FPGA通 DDR寄存器存取技术,甚至可以支持高达2GHz的频率 (2)基本可编程逻辑单元 基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改支其 内部连接与配置,完成不同的逻辑功能。FPGA一般是基于SRAM工艺的: 其基本可编程逻辑单元通常是由查找表(LUT,Look Up Table)和寄存器 底层嵌入 功能单元

第 1 章 ISE 系统简介 2 1.1.1 FPGA/CPLD 的基本原理 简化的 FPGA 基本由 6 部分组成:可编程输入/输出单元、基本可编程逻辑单元、嵌 入式块 RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核,如图 1-1 所示。 图1-1 可编程逻辑器件的结构原理图 (1) 可编程输入/输出单元 输入/输出(Input/Output)单元简称 I/O 单元,它们是芯片与外界电路的 接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配需求。为了使 FPGA 有更灵活的应用,目前大多数 FPGA 的 I/O 单元被设计为可编程模 式,即通过软件的灵活设置,可以匹配不同的电气标准与 I/O 物理特性;可 以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。 可编程 I/O 单元支持的电气标准因工艺而异,不同器件商或不同器件族的 FPGA 支持的 I/O 标准也不同,一般说来,常见的电气标准有 LVTTL、 LVCMOS、SSTL、HSTL、LVDS、LVPECL 和 PCI 等。值得一提的是,随着 ASIC 工艺的飞速发展,目前可编程 I/O 支持的最高频率越来越高,一些高端 FPGA 通过 DDR 寄存器存取技术,甚至可以支持高达 2GHz 的频率。 (2) 基本可编程逻辑单元 基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其 内部连接与配置,完成不同的逻辑功能。FPGA 一般是基于 SRAM 工艺的, 其基本可编程逻辑单元通常是由查找表(LUT,Look Up Table)和寄存器